Известны транзисторные логические элементы с резервированием с резистором, включенным в их коллекторные цепи, в которых базы транзисторов разделены и через резисторы подключены ко входным зажимам.

Предложенный элемент отличается от известных тем, что в нем эмиттеры транзисторов подключены к раздельным шинам, которые через ключи подсоединены к общей шине.

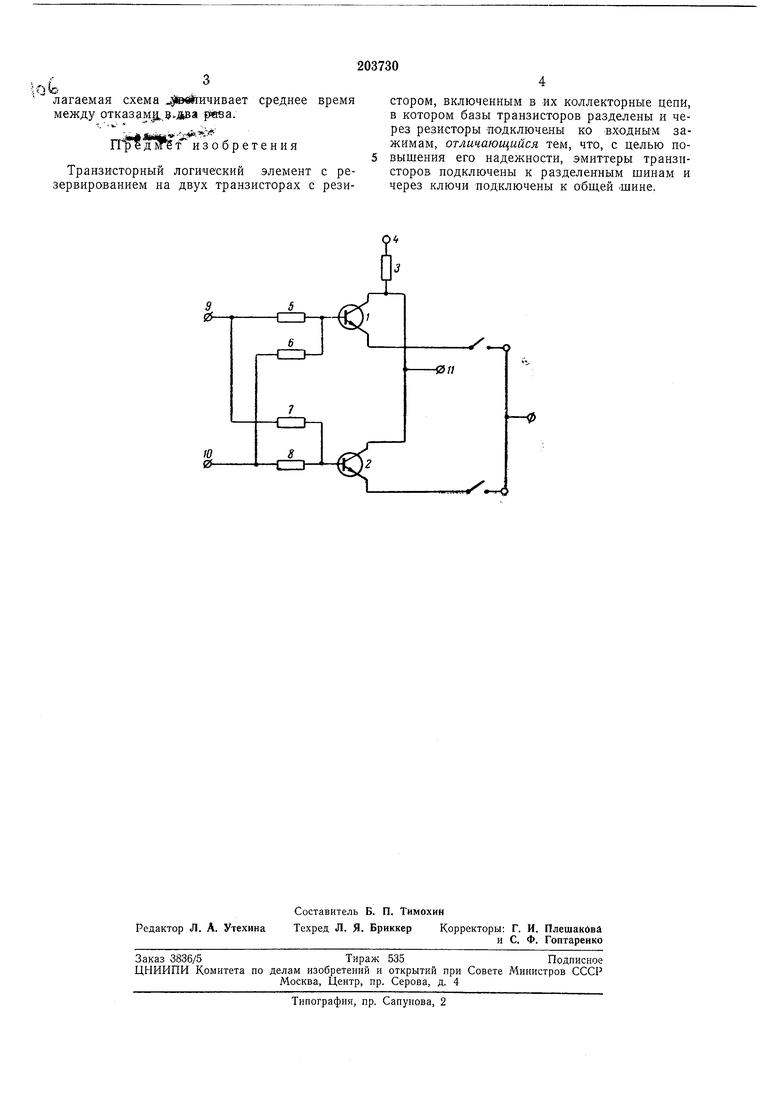

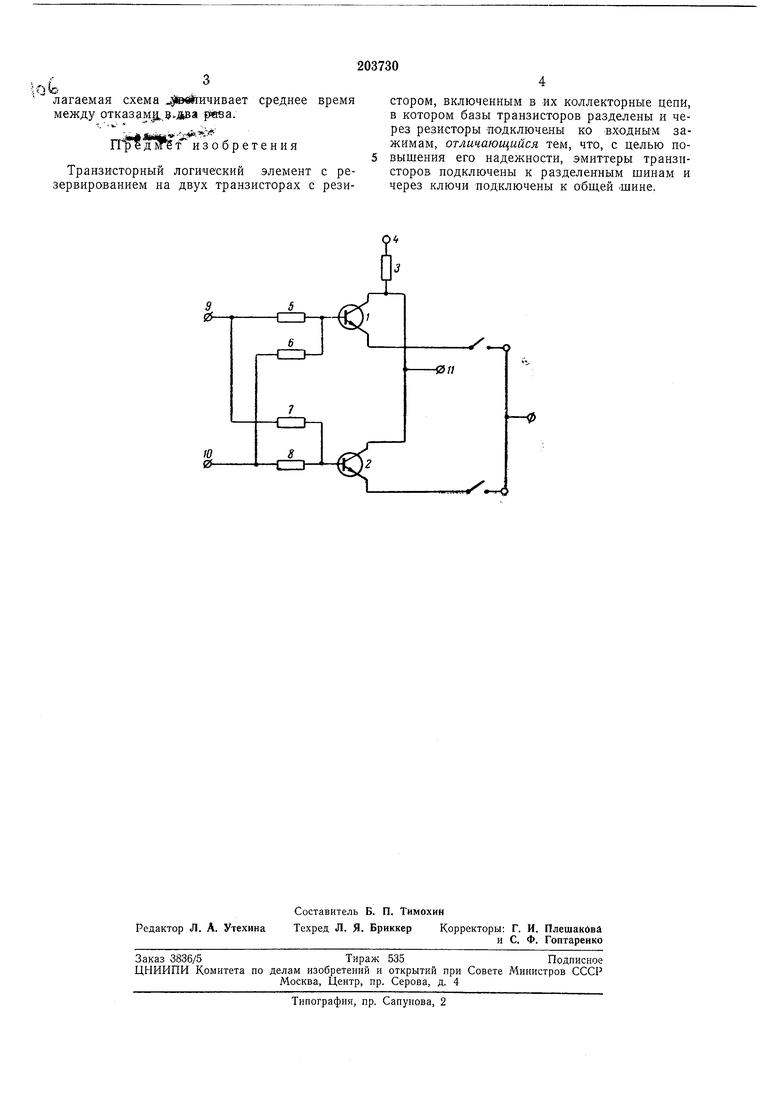

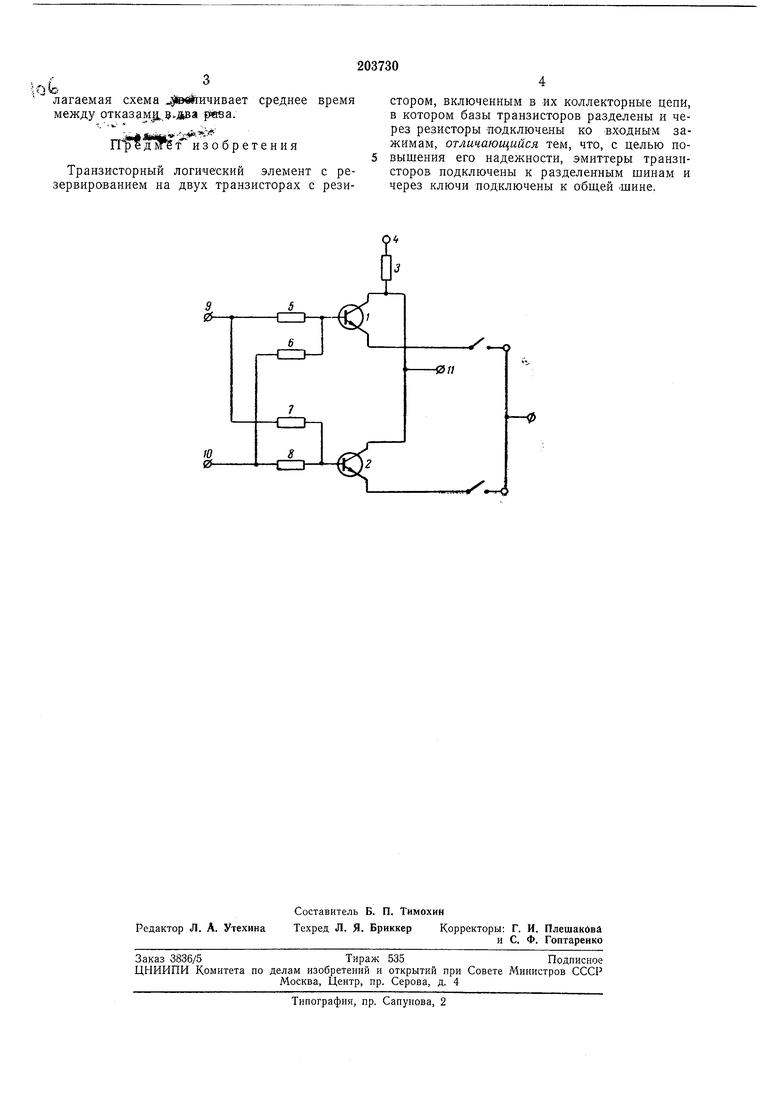

На чертеже показан предложенный элемент.

Он содержит два резервируемых транзистора } и 2, которые включены по схеме с общим SMHTiepOM и объединены коллекторами. Точка объединения подключена к выходной клемме схемы. Через резистор 3 коллекторы транзисторов подключены к источнику питающего напряжения 4. Входные клеммы схемы подключены к базам транзисторов через резисторы 5, 6, 7 и 8, причем к базе каждого транзистора подключено два резистора, на которых с учетом порога включения транзн торов, реализуется логическая функция . В коллекторе транзисторов получается инвертированный сигнал относите тьно базового.

соответствует высокий отрицательный потенциал, а уровню «О - потенциал, близкий к уровню земли. Базы резервируемых транзисторов / и 2

раздельны, благодаря этому схема нормально функционирует при любом единичном обрыве выводов транзисторов и при любом нарушении контакта одного из резисторов. При обрыве коллекторного вывода одного из транзисторов, получающийся диод база-эмиттер не подключен непосредственно в параллель с входным резистором оставшегося транзистора. Вследствие этого шунтирующее влияние диода оказывается резко ослабленным и

оставшийся транзистор обеспечивает нормальное функционирование схемы. Короткое замыкание база - эмиттер одного из транзисторов также не приводит к безусловному отказу. Эмиттеры пары резервируемых транзисторов раздельны. Подачей на любую из эмиттерных шин запирающего потенциала в процессе профилактики может быть определен отказ любого из двух транзисторов. Таким образом, при многоразовом использоваиии схемы получается значительный выигрыш в надежности. Вероятность безотказной работы предлагаемой схемы можно поддерживать на любом требуемом уровне. Даже в случае равновероятности отказов - j- лагаемая схема юШичивает среднее время между отказами §.даа pesa. irffffg t изобретения Транзисторный логический элемент с резервированием на двух транзисторах с резистером, включенным в их коллекторные цепи, в котором базы транзисторов разделены и через резисторы подключены ко входным зажимам, отличающийся тем, что, с целью новышения его надежности, эмиттеры транзисторов подключены к разделенным шинам и через ключи подключены к общей шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора непрерывных сигналов | 1982 |

|

SU1027826A1 |

| УСТРОЙСТВО КОНТРОЛЯ | 1996 |

|

RU2109300C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Устройство для управления мощным высоковольтным транзисторным ключом | 1987 |

|

SU1504751A2 |

| Автономная система электроснабжения | 1989 |

|

SU1617532A1 |

| Многоканальное резервированное аналоговое устройство | 1980 |

|

SU984089A2 |

| Устройство для управления мощным высоковольтным транзисторным ключом | 1991 |

|

SU1778886A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Стабилизатор постоянного напряжения с защитой от коротких замыканий | 1983 |

|

SU1156036A1 |

-0

-О

Даты

1967-01-01—Публикация