Изобретение относится к автоматике, к цифровой вычислительной технике и предназначено для построения логических элементов (ЛЭ) транзисторно-транзисторной логики (ТТЛ), реализующих функции троичной логики.

Известен логический элемент двоичной транзисторно-транзисторной логики «И-НЕ» с простым инвертором (Основы промышленной электроники: Учеб. для неэлектротехн. спец. вузов / В.Г. Герасимов, О.М. Князьков, А.И. Краснопольский, В.В. Сухоруков; Под ред. В.Г. Герасимова. - 3-е изд., перераб. и доп. - М.: Высш. шк., 1986. - С. 188). Он содержит (Рис.8.26, с.188): общую шину, шину источника положительного напряжения питания, соединенные с одноименными выводами питания, многоэмиттерный транзистор (МЭТ), база которого соединена через резистор, ограничивающий ток, с шиной источника положительного напряжения питания, а эмиттеры - с входными контактами ЛЭ. Коллектор многоэмиттерного транзистора соединен с базой второго транзистора, эмиттер которого соединен с общей шиной, а коллектор - с шиной источника положительного напряжения через нагрузочный резистор. Коллектор этого транзистора, представляющего собой ключевой инвертирующий каскад, соединяется также с выходным контактом ЛЭ.

Если на всех входах ЛЭ, а, следовательно, и на эмиттерах МЭТ действует высокий потенциал сигнала логической «1», то все переходы эмиттер–база этого транзистора закрыты, а переход коллектор–база МЭТ открыт приложенным в прямом направлении положительным напряжением источника питания через резистор, ограничивающий ток базы. Ток коллекторного перехода МЭТ, проходя через переход эмиттер–база второго транзистора, открывает его и переводит в режим насыщения, в результате чего на выходе появляется потенциал низкого уровня, соответствующий сигналу логического «0».

Если же хотя бы на одном из входов ЛЭ, а, следовательно, и на одном из эмиттеров МЭТ появится потенциал низкого уровня, соответствующий сигналу логического «0», то соответствующий переход эмиттер–база МЭТ откроется, и его базовый ток переключится из коллекторной цепи в эмиттерную. В результате этого потенциал базы второго транзистора окажется близким к потенциалу общей шины, этот транзистор закроется и на выходе ЛЭ с шины источника положительного напряжения через нагрузочный резистор установится потенциал высокого уровня, соответствующий сигналу логической «1».

Таким образом, сигнал логического «0» может быть на выходе ЛЭ только при потенциалах высокого уровня сигналов логической «1» на всех его входах, что, собственно, и соответствует содержанию логической операции «И-НЕ».

К недостаткам такого ЛЭ с простым инвертором обычно относят низкую помехоустойчивость, малую нагрузочную способность, сравнительно низкое быстродействия при работе на емкостную нагрузку, но основным его недостатком в данном случае является его неспособность выполнять функцию «И-НЕ» в троичной логике, где дополнительным логическим уровнем является логическое состояние «НЕИЗВЕСТНО» («НЕ ОПРЕДЕЛЕНО»), потенциал которого соответствует половине положительного напряжения питания.

Известен ЛЭ двоичной ТТЛ–логики «И-НЕ» с парафазным каскадом, открытым коллекторным выходом и повышенной нагрузочной способностью (Справочник по полупроводниковым диодам, транзисторам и интегральным схемам. Под общ. ред. Н. Н. Горюнова. Изд. 4-е, перераб. и доп. - М.: «Энергия», 1977, С. 504). Он содержит (Рис. К1ЛБ337, с. 504): общую шину, шину источника положительного напряжения питания, соединенные с одноименными выводами питания, МЭТ, база которого соединена через резистор, ограничивающий ток, с шиной источника положительного напряжения питания, а эмиттеры - с входными контактами ЛЭ. Коллектор многоэмиттерного транзистора соединен с базой второго транзистора, коллектор которого соединен с шиной источника положительного напряжения через первый нагрузочный резистор, а эмиттер - с общей шиной через второй нагрузочный резистор. Номиналы первого и второго нагрузочного резисторов выбраны таким образом, что образуется так называемый парафазный каскад: сигналы на эмиттере и коллекторе второго транзистора примерно равны по амплитуде, но противофазны, причем по отношению ко второму нагрузочному резистору этот транзистор включен как эмиттерный повторитель. Эмиттер второго транзистора соединен также с базой третьего, мощного выходного транзистора, эмиттер которого соединен с общей шиной, а коллектор - лишь с выходным контактом ЛЭ, что позволяет включить в коллекторную цепь низкоомный внешний нагрузочный резистор, соединенный с шиной источника положительного напряжения. Наличие в схеме ЛЭ мощного выходного транзистора позволяет повысить нагрузочную способность такого элемента, а открытый коллекторный выход позволяет управлять внешней нагрузкой или индикацией, либо согласовывать логические уровни ТТЛ с логическими уровням элементов, построенных на основе МОП транзисторов.

При воздействии высокого потенциала сигнала логической «1» на все входы ЛЭ, а, следовательно, и на все эмиттеры МЭТ, все переходы эмиттер–база этого транзистора закрыты, а его переход коллектор–база открыт приложенным в прямом направлении положительным напряжением источника питания через резистор, ограничивающий ток базы. Второй транзистор, образующий вместе со своими нагрузочными резисторами парафазный каскад, открыт током коллекторного перехода МЭТ, проходящим через его переход эмиттер–база. Второй транзистор при этом находится в режиме насыщения, и на его нагрузочном сопротивлении в цепи эмиттера устанавливается потенциал высокого уровня, обеспечивающий входной ток третьего мощного выходного транзистора. Следовательно, третий транзистор также насыщен из-за высокого потенциала на его базе, создающего ток через его переход база–эмиттер, в результате чего при подключенном внешнем нагрузочном резисторе на выходе ЛЭ появляется потенциал низкого уровня, соответствующий сигналу логического «0».

При воздействии потенциала низкого уровня, соответствующего сигналу логического «0» , хотя бы на один из входов ЛЭ, а значит и на один из эмиттеров МЭТ соответствующий переход эмиттер–база МЭТ откроется и его базовый ток переключится из коллекторной цепи в эмиттерную. В результате этого потенциал базы второго транзистора окажется близким к потенциалу общей шины, этот транзистор закроется, и на входе третьего мощного выходного транзистора также установится низкий потенциал с общей шины через резистор в цепи эмиттера второго транзистора. Этот транзистор также закроется, и на выходе ЛЭ с шины источника положительного напряжения через внешний нагрузочный резистор установится потенциал высокого уровня, соответствующий сигналу логической «1».

Очевидно, что сигнал логического «0» может быть на выходе такого ЛЭ только при потенциалах высокого уровня сигналов логической «1» на всех его входах, что опять же соответствует содержанию логической операции «И-НЕ».

Недостатками ЛЭ с парафазным каскадом, открытым коллекторным выходом и повышенной нагрузочной способностью также являются низкая помехоустойчивость и сравнительно низкое быстродействие при работе на емкостную нагрузку из-за способа формирования уровня логической «1» через внешний нагрузочный резистор, но основным его недостатком в данном случае также является его неспособность выполнять функцию «И-НЕ» с логическими уровнями троичной логики.

Известен ЛЭ ТТЛ со сложным инвертором (Шило В.Л. Популярные цифровые микросхемы: Справочник. - 2-е изд., исправленное. - М.: Радио и связь, 1989.- С. 16). Он содержит общую шину, шину источника положительного напряжения питания, соединенные с одноименными выводами питания, МЭТ, база которого соединена через резистор, ограничивающий ток, с шиной источника положительного напряжения питания, а эмиттеры - с входными контактами ЛЭ. Эмиттеры ЛЭ ТТЛ также соединены с общей шиной посредством защитных диодов, включенных по отношению к потенциалу логических сигналов в обратном смещении, защищающих ЛЭ от воздействия помех отрицательной полярности и ограничивающих их на уровне 0,5÷0,6В. Подобные диоды имеются обычно во всех схемах элементов ТТЛ, но поскольку они выполняют лишь защитную функцию и не влияют на логику работы элемента, то на принципиальных электрических схемах элементов их зачастую не отображают. Коллектор многоэмиттерного транзистора соединен с базой второго транзистора, коллектор которого соединен с шиной источника положительного напряжения через первый нагрузочный резистор, а эмиттер - с общей шиной через второй нагрузочный резистор. Номиналы первого и второго нагрузочного резисторов выбраны таким образом, что образуется так называемый парафазный каскад: сигналы на эмиттере и коллекторе второго транзистора примерно равны по амплитуде, но противофазны. Эмиттер второго транзистора соединен также с базой третьего выходного транзистора, эмиттер которого соединен с общей шиной, а коллектор - с выходным контактом ЛЭ. Коллектор второго транзистора соединен с базой четвертого выходного транзистора, эмиттер которого через диод, включенный в прямом направлении, соединен с коллектором третьего транзистора и с выходным контактом ЛЭ. Коллектор четвертого транзистора через токоограничивающий резистор соединен с шиной источника положительного напряжения.

Входной каскад ЛЭ с МЭТ работает точно так же, как и в схемах элементов ТТЛ, описание которых приведено выше. При наличии на всех входах ЛЭ, а, следовательно, и на эмиттерах МЭТ высокого потенциала сигнала логической «1», то все переходы эмиттер–база этого транзистора закрыты, а переход коллектор–база МЭТ открыт приложенным в прямом направлении положительным напряжением источника питания через резистор, ограничивающий ток базы. Ток коллекторного перехода МЭТ, проходя через переход эмиттер–база второго транзистора, открывает его и переводит в режим насыщения, в результате чего на его нагрузочном сопротивлении в цепи эмиттера устанавливается потенциал высокого уровня, обеспечивающий входной ток третьего выходного транзистора. Третий транзистор входит в насыщение из-за высокого потенциала на его базе, создающего ток через его переход база–эмиттер, и на его коллекторе, соединенном с выходным контактом ЛЭ, появляется потенциал низкого уровня, соответствующий сигналу логического «0».

Второй транзистор при этом находится в режиме насыщения, и на его нагрузочном сопротивлении в цепи эмиттера устанавливается потенциал высокого уровня, обеспечивающий входной ток третьего мощного выходного транзистора. Следовательно, третий транзистор также насыщен из-за высокого потенциала на его базе, создающего ток через его переход база–эмиттер, в результате чего при подключенном внешнем нагрузочном резисторе на выходе ЛЭ появляется потенциал низкого уровня, соответствующий сигналу логического «0». Диод в цепи эмиттера четвертого транзистора предназначен для обеспечения режима смещения этого транзистора так, чтобы этот транзистор был надежно закрыт при насыщенном втором транзисторе.

При наличии хотя бы на одном из входов ЛЭ низкого потенциала сигнала логического «0», МЭТ находится в режиме насыщения, и потенциал базы второго транзистора окажется близким к потенциалу общей шины, а, следовательно, второй транзистор закрыт. Поэтому закрыт и третий транзистор, поскольку ток через резистор нагрузки в эмиттерной цепи второго транзистора не протекает, и напряжение на базе третьего транзистора близко к потенциалу общей шины. Четвертый транзистор открыт, поскольку его база теперь подключена к шине источника положительного напряжения питания через резистор в цепи коллектора второго транзистора. Сопротивление резистора в цепи коллектора четвертого транзистора невелико, и предназначено лишь для ограничения тока в момент переключения выходных транзисторов, поэтому каскад на четвертом транзисторе работает как эмиттерный повторитель. Через четвертый транзистор, низкоомный резистор в его коллекторной цепи и открытый диод в эмиттерной цепи от источника положительного напряжения питания протекает ток нагрузки ЛЭ, и на выходной контакт поступает высокий уровень выходного напряжения, соответствующий уровню логической «1».

Следовательно, сигнал логической «1» может быть на выходе ЛЭ ТТЛ со сложным инвертором, если хотя бы на один из его входов поступает потенциал низкого уровня сигнала логического «0», а сигнал логического «0» может быть на выходе этого ЛЭ лишь при наличии потенциалов высокого уровня сигналов логической «1» на всех его входах, что соответствует таблице истинности логической операции «И-НЕ».

Элементы ТТЛ со сложным инвертором имеют большой перепад логических уровней, малую потребляемую мощность, высокое быстродействие и помехоустойчивость. Тем не менее, основным недостатком конструкции ЛЭ, выбранной в качестве прототипа, является то, что этот ЛЭ также не способен выполнять функцию «И-НЕ» с логическими уровнями троичной логики.

Технической проблемой заявляемого технического решения является создание ЛЭ транзисторно-транзисторной логики, способных выполнять логические функции с логическими уровнями троичной логики.

Технический результат заключается в повышении производительности логических элементов транзисторно-транзисторной логики, и расширении их функциональных возможностей.

Технический результат достигается тем, что согласно изобретению, логический элемент троичной транзисторно-транзисторной логики содержит общую шину и шину источника положительного напряжения, соединенные с одноименными выводами питания, входной каскад на основе МЭТ и выходной инвертирующий каскад, при этом схемотехнически выходной каскад выполнен таким образом, что он способен формировать троичные логические уровни на выходе ЛЭ из выходных аналоговых сигналов входного каскада основе МЭТ.

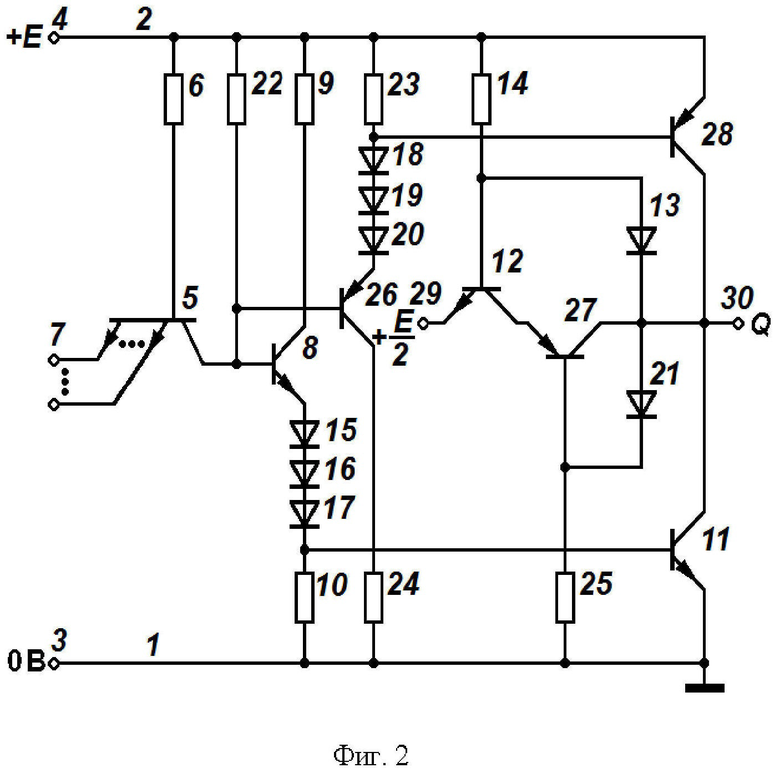

Изобретение поясняется чертежами, где

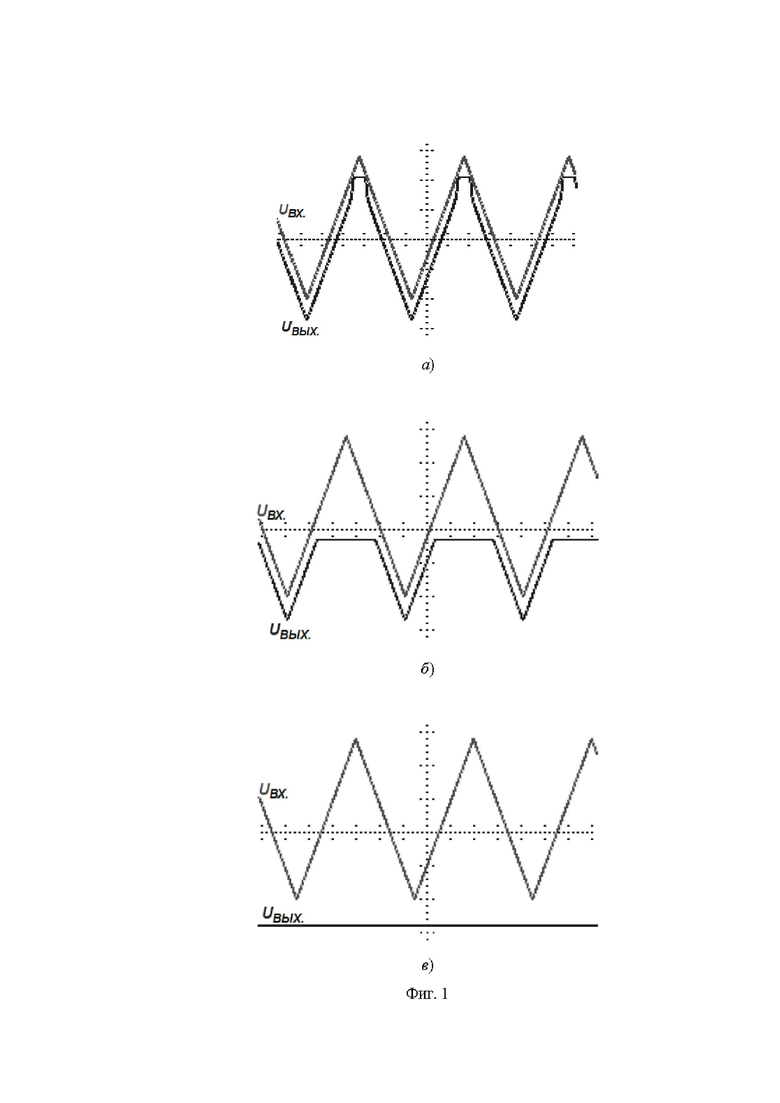

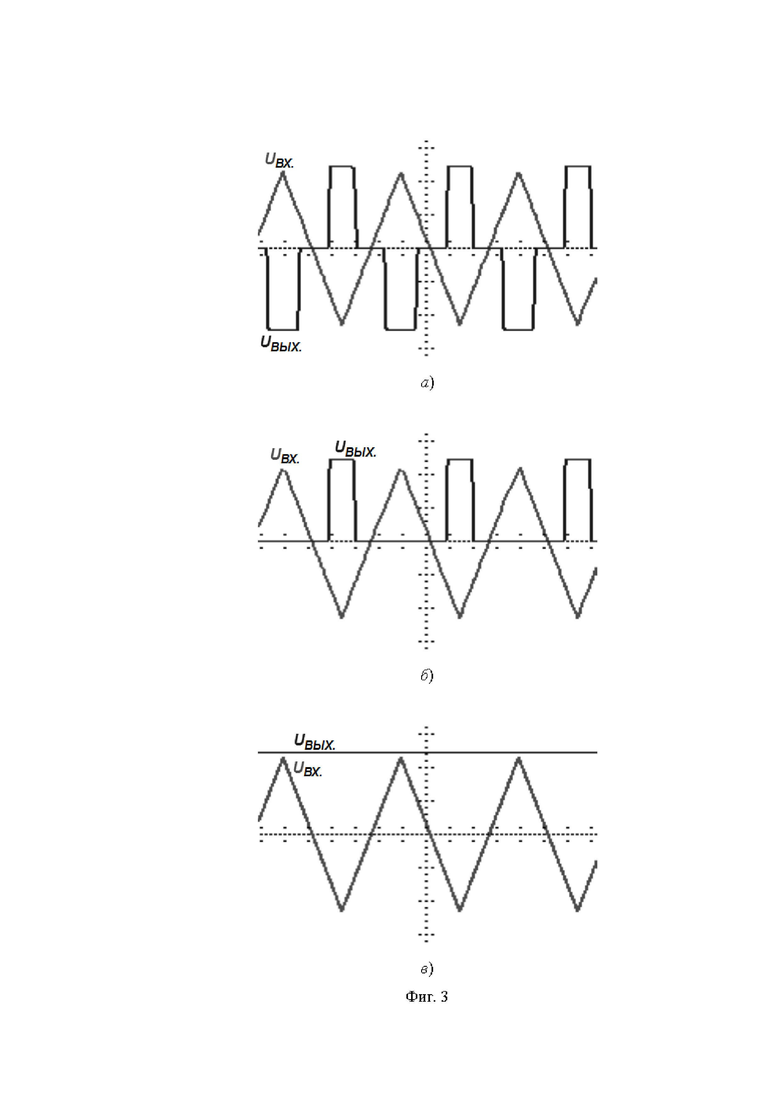

на фиг. 1 – представлены осциллограммы результатов испытаний входного каскада элемента ТТЛ на основе МЭТ;

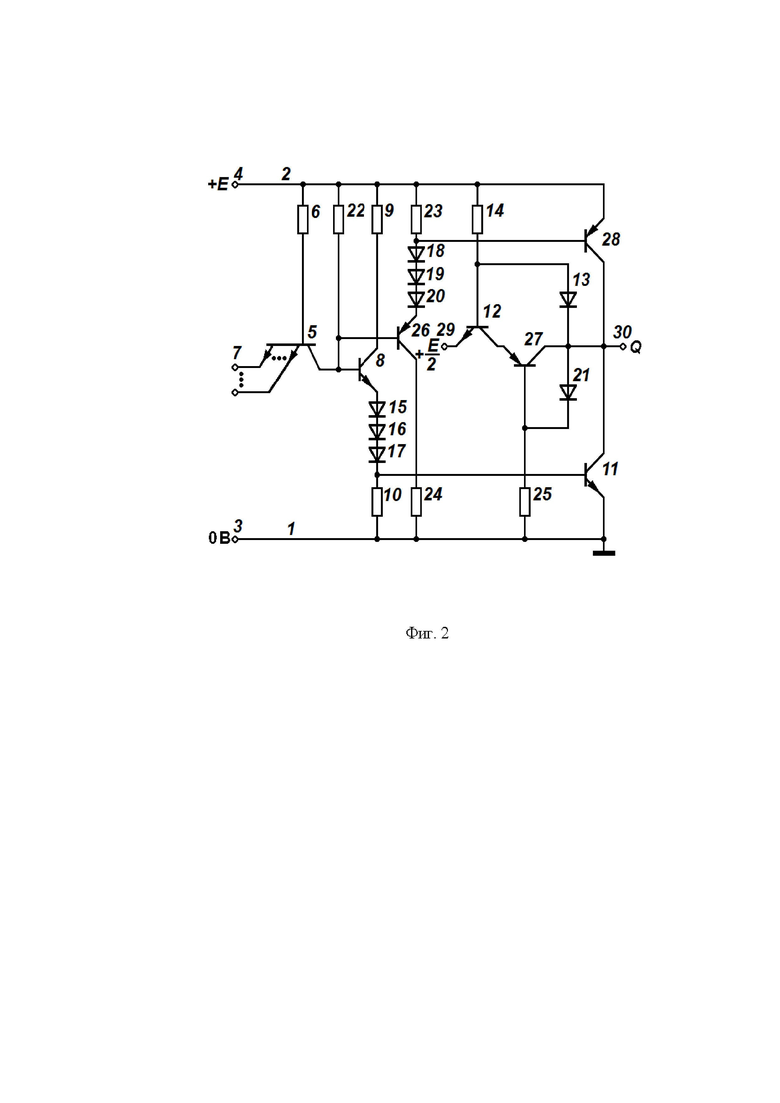

на фиг. 2 – приведена принципиальная электрическая схема устройства;

на фиг. 3 – представлены осциллограммы сигналов, иллюстрирующие принцип работы устройства;

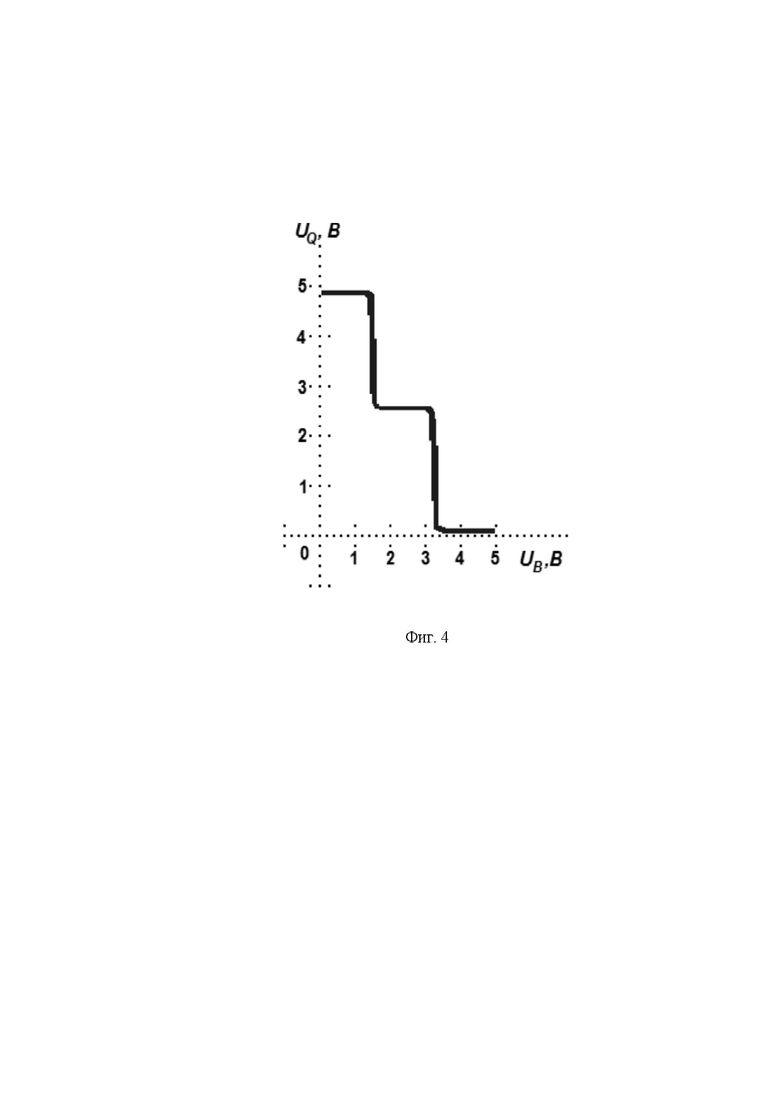

на фиг. 4 – передаточная характеристика ЛЭ;

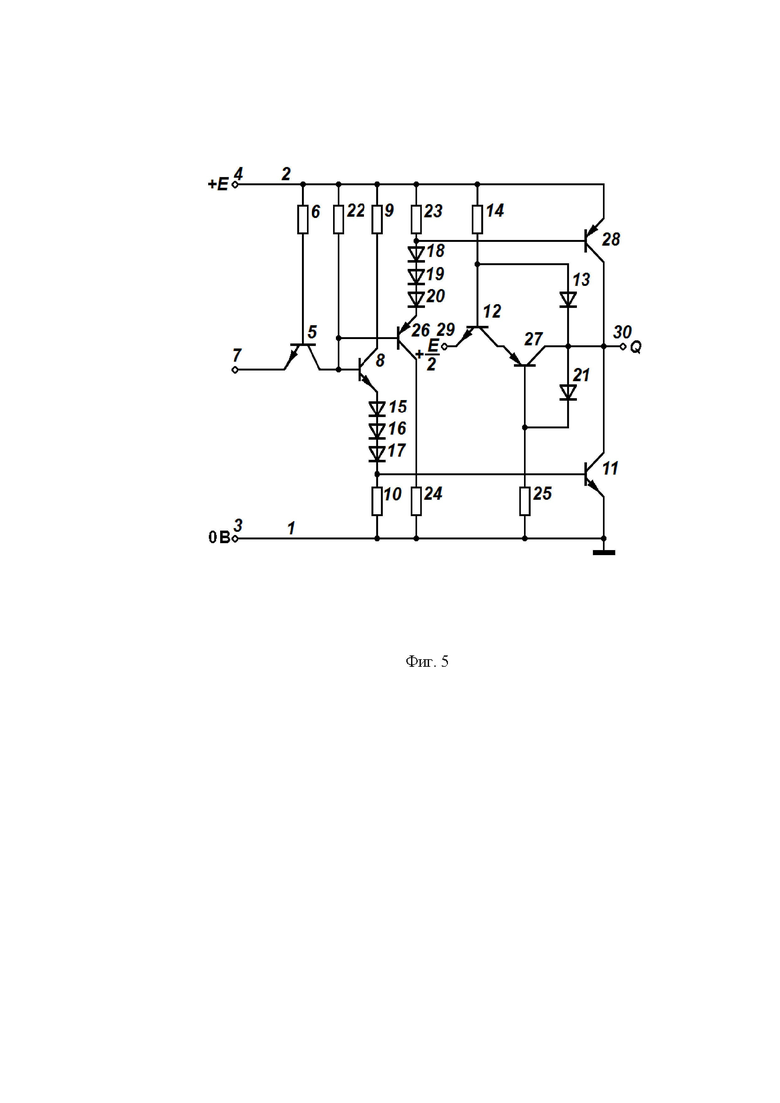

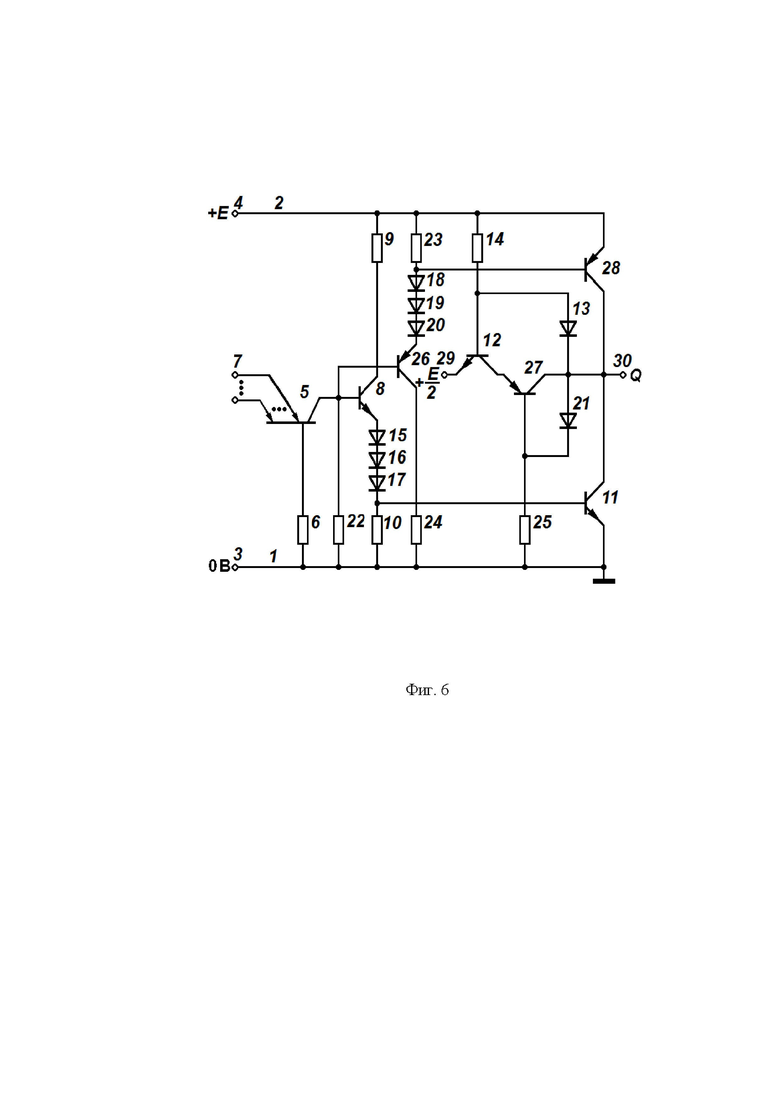

на фиг. 5, 6 – принципиальная электрическая схема устройства (варианты).

Позициями на чертежах обозначены:

1. общая шина;

2. шина источника положительного напряжения питания;

3. – 4. выводы питания;

5. МЭТ;

6. резистор, ограничивающий ток;

7. входные контакты;

8. транзистор;

9. первый нагрузочный резистор;

10. второй нагрузочный резистор;

11. транзистор;

12. четвертый транзистор;

13. диод;

14. резистор;

15. – 21. диоды;

22-25 резисторы;

26. – 28. транзисторы;

29. дополнительный вывод питания;

30. выходной контакт логического элемента.

Проведенный обзор ближайших аналогов ЛЭ двоичной логики показывает, что любой элемент ТТЛ состоит фактически из двух основных частей: входного каскада на основе МЭТ, обеспечивающего, собственно, логическую функцию элемента, а также его входные характеристики, и выходного каскада той или иной сложности, обеспечивающего усиление по мощности, нагрузочную способность элемента, потенциалы логических уровней и прочие выходные характеристики.

С учетом того, что теоретически двоичная логика является подмножеством троичной, было проведено исследование входного каскада элемента ТТЛ на основе МЭТ при воздействии на его входы уровнями, характерными для логических сигналов троичной логики, в рамках которой принято, что логический сигнал характерный для логического состояния «ИСТИННО» или «1», соответствует потенциалу близкому к потенциалу положительного напряжения источника питания (+E); логический сигнал характерный для логического состояния «ЛОЖНО» или «–1», соответствует потенциалу близкому к потенциалу общей шины питании (0 В), а дополнительному логическому состоянию - «НЕИЗВЕСТНО» («0», «НЕ ОПРЕДЕЛЕНО»), отсутствующему в двоичной логике, соответствует потенциал близкий к половине положительного напряжения источника питания (+E/2). При этом потенциалы логических состояний «ИСТИННО» или «1» и «ЛОЖНО» или «–1» троичной логики примерно соответствуют потенциалам «ИСТИННО» или «1» и «ЛОЖНО» или «0» двоичной логики.

Исследование только входного каскада элемента ТТЛ на основе МЭТ возможно, несмотря на его интегральное исполнение, благодаря наличию в серии элементов ТТЛ микросхемы расширителя по «ИЛИ», ЛЭ которой представляют собой типичный входной каскад элемента ТТЛ на основе МЭТ, к коллектору которого подключена база второго транзистора, выводы коллектора и эмиттера которого ни к чему не подключены, и выведены на внешние контакты (Юшин А.М. Цифровые микросхемы для электронных устройств: справочник – М.: Высшая школа, 1993, С.111). Это позволяет включить второй транзистор как эмиттерный повторитель, представляющий собой высокоомную нагрузку в коллекторной цепи МЭТ относительно шины положительного напряжения источника питания, и практически полностью повторяющий сигнал на коллекторе МЭТ со сдвигом 0,5÷0,6В по постоянному сигналу.

В процессе исследования входного каскада элемента ТТЛ на основе МЭТ на три из четырёх входов ЛЭ расширителя по «ИЛИ» подавались потенциалы, соответствующие троичным логическим уровням «1», «0», «–1», а на четвертый вход - пилообразное напряжение амплитудой 2,5 В и постоянной составляющей 2,5 В.

На фиг. 1 а изображены осциллограммы входного сигнала (UВХ.) и сигнала на коллекторе МЭТ (UВЫХ.) при подаче на остальные входы потенциала, соответствующего троичному логическому уровню «1». Очевидно, что в этом случае МЭТ пропускает пилообразный сигнал с входа полностью, внося лишь незначительные искажения в максимуме сигнала. Осциллограммы на фиг. 1 б иллюстрируют ситуацию при подаче на остальные входы МЭТ потенциала, соответствующего троичному логическому уровню «0» (2,5 В). В этом случае МЭТ пропускает лишь часть пилообразного сигнала ниже уровня 2,5 В. На осциллограмме фиг. 1 в видно, что при подаче на остальные входы МЭТ потенциала, соответствующего троичному логическому уровню «–1», он не пропускает входной пилообразный сигнал. Из представленных результатов следует, что входной каскад элемента ТТЛ на основе МЭТ способен различать троичные логические уровни и осуществлять над ними логические операции, хотя результат на выходе МЭТ представлен в аналоговой форме.

Следовательно, для достижения результата заявляемого технического решения в конструкцию выходного каскада ЛЭ ТТЛ - сложного инвертора - следует внести изменения, позволяющие ему обрабатывать аналоговый сигнал с выхода МЭТ и формировать на выходе ЛЭ потенциалы, соответствующие троичным логическим уровням «1», «0», «–1».

Устройство содержит общую шину 1, шину источника положительного напряжения питания 2, соединенные с одноименными выводами питания 3, 4, МЭТ 5, база которого соединена через резистор 6, ограничивающий ток, с шиной источника положительного напряжения питания 2, а эмиттеры - с входными контактами ЛЭ 7, в коллекторную цепь МЭТ 5 включен нагрузочный резистор 22, обеспечивающий базовый ток второго транзистора 8, подключенного базовым выводом к коллектору МЭТ 5, в ситуации, когда на все эмиттеры МЭТ 5 подан высокий потенциал сигналов логической «1», и ток коллектора сравнительно мал. Коллектор второго транзистора 8 через нагрузочный резистор 9 соединен с шиной источника положительного напряжения 2, а эмиттер - с общей шиной 1 через диоды 15-17 и второй нагрузочный резистор 10. Резистор 9 при этом имеет сравнительно небольшую величину, и в его функцию входит ограничение коллекторного тока транзистора 8 при открытии третьего транзистора 11, база которого подключена к верхнему по схеме выводу резистора 10. Диоды 15-21 обеспечивают порог включения транзистора 11, при уровне входного сигнала примерно +2⋅E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нём равном примерно 0,5÷0,6 В. Коллектор транзистора 11, соединяется с выходным контактом 30 (Q) логического элемента и через диод 13 - с резистором 14, подключенным к шине источника положительного напряжения питания 2. Резистор 14 представляет собой коллекторную нагрузку транзистора 11 и цепь смещения подключенного к нему выводом базы четвертого транзистора 12, входящего в состав ключа, коммутирующего на выходной контакт 30 логического элемента совместно с вновь введенным в конструкцию транзистором 27, внешнее напряжение +E / 2, поступающее на вывод 29 транзистора 12. Внешнее напряжение +E / 2 легко получить из положительного напряжения питания +E с помощью внешнего низкоомного делителя или специальной схемы, создающей так называемый потенциал средней точки.

Базовым выводом к коллектору МЭТ 5 подключен транзистор 26 типа p-n-p, коллектор которого через токоограничивающий резистор 24 соединен с общей шиной 1, а эмиттер - с источником положительного напряжения питания 2 через диоды 18-20 и нагрузочный резистор 23, к нижнему по схеме выводу которого своим базовым выводом подключен вновь введенный в конструкцию транзистор 28 также p-n-p–типа. Диоды 18-20 обеспечивают порог включения транзистора 28, при уровне входного сигнала примерно +E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нём равном примерно 0,5÷0,6 В. Коллектор транзистора 28, соединяется с выходным контактом 30 (Q) логического элемента и через диод 21 - с резистором 25, подключенным к общей шине 1. Резистор 25 представляет собой коллекторную нагрузку транзистора 28 и цепь смещения подключенного к нему выводом базы вновь введенного транзистора 27 p-n-p–типа, входящего в состав ключа, коммутирующего на выходной контакт 30 логического элемента совместно с транзистором 12, внешнее напряжение +E / 2, поступающее на вывод 29.

Таким образом, в схеме выходного каскада ЛЭ существуют практически два взаимно симметричных канала, управляющих своими выходными транзисторами 11 и 28, работающими на внешнюю нагрузку через выходной контакт 30 логического элемента и формирующими управляющие сигналы на базах транзисторов 12 и 27, совместно коммутирующими на выходной контакт 30 внешнее напряжение +E / 2, поступающее на вывод 29. Каскады на транзисторах 8 и 26 представляют собой фактически эмиттерные повторители с диодными пороговыми элементами в цепях эмиттеров, развязывающие выходные ключи на транзисторах 11 и 28 от входного логического каскада на МЭТ 5, причем ключевой каскад на транзисторе 11 формирует низкий выходной потенциал, соответствующий логической «–1», на выходе 30 ЛЭ в то время, когда входах 7 ЛЭ и эмиттерах МЭТ 5, действует высокий потенциал, соответствующий логической «1». Этот же ключевой каскад на транзисторе 11 в этот же момент через диод 13 запирает низким потенциалом на базе транзистор 12, не позволяя ему пропускать на выходной контакт 30 логического элемента внешнее напряжение +E / 2, поступающее на вывод 29. Эмиттерный повторитель на транзисторе 26 с диодными пороговыми элементами в цепи эмиттера управляет выходным ключевым каскад на транзисторе 28, который формирует высокий выходной потенциал, соответствующий логической «1», на выходе 30 ЛЭ в то время, когда входах 7 ЛЭ и эмиттерах МЭТ 5, действует низкий потенциал, соответствующий логической «–1». В этот же момент транзистор 28 через диод 21 запирает высоким потенциалом на базе транзистор 27, не позволяя ему вместе с транзистором 12 пропускать на выходной контакт 30 логического элемента внешнее напряжение +E / 2, поступающее на вывод 29.

Следовательно, два взаимно симметричных канала обеспечивают инверсию входных логических сигналов «1» и «–1» соответственно. Ключевой каскад на транзисторах 12 и 27, пропускает на выходной контакт 30 логического элемента внешнее напряжение +E / 2, поступающее на вывод 29 и соответствующее логическому «0», в те моменты, когда на выходе 30 ЛЭ потенциал не соответствует ни логической «1», ни «–1», что возможно лишь в ситуации, когда ключи на транзисторах 11 и 28 закрыты, а значит потенциал на входах 7 ЛЭ соответствует логическому «0», что совершенно справедливо, поскольку в троичной логике инверсия логического «0» - «НЕИЗВЕСТНО» - и есть логический «0».

Рассмотрим принцип работы устройства в предположении наличия у ЛЭ двух входов 7 и, соответственно, лишь двух эмиттеров у МЭТ 5 с целью упрощения. По индукции это будет справедливо и для большего числа входов. Устройство в таком случае работает следующим образом.

При наличии на всех входах 7 ЛЭ, а, следовательно, и на эмиттерах МЭТ 5 высокого потенциала сигнала логической «1», то все переходы эмиттер–база этого транзистора закрыты, а переход коллектор–база МЭТ 5 открыт приложенным в прямом направлении положительным напряжением источника питания через резистор 6, ограничивающий ток базы. Ток коллекторного перехода МЭТ 5, складываясь с током, протекающим через резистор 22, проходя через переход эмиттер–база транзистора 8 максимально открывает этот транзистор. Поскольку транзистор 8 включен по схеме эмиттерного повторителя, его входное сопротивление велико, и поэтому ток, протекающий через резистор 22, мал, тем более что этот резистор шунтируется прямосмещенным переходом коллектор–база МЭТ 5. Следовательно, к базе транзистора 8 приложено практически полное напряжение питания с шины 2, которое для микросхем ТТЛ составляет +5 В. С учетом падения напряжения на токоограничивающем резисторе 9 и насыщенном транзисторе 8, напряжение на его эмиттере составит примерно 5 В – (0,8…1 В) = 4,2…4 В. Этого напряжения достаточно, чтобы открыть три диода 15-17, падение напряжения на которых составляет примерно 3•(0,5÷0,6 В) = 1,5÷1,8 В, и подать высокий потенциал напряжения на базу транзистора 11. Этот высокий потенциал обеспечивает ток перехода база–эмиттер транзистора 11, открывает его и переводит в режим насыщения, в результате чего на выходе 30 ЛЭ появляется потенциал низкого уровня, соответствующий логическому сигналу «–1», и этот же потенциал, поступая через диод 13 на базу транзистора 12, запирает его, препятствуя подаче на выход 30 ЛЭ напряжения +E / 2, поступающего с вывода 29. В момент открытия транзистора 11 его прямосмещенный переход база–эмиттер шунтирует резистор 10, и токоограничивающий резистор 9 в цепи коллектора транзистора 8 препятствует возникновению чрезмерно больших коллекторных токов этого транзистора, действуя как элемент отрицательной обратной связи по току.

Транзистор 26 p-n-p–типа, подключенный к коллектору МЭТ 5 также включен по схеме эмиттерного повторителя, но напряжение на его эмиттере действует относительно шины источника положительного напряжения 2, поэтому транзисторы 8 и 26 действуют в противофазе. Следовательно, напряжения на эмиттере транзистора 26 недостаточно чтобы открыть диоды 18-20 в его эмиттерной цепи. Поэтому транзистор 28 p-n-p–типа закрыт положительным потенциалом шины источника положительного напряжения 2, и не способен влиять через диод 21 на потенциал базы транзистора 27. На базу этого транзистора 27 через резистор 25 действует открывающий его потенциал общей шины 1, но включенный последовательно с ним транзистор 12 закрыт потенциалом низкого уровня с коллектора транзистора 11 через диод 13. Поэтому внешнее напряжение +E / 2, подающееся на вывод 29 не поступает на выход 30 ЛЭ, на котором действует потенциал низкого уровня с коллектора транзистора 11, соответствующий логическому сигналу «–1».

Следовательно, при наличии на всех входах 7 ЛЭ, а, следовательно, и на эмиттерах МЭТ 5 высокого потенциала сигнала логической «1», на выходе 30 ЛЭ действует потенциал низкого уровня, соответствующий логическому сигналу «–1».

Рассмотрим ситуацию, когда на одном из входов 7 ЛЭ, а, следовательно, и на одном из эмиттеров МЭТ 5 действует потенциал низкого уровня, соответствующий логическому сигналу «–1», а на другом - высокий потенциала сигнала логической «1». Потенциал низкого уровня, соответствующий логическому сигналу «–1», на одном из эмиттеров МЭТ 5 открывает его переход база–эмиттер, в результате чего МЭТ 5 находится в режиме насыщения, и потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, окажется близким к потенциалу общей шины. В силу того что транзисторы 8 и 26 действуют в противофазе, как это было подробно описано выше, ключ на транзисторе 11 оказывается закрытым, а ключ на транзисторе 28 — насыщен и открыт, в результате чего на выходе 30 ЛЭ действует потенциал высокого уровня, соответствующий логическому сигналу «1». Этот потенциал через диод 21 закрывает ключ на транзисторе 27, и внешнее напряжение +E / 2, подающееся на вывод 29 не может поступить на выход 30 ЛЭ.

Если на второй из входов 7 ЛЭ, вместо высокого потенциала сигнала логической «1» подать потенциал +E / 2, соответствующий логическому «0», это не изменит ситуацию, поскольку потенциал низкого уровня, соответствующий логическому сигналу «–1», на первом входе удерживает МЭТ 5 в режиме насыщения, а потенциал +E / 2 на втором из входов 7 ЛЭ поддерживает свой переход база–эмиттер в режиме обратного смещения, вследствие чего он не способен изменить режим работы МЭТ 5.

Таким образом, если хотя бы на одном из входов 7 ЛЭ действует логический сигнал «-1», то на выходе 30 ЛЭ устанавливается его инверсия «1» вне зависимости от логического уровня на другом входе. Очевидно, что ЛЭ с точностью до инверсии корректно отрабатывает логическую ситуацию: если одно из логических высказываний ложно, то и результат логической операции «И» будет ложным, каким бы ни было второе логическое высказывание.

Предположим теперь, что на одном из входов 7 ЛЭ, а, следовательно, и на одном из эмиттеров МЭТ 5 действует потенциал уровня +E / 2, соответствующий логическому сигналу «0», а на другом - высокий потенциала сигнала логической «1».

Потенциал уровня +E / 2, на одном из эмиттеров МЭТ 5 ниже потенциала +E на его базе, следовательно, соответствующий переход база–эмиттер МЭТ 5 будет открыт, а переход, на котором действует высокий потенциала сигнала логической «1», смещен в обратном направлении, МЭТ 5 в результате этого войдёт в режим насыщения, и потенциал на его коллекторе будет превышать потенциал +E / 2, примерно на 0,2 В. Этот потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, не позволит каждому из них открыть диоды 15-17 и 18-20 в своих эмиттерных цепях, поскольку напряжение на эмиттерах с учетом падения напряжения на токоограничивающих резисторах 9 и 24 примерно на 0,8…1 В меньше потенциала на базах. Следовательно, выходные ключи на транзисторах 11 и 28 окажутся запертыми потенциалами, подаваемыми на их базы через резисторы 10 и 23 с общей шины 1 и шины источника положительного напряжения 2. Поскольку на выход 30 ЛЭ в этот момент не действуют ни потенциал высокого уровня, ни потенциал низкого уровня, ключи на транзисторах 12 и 27 оказываются открытыми через резисторы 14 и 25 потенциалам шины источника положительного напряжения 2 и общей шины 1, соответственно, в результате чего на выход 30 ЛЭ подаётся внешнее напряжение +E / 2 с вывода 29, что соответствует логическому сигналу «0».

Этот результат показывает, что ЛЭ с точностью до инверсии корректно обрабатывает логическую ситуацию: если одно из логических высказываний истинно, а второе - неизвестно или не определено, то и результат логической операции «И» будет неопределённым.

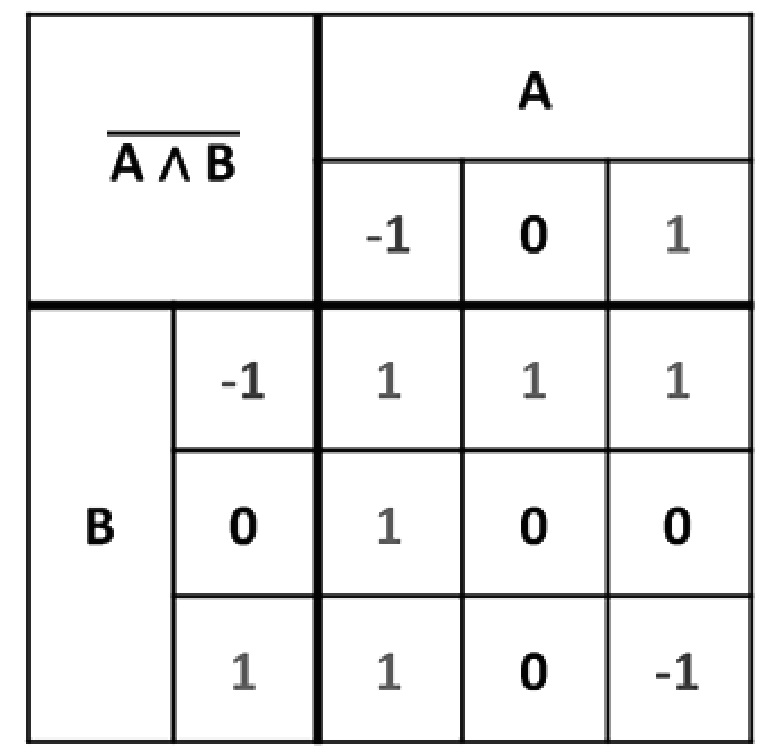

Таким образом, при подаче на входы 7 ЛЭ потенциалов, соответствующих троичным логическим уровням «–1», «0», «1», он работает в соответствии с таблицей истинности 1.

Таблица 1

Из приведенных в таблице 1 данных следует, что заявляемое устройство реализует основные свойства ЛЭ «И-НЕ» троичной логики:

- ЛЭ «И-НЕ» троичной логики избирательно реагирует на совпадение сигналов логической «1»;

- Логический вентиль «И-НЕ» троичной логики прозрачен (пропускает логический сигнал) при наличии логической «1» на одном из входов и не прозрачен при наличии логической «–1» на одном из входов;

- Инверсия логического «0» в троичной логике есть «0»;

- ЛЭ «И-НЕ» троичной логики реализует функцию инверсии минимума двух и более аргументов, принимающих логические значения «–1», «0», «1».

С целью апробации был изготовлен макет заявляемого устройства, и исследованы его свойства при подаче на один из входов потенциалов, соответствующих троичным логическим уровням «1», «0», «–1», а на другой вход - пилообразного напряжения амплитудой 2,5 В и постоянной составляющей 2,5 В.

Результаты исследования представлены на фиг. 3. На фиг. 3 а изображены осциллограммы входного сигнала (UВХ.) и сигнала на выходе ЛЭ (UВЫХ.) при подаче на первый вход потенциала, соответствующего троичному логическому уровню «1». В этом случае ЛЭ переключается на уровнях пилообразного сигнала примерно равных +Е/3 и +2Е/3, формируя инвертированный выходной трёхуровневый сигнал. Осциллограммы на фиг. 3 б иллюстрируют ситуацию при подаче на первый вход ЛЭ потенциала, соответствующего троичному логическому уровню «0» (2,5 В). В этом случае ЛЭ пропускает лишь часть пилообразного сигнала ниже уровня 2,5 В, инвертируя сигнал на выходе. На осциллограмме фиг. 3 в видно, что при подаче на первый вход ЛЭ потенциала, соответствующего троичному логическому уровню «–1», он не пропускает сигнал, удерживая на выходе высокий логический уровень «1». Таким образом, согласно приведенным на фиг. 3 осциллограммам, заявляемое устройство работает в полном соответствии с таблицей 1 и представляет собой ЛЭ «И-НЕ» троичной транзисторно-транзисторной логики.

Передаточная характеристика ЛЭ (зависимость UВЫХ от UВХ при подаче на другой вход потенциала, соответствующего троичному логическому уровню «1») изображена на фиг. 4 . Характеристика иллюстрирует пороги переключения ЛЭ на уровнях входного пилообразного сигнала примерно равных +Е/3 и +2Е/3.

Поскольку троичный элемент ТТЛ согласно заявляемому техническому решению обладает свойством инверсии по выходу, на его основе можно выполнить троичный инвертор, схемотехнически включив в позиции МЭТ идентичный ему по параметрам транзистора с одним эмиттером, так как технологически МЭТ может быть выполнен с количеством эмиттеров от одного до восьми. Схема троичного инвертора ТТЛ представлена на фиг. 5 . Выходной каскад инвертора работает полностью идентично схеме, изображенной на фиг. 2 . В функции транзистора входного каскада входит лишь обеспечение инвертору входных параметров, идентичных логическому элементу с многоэмиттерным транзистором на входе, что важно при взаимном соединении логических элементов.

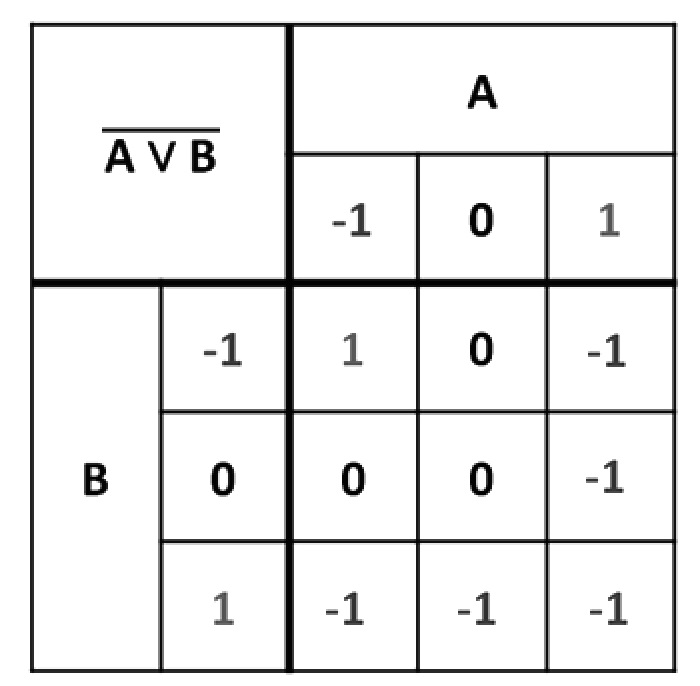

Если же во входном каскаде троичного элемента ТТЛ согласно заявляемому техническому решению применить МЭТ p-n-p-типа, подключив его базу через резистор 6 и коллектор через нагрузочный резистор 22 к общей шине 1, то непосредственно во входном каскаде произойдёт инверсия входных сигналов и выходного сигнала, следовательно, согласно правилам де Моргана (логические правила, связывающие пары логических операций при помощи логического отрицания), логический элемент по схеме, представленной на фиг. 6 , будет выполнять функцию «ИЛИ-НЕ» троичной логики. Так же, как и в случае троичного инвертора, выходной каскад ЛЭ «ИЛИ-НЕ» троичной логики работает полностью идентично схеме, изображенной на фиг. 2 . Но в результате инверсии входных сигналов и выходного сигнала непосредственно во входном каскаде, при подаче на входы 7 ЛЭ потенциалов, соответствующих троичным логическим уровням «–1», «0», «1», ЛЭ «ИЛИ-НЕ» троичной логики работает в соответствии с таблицей истинности 2.

Таблица 2

Из приведенных в таблице 2 данных следует, что заявляемое устройство реализует основные свойства ЛЭ «ИЛИ-НЕ» троичной логики:

- ЛЭ «ИЛИ-НЕ» троичной логики избирательно реагирует на совпадение сигналов логической «–1»;

- Логический вентиль «ИЛИ-НЕ» троичной логики прозрачен (пропускает логический сигнал) при наличии логической «–1» на одном из входов и не прозрачен при наличии логической «1» на одном из входов;

- Инверсия логического «0» в троичной логике есть «0» — выполняется и в случае троичного ЛЭ «ИЛИ-НЕ»;

- ЛЭ «И-НЕ» троичной логики реализует функцию инверсии максимума двух и более аргументов, принимающих логические значения «–1», «0», «1».

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Элемент транзисторно-транзисторной логики | 1986 |

|

SU1336225A1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

Изобретение относится к автоматике, к цифровой вычислительной технике и предназначено для построения логических элементов (ЛЭ) транзисторно-транзисторной логики (ТТЛ), реализующих функции троичной логики. Технический результат заключается в повышении производительности логических элементов транзисторно-транзисторной логики, и расширении их функциональных возможностей. Он достигается тем, что согласно изобретению логический элемент троичной транзисторно-транзисторной логики содержит общую шину и шину источника положительного напряжения, соединенные с одноименными выводами питания, входной каскад и выходной инвертирующий каскад, при этом схемотехнически выходной каскад выполнен таким образом, что он способен формировать троичные логические уровни на выходе ЛЭ из выходных аналоговых сигналов входного каскада. 2 з.п. ф-лы, 6 ил., 2 табл.

1. Логический элемент троичной транзисторно-транзисторной логики, характеризующийся тем, что содержит общую шину 1 и шину источника положительного напряжения 2, соединенные с одноименными выводами питания 3, 4,

входной каскад, включающий многоэмиттерный транзистор 5, выводы эмиттеров которого соединены с одним или несколькими входными контактами 7, база и коллектор транзистора 5 через резистор 6 и резистор 22 соответственно соединены с одной из шин,

выходной каскад, включающий транзисторы 8, 11, 12, 26, 27, 28, резисторы 9, 10, 14, 23, 24, 25, диоды 13 и 21 и группы последовательно соединенных диодов 15-17 и 18-20, а также дополнительный вывод питания 29,

при этом база транзистора 8 соединена с коллектором транзистора 5, коллектор транзистора 8 через токоограничивающий резистор 9 соединен с шиной источника положительного напряжения 2, а эмиттер транзистора 8 через группу диодов 15-17 и нагрузочный резистор 10 соединен с общей шиной 1,

база транзистора 11 через резистор 10 подключена к общей шине 1 и диоду 17, коллектор транзистора 11 соединен с выходным контактом 30 логического элемента и через диод 13 подключен к базе транзистора 12, а через резистор 14 подключен к шине источника положительного напряжения питания 2, эмиттер транзистора 11 соединен с общей шиной 1,

база транзистора 26 типа p-n-p соединена с коллектором транзистора 5, коллектор транзистора 26 через токоограничивающий резистор 24 соединен с общей шиной 1, эмиттер транзистора 26 через группу диодов 18-20 и резистор 23 соединен с шиной источника положительного напряжения 2,

базовый вывод транзистора 28 p-n-p–типа через резистор 23 подключен к шине источника положительного напряжения питания 2 и к диоду 18, коллектор транзистора 28 соединен с выходным контактом 30 логического элемента и через диод 21 - с базой транзистора 27, а через резистор 25 - с общей шиной 1, эмиттер транзистора 28 соединен с шиной источника положительного напряжения 2,

эмиттер транзистора 12 подключен к дополнительному выводу питания 29, база транзистора 12 через резистор 14 подключена к шине источника положительного напряжения 2 и через диод 13 - к коллектору транзистора 11, а коллектор транзистора 12 соединен с эмиттером транзистора 27 p-n-p–типа, коллектор которого соединен с выходным контактом 30, а база - через резистор 25 подключена к общей шине 1 и через диод 21 - к коллектору транзистора 28.

2. Логический элемент по п. 1, характеризующийся тем, что многоэмиттерный транзистор 5 n-p-n–типа, технологически выполненный с одним эмиттером, подключен выводом эмиттера к входному контакту 7, базой через резистор 6, и коллектором через резистор 22 - к шине источника положительного напряжения 2.

3. Логический элемент по п. 1, характеризующийся тем, что многоэмиттерный транзистор 5 p-n-p–типа выводами эмиттеров соединен с входными контактами 7 и подключен базой через резистор 6, а коллектором через резистор 22 к общей шине 1.

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Способ регенерирования сульфо-кислот, употребленных при гидролизе жиров | 1924 |

|

SU2021A1 |

Авторы

Даты

2022-10-28—Публикация

2022-05-27—Подача