Область техники

Группа изобретений относится к автоматике, к цифровой вычислительной технике и предназначена для построения логических элементов (ЛЭ) транзисторно-транзисторной логики (ТТЛ), реализующих функции троичной циклической инверсии.

Уровень техники

В двоичной логике элементы «И», «ИЛИ», «НЕ», являются базовыми. На их основе можно реализовать цифровое устройство практически любой сложности.

Связь между функциями «И», «ИЛИ» определяют правила де Моргана посредством операции инверсии («НЕ»). Поэтому любой из двухвходовых логических элементов с инверсией по выходу будет фактически универсальным. Но благодаря более простой схемотехнике, универсальным логическим элементом в ТТЛ принято считать вентиль «И-НЕ». На его основе можно реализовать любой другой базисный элемент.

Двоичный логический элемент «НЕ» (инвертор) осуществляет следующее преобразование двоичных логических сигналов: «0»→«1», «1»→«0», что фактически является инкрементом и декрементом в пределах одного разряда.

Троичный логический инвертор осуществляет преобразование троичных логических сигналов следующим образом: «-1»→«+1», «0»→«0», «+1»→«-1». С учетом того, что двоичный логический «0» («ЛОЖЬ») соответствует троичной логической «-1», двоичной логической «1» («ИСТИНА») соответствует троичная логическая «+1», а под троичным логическим «0» («НЕОПРЕДЕЛЕНО») может скрываться лишь «ИСТИНА» или «ЛОЖЬ», фактически троичный логический инвертор выполняет те же самые действия, что и двоичный логический инвертор, преобразуя «ИСТИНУ» в «ЛОЖЬ», а «ЛОЖЬ» в «ИСТИНУ». Но в троичной логике такие преобразования логических сигналов не являются инкрементом и декрементом, а представляют лишь изменение знака числа.

Таким образом, в троичной логике наряду с обычной инверсией существуют две функции так называемых циклических инверсий, осуществляющих следующие операции преобразования троичных логических уровней: «+1» → «0», «0» → «-1», «-1» → «+1» и «+1» → «-1», «-1» → «0», «0» → «+1». Подобное преобразование напоминает вращение против часовой и по часовой стрелке, иначе говоря, в левую и в правую стороны, почему данные троичные логические элементы и получили соответствующие названия левой и правой циклических инверсий. А технической проблемой заявляемого технического решения является создание ЛЭ транзисторно-транзисторной логики, способных выполнять логические функции левой и правой циклических инверсий с логическими сигналами троичной логики.

Известен ЛЭ «НЕ» двоичной ТТЛ-логики с парафазным каскадом и открытым коллекторным выходом (Юшин А.М. Цифровые микросхемы для электронных устройств: Справ. - М.: Высш. шк., 1993, С. 37). Инвертор содержит общую шину, шину источника положительного напряжения питания, соединенные с одноименными выводами питания, МЭТ, база которого соединена через резистор, ограничивающий ток, с шиной источника положительного напряжения питания, а единственный эмиттер - с входным контактом ЛЭ. Данный транзистор технологически выполнен по многоэмиттерной технологии, но на кристалле сформирован лишь один эмиттер. Коллектор этого транзистора соединен с базой второго транзистора, коллектор которого соединен с шиной источника положительного напряжения через первый нагрузочный резистор, а эмиттер - с общей шиной через второй нагрузочный резистор. Номиналы первого и второго нагрузочного резисторов выбраны таким образом, что образуется так называемый парафазный каскад: сигналы на эмиттере и коллекторе второго транзистора примерно равны по амплитуде, но противофазны, причем по отношению ко второму нагрузочному резистору этот транзистор включен как эмиттерный повторитель. Эмиттер второго транзистора соединен также с базой третьего, выходного транзистора, эмиттер которого соединен с общей шиной, а коллектор - лишь с выходным контактом ЛЭ, что позволяет включить в коллекторную цепь внешний нагрузочный резистор, соединенный с шиной источника положительного напряжения. Наличие в схеме инвертора открытого коллекторного выхода позволяет также управлять внешней нагрузкой или индикацией, либо согласовывать логические уровни ТТЛ с логическими уровням элементов, построенных на основе МОП транзисторов.

Недостатками ЛЭ «НЕ» с парафазным каскадом, открытым коллекторным выходом являются низкая помехоустойчивость и сравнительно низкое быстродействие при работе на емкостную нагрузку из-за способа формирования уровня логической «1» через внешний нагрузочный резистор, но основным его недостатком в данном случае является его неспособность выполнять функцию циклической инверсии с логическими уровнями троичной логики.

Известен ЛЭ «НЕ» ТТЛ со сложным инвертором (Юшин А.М. Цифровые микросхемы для электронных устройств: Справ. - М.: Высш. шк., 1993.- С. 36). Он содержит общую шину, шину источника положительного напряжения питания, соединенные с одноименными выводами питания, МЭТ, база которого соединена через резистор, ограничивающий ток, с шиной источника положительного напряжения питания, а единственный эмиттер - с входным контактом ЛЭ. Данный транзистор технологически выполнен по многоэмиттерной технологии, но на кристалле сформирован лишь один эмиттер. Такое решение обеспечивает согласование ЛЭ ТТЛ по входному току. Эмиттер ЛЭ ТТЛ также соединен с общей шиной посредством защитного диода, включенного по отношению к потенциалу логических сигналов в обратном смещении, защищающего ЛЭ от воздействия помех отрицательной полярности и ограничивающих их на уровне 0,5÷0,6 В. Подобные диоды имеются обычно во всех схемах элементов ТТЛ, но поскольку они выполняют лишь защитную функцию и не влияют на логику работы элемента, то на принципиальных электрических схемах элементов их зачастую не отображают. Коллектор многоэмиттерного транзистора соединен с базой второго транзистора, коллектор которого соединен с шиной источника положительного напряжения через первый нагрузочный резистор, а эмиттер - с общей шиной через второй нагрузочный резистор. Номиналы первого и второго нагрузочного резисторов выбраны таким образом, что образуется так называемый парафазный каскад: сигналы на эмиттере и коллекторе второго транзистора примерно равны по амплитуде, но противофазны. Эмиттер второго транзистора соединен также с базой третьего выходного транзистора, эмиттер которого соединен с общей шиной, а коллектор - с выходным контактом ЛЭ. Коллектор второго транзистора соединен с базой четвертого выходного транзистора, эмиттер которого через диод, включенный в прямом направлении, соединен с коллектором третьего транзистора и с выходным контактом ЛЭ. Коллектор четвертого транзистора через токоограничивающий резистор соединен с шиной источника положительного напряжения.

Входной каскад ЛЭ с МЭТ работает точно так же, как и в схеме инвертора ТТЛ, описание которого приведено выше. При наличии на входе ЛЭ, а, следовательно, и на единственном эмиттере МЭТ высокого потенциала сигнала логической «1», переход эмиттер-база этого транзистора закрыт, а переход коллектор-база МЭТ открыт приложенным в прямом направлении положительным напряжением источника питания через резистор, ограничивающий ток базы. Ток коллекторного перехода МЭТ проходя через переход эмиттер-база второго транзистора, открывает его и переводит в режим насыщения, в результате чего на его нагрузочном сопротивлении в цепи эмиттера устанавливается потенциал высокого уровня, обеспечивающий входной ток третьего выходного транзистора. Третий транзистор входит в насыщение из-за высокого потенциала на его базе, создающего ток через его переход база-эмиттер, и на его коллекторе, соединенном с выходным контактом ЛЭ, появляется потенциал низкого уровня, соответствующий логическому «0».

Второй транзистор при этом находится в режиме насыщения, и на его нагрузочном сопротивлении в цепи коллектора устанавливается потенциал низкого уровня, обеспечивающий запирание четвертого выходного транзистора. Диод в цепи эмиттера четвертого транзистора предназначен для обеспечения режима смещения этого транзистора так, чтобы этот транзистор был надежно закрыт при насыщенных втором и третьем транзисторах.

При наличии на входе инвертора низкого потенциала сигнала логического «0» возникает ток эмиттер-база, МЭТ находится в режиме насыщения, и потенциал базы второго транзистора окажется близким к потенциалу общей шины, а, следовательно, второй транзистор закрыт. Поэтому закрыт и третий транзистор, поскольку ток через резистор нагрузки в эмиттерной цепи второго транзистора не протекает, и напряжение на базе третьего транзистора близко к потенциалу общей шины. Четвертый транзистор открыт, поскольку его база теперь подключена к шине источника положительного напряжения питания через резистор в цепи коллектора второго транзистора. Сопротивление резистора в цепи коллектора четвертого транзистора невелико, и предназначено лишь для ограничения тока в момент переключения выходных транзисторов, поэтому каскад на четвертом транзисторе работает как эмиттерный повторитель. Через четвертый транзистор, низкоомный резистор в его коллекторной цепи и открытый диод в эмиттерной цепи от источника положительного напряжения питания протекает ток нагрузки ЛЭ, и на выходной контакт поступает высокий уровень выходного напряжения, соответствующий уровню логической «1».

Элементы ТТЛ со сложным инвертором имеют большой перепад логических уровней, малую потребляемую мощность, высокое быстродействие и помехоустойчивость. Тем не менее, основным недостатком конструкции подобного ЛЭ «НЕ» в данном случае является то, что он также не способен выполнять функцию циклической инверсии с логическими уровнями троичной логики.

Известен логический элемент троичной транзисторно-транзисторной логики (патент РФ №2782474, МПК Н03К 19/088, опубл. 28.10.2022). Согласно изобретению троичный инвертор ТТЛ содержит общую шину и шину источника положительного напряжения, соединенные с одноименными выводами питания, входной каскад и выходной инвертирующий каскад, при этом схемотехнически выходной каскад выполнен таким образом, что он способен формировать троичные логические уровни на выходе ЛЭ из выходных аналоговых сигналов входного каскада.

Троичный логический инвертор ТТЛ способен обрабатывать троичные логические сигналы, осуществляя их преобразование следующим образом: «-1»→«+1», «0»→«0», «+1»→«-1», но он не может реализовать функции циклических инверсий, осуществляющих следующие преобразования троичных логических уровней: «+1»→«0», «0»→«-1», «-1»→«+1» и «+1»→«-1», «-1»→«0», «0»→«+1», что в данном случае является его основным недостатком.

Раскрытие сущности изобретения

Технической проблемой заявляемых технических решений является создание ЛЭ транзисторно-транзисторной логики, способных выполнять логические функции циклических инверсий с логическими уровнями троичной логики.

Технический результат заключается в повышении производительности логических элементов троичной транзисторно-транзисторной логики, и расширении их функциональных возможностей, поскольку в троичной логике функционально полный набор логических функций (логический базис) образуют троичные аналоги элементов «И», «ИЛИ», а также любая из функций циклических инверсий.

Если проанализировать приведенные выше варианты преобразований, характерные для троичного инвертора и функций циклических инверсий, можно заметить, что троичный инвертор способен выполнить одно из преобразований левой циклической инверсии «-1»→«+1», и одно из преобразований правой циклической инверсии: «+1»→«-1».

Следовательно, для достижения результата заявляемого технического решения в конструкцию выходного каскада троичного инвертора ТТЛ следует внести изменения, позволяющие ему формировать на выходе ЛЭ логические уровни, соответствующие операциям, характерным для функций циклических инверсий.

Технический результат достигается тем, что согласно изобретению, логический элемент циклической инверсии троичной транзисторно-транзисторной логики содержит общую шину и шину источника положительного напряжения, соединенные с одноименными выводами питания, входной каскад на основе МЭТ и выходной инвертирующий каскад, при этом схемотехнически выходной каскад выполнен таким образом, что он способен формировать на выходе ЛЭ троичные логические уровни, соответствующие функциям циклической инверсии, из выходных сигналов входного каскада основе МЭТ.

Краткое описание чертежей

Группа изобретений поясняется чертежами, где

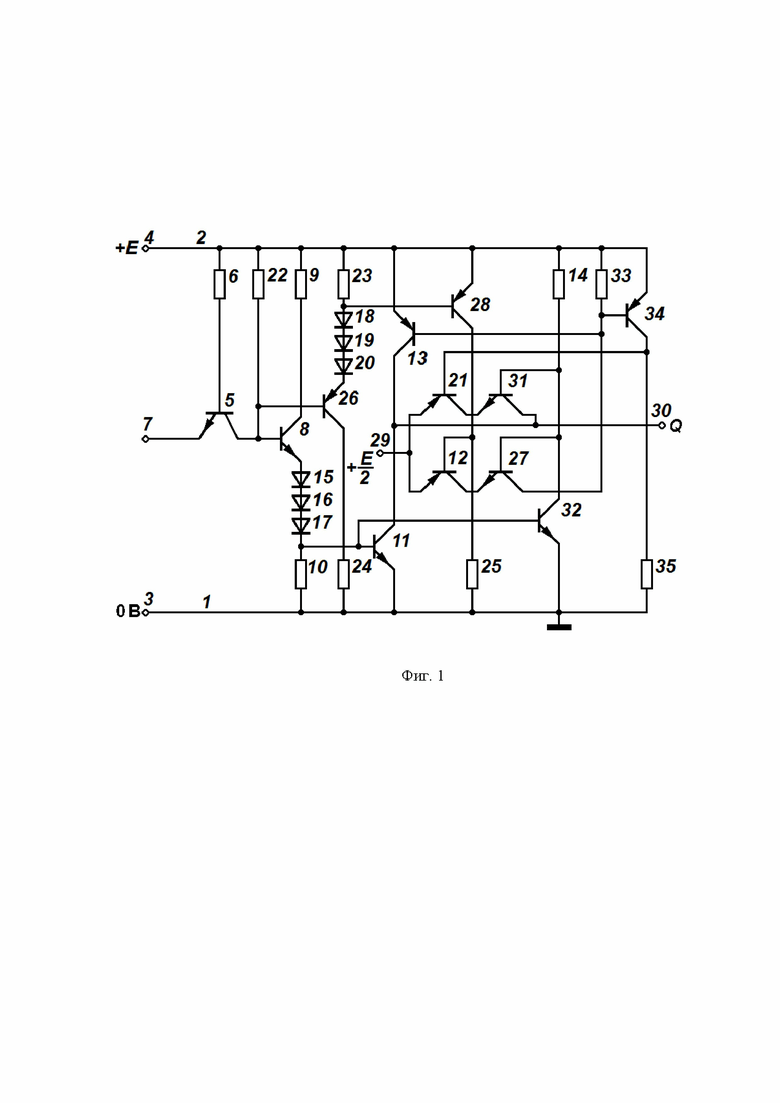

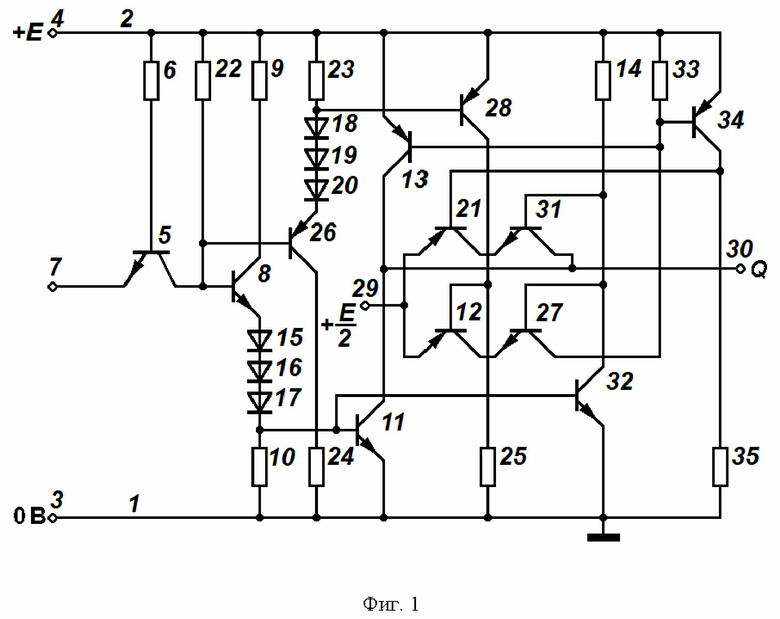

на фиг. 1 представлена принципиальная электрическая схема ЛЭ правой циклической инверсии троичной транзисторно-транзисторной логики;

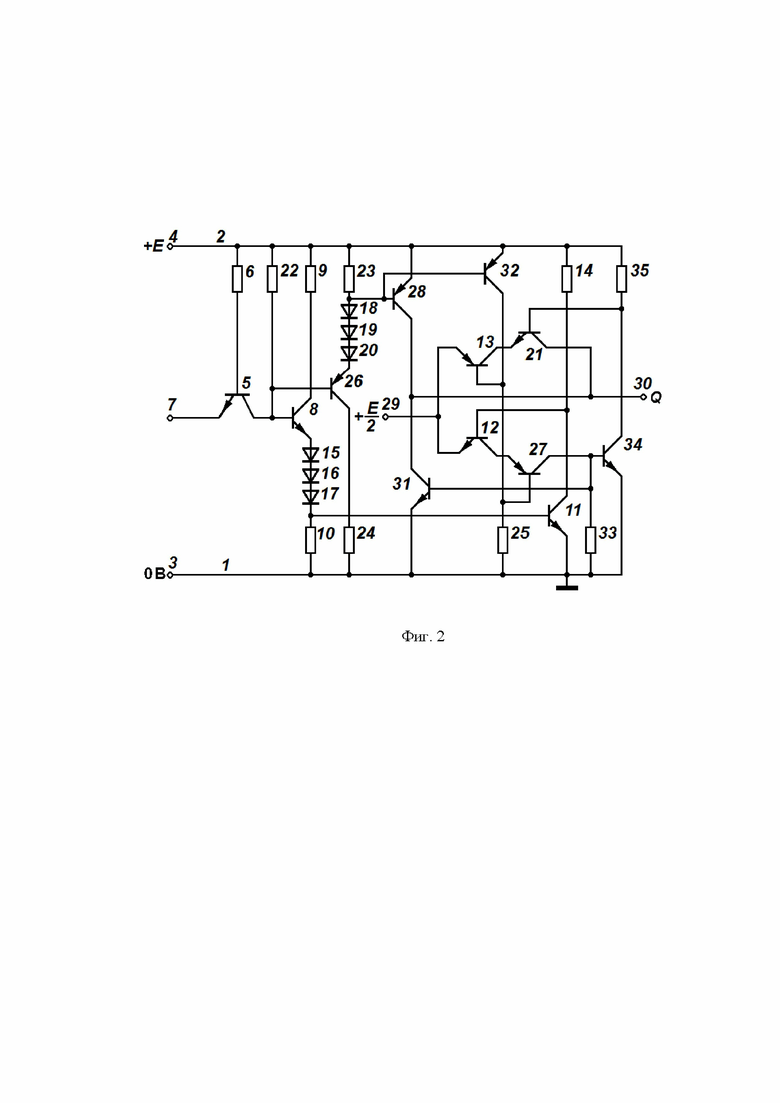

на фиг. 2 приведена принципиальная электрическая схема ЛЭ левой циклической инверсии троичной транзисторно-транзисторной логики;

на фиг. 3 представлены осциллограммы сигналов, иллюстрирующие принцип работы ЛЭ правой циклической инверсии троичной транзисторно-транзисторной логики;

на фиг. 4 представлены осциллограммы сигналов, иллюстрирующие принцип работы ЛЭ левой циклической инверсии троичной транзисторно-транзисторной логики.

На фиг. 1, фиг. 2 введены следующие обозначения:

1 - общая шина;

2 - шина источника положительного напряжения питания;

3, 4 - выводы питания;

5 - МЭТ;

6 - резистор, ограничивающий ток;

7 - входной контакт;

8 - транзистор n-p-n-типа (эмиттерный повторитель);

9 - первый нагрузочный резистор;

10 - второй нагрузочный резистор;

11 - транзистор ключевой p-n-p-типа;

12, 13 - транзисторы ключевые;

14 - нагрузочный резистор;

15÷20 - диоды;

21 - транзистор ключевой;

22÷25 - резисторы

26 - транзистор p-n-p-типа (эмиттерный повторитель);

27, 28 - транзисторы ключевые;

29 - дополнительный вывод питания;

30 - выходной контакт логического элемента;

31, 32 - транзисторы ключевые;

33 - нагрузочный резистор;

34 - транзистор ключевой;

35 - нагрузочный резистор.

Осуществление изобретения

Логический элемент правой циклической инверсии троичной транзисторно-транзисторной логики содержит общую шину 1, шину источника положительного напряжения питания 2, соединенные с одноименными выводами питания 3, 4, МЭТ 5, база которого соединена через резистор 6, ограничивающий ток, с шиной источника положительного напряжения питания 2, а единственный эмиттер - с входным контактом ЛЭ 7, в коллекторную цепь МЭТ 5 включен нагрузочный резистор 22, обеспечивающий базовый ток второго транзистора 8, подключенного базовым выводом к коллектору МЭТ 5, в ситуации, когда на эмиттер МЭТ 5 подан высокий потенциал сигнала логической «1», и ток коллектора сравнительно мал. Коллектор второго транзистора 8 через нагрузочный резистор 9 соединен с шиной источника положительного напряжения 2, а эмиттер - с общей шиной 1 через диоды 15÷17 и второй нагрузочный резистор 10. Резистор 9 при этом имеет сравнительно небольшую величину, и в его функцию входит ограничение коллекторного тока транзистора 8 при открытии третьего транзистора 11, база которого подключена к верхнему по схеме выводу резистора 10. Диоды 15÷21 обеспечивают порог включения транзистора 11, при уровне входного сигнала примерно +2•E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нем равном примерно 0,5÷0,6 В. Коллектор транзистора 11, соединяется с выходным контактом 30 (Q) логического элемента, обеспечивая подачу на выход Q потенциала общей шины 1, что соответствует логическому уровню «-1». К верхнему по схеме выводу резистора 10 подключена также база транзистора 32. Резистор 14, подключенный к коллектору транзистора 32 и к шине источника положительного напряжения питания 2, представляет собой коллекторную нагрузку транзистора 32 и цепь смещения подключенного к нему выводом базы транзистора 31, входящего в состав ключа, коммутирующего на выходной контакт 30 логического элемента совместно с транзистором 21, внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 21. Резистор 14 также обеспечивает цепь смещения подключенного к нему выводом базы транзистора 27, входящего совместно с транзистором 12 в состав ключа, коммутирующего на нагрузку в виде резистора 33, подключенного к шине источника положительного напряжения питания 2, внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 12. Внешнее напряжение +E / 2 легко получить из положительного напряжения питания +E с помощью внешнего низкоомного делителя или специальной схемы, создающей так называемый потенциал средней точки.

К нижнему по схеме выводу резистора 33 выводом базы подключается транзистор 13, вывод эмиттера которого соединен с шиной источника положительного напряжения питания 2, а коллектор соединяется с выходным контактом 30 (Q) логического элемента, обеспечивая подачу на выход Q потенциала шины источника положительного напряжения питания 2, что соответствует логическому уровню «+1». К нижнему по схеме выводу резистора 33 выводом базы подключается также транзистор 34, в коллекторную цепь которого включен нагрузочный резистор 35 относительно общей шины 1. Резистор 35, подключенный также к базе транзистора 21, представляет собой его цепь смещения, позволяющую транзистору 21 совместно с транзистором 31 коммутировать на выходной контакт 30 логического элемента внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 21.

Базовым выводом к коллектору МЭТ 5 подключен также транзистор 26 типа p-n-p, коллектор которого через токоограничивающий резистор 24 соединен с общей шиной 1, а эмиттер - с источником положительного напряжения питания 2 через диоды 18÷20 и нагрузочный резистор 23, к нижнему по схеме выводу которого своим базовым выводом транзистор 28 также p-n-p-типа. Диоды 18÷20 обеспечивают порог включения транзистора 28, при уровне входного сигнала примерно +E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нем равном примерно 0,5÷0,6 В. Коллектор транзистора 28 соединяется с резистором 25, подключенным к общей шине 1. Резистор 25 представляет собой коллекторную нагрузку транзистора 28 и цепь смещения подключенного к нему выводом базы транзистора 12, входящего в состав ключа, коммутирующего на нагрузочный резистор 33 совместно с транзистором 27, внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 12.

Логический элемент правой циклической инверсии троичной транзисторно-транзисторной логики работает следующим образом.

При подаче на вход 7 ЛЭ, а, следовательно, и на эмиттер МЭТ 5 высокого потенциала сигнала логической «+1», переход эмиттер-база этого транзистора закрыт, а переход коллектор-база МЭТ 5 открыт приложенным в прямом направлении положительным напряжением источника питания через резистор 6, ограничивающий ток базы. Ток коллекторного перехода МЭТ 5, складываясь с током, протекающим через резистор 22, проходя через переход эмиттер-база транзистора 8, максимально открывает этот транзистор. Поскольку транзистор 8 включен по схеме эмиттерного повторителя, его входное сопротивление велико, и поэтому ток, протекающий через резистор 22, мал, тем более что этот резистор шунтируется прямосмещенным переходом коллектор-база МЭТ 5. Следовательно, к базе транзистора 8 приложено практически полное напряжение питания с шины 2, которое для микросхем ТТЛ составляет +5 В. С учетом падения напряжения на токоограничивающем резисторе 9 и насыщенном транзисторе 8, напряжение на его эмиттере составит примерно 5 В - (0,8…1 В) = 4,2…4 В. Этого напряжения достаточно, чтобы открыть три диода 15÷17, падение напряжения на которых составляет примерно 3⋅(0,5÷0,6 В) = 1,5÷1,8 В, и подать высокий потенциал напряжения на базу транзистора 11. Этот высокий потенциал обеспечивает ток перехода база-эмиттер транзистора 11, открывает его и переводит в режим насыщения, в результате чего на выходе 30 ЛЭ появляется потенциал низкого уровня, соответствующий логическому сигналу «-1». Таким образом ЛЭ правой циклической инверсии осуществляет преобразование «+1» → «-1».

Напряжение с верхнего по схеме вывода резистора 10 поступает также на базу транзистора 32, обеспечивая ток перехода база-эмиттер, открывает его и переводит в режим насыщения, в результате чего на нижнем по схеме выводе резистора 14 также появляется потенциал низкого уровня, поступающий на базы транзисторов 27 и 31, запирая сдвоенные ключи, в состав которых эти транзисторы входят.

Если же на входе 7 ЛЭ, а, следовательно, и на эмиттере МЭТ 5 действует потенциал низкого уровня, соответствующий логическому сигналу «-1», он открывает его переход база-эмиттер, в результате чего МЭТ 5 находится в режиме насыщения, и потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, окажется близким к потенциалу общей шины. В силу того что транзисторы 8 и 26 действуют в противофазе, транзистор 8 закрыт, а транзистор 26 насыщен и открыт. Следовательно, ключи на транзисторах 11 и 32 оказываются закрытыми, а ключ на транзисторе 28 - насыщен и открыт, в результате чего на верхнем по схеме выводе резистора 25 появляется потенциал высокого уровня, который закрывает транзистор 12 сдвоенного ключа, и на нижнем по схеме выводе резистора 33 действует потенциал шины источника положительного напряжения питания 2. Этот потенциал запирает ключи на транзисторах 13 и 34, а поскольку заперт и ключ на транзисторе 32, то через резисторы базового смещения 35 и 14 начинают протекать токи базы транзисторов 21 и 31 соответственно, что приводит к насыщению этих транзисторов, следовательно, сдвоенный ключ на их основе открывается и пропускает на выход 30 (Q) ЛЭ внешнее напряжение +E / 2, соответствующее логическому «0», с вывода 29, соединенного с эмиттером транзистора 21. Таким образом осуществляется преобразование «-1» → «0».

Рассмотрим ситуацию, когда на входе 7 ЛЭ правой циклической инверсии, а, следовательно, и на единственном эмиттере МЭТ 5 действует потенциал уровня +E / 2, соответствующий логическому сигналу «0».

Потенциал уровня +E / 2, на эмиттере МЭТ 5 ниже потенциала +E на его базе, следовательно, переход база-эмиттер МЭТ 5 будет открыт, МЭТ 5 в результате этого войдет в режим насыщения, и потенциал на его коллекторе будет превышать потенциал +E / 2, примерно на 0,2 В. Этот потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, не позволит каждому из них открыть диоды 15÷17 и 18÷20 в своих эмиттерных цепях, поскольку напряжение на эмиттерах с учетом падения напряжения на токоограничивающих резисторах 9 и 24 примерно на 0,8…1 В меньше потенциала на базах. Следовательно, ключи на транзисторах 11, 32 и 28 окажутся запертыми потенциалами, подаваемыми на их базы через резисторы 10 и 23 с общей шины 1 и шины источника положительного напряжения 2. Это приведет к тому, что через резисторы базового смещения 25 и 14 начнут протекать токи базы транзисторов 12 и 27 соответственно, что приводит к насыщению этих транзисторов. Сдвоенный ключ на их основе открывается и подключает нижний по схеме вывод резистора 33 к потенциалу +E / 2 с вывода 29, соединенного с эмиттером транзистора 12. Этот потенциал откроет одновременно ключи на транзисторах 13 и 34, последний из которых закроет напряжением высокого уровня с шины источника положительного напряжения питания 2 транзистор 21 сдвоенного ключа, а, следовательно, и сам сдвоенный ключ на транзисторах 21 и 31.

В это же время открытый ключ на транзисторе 13 подаст напряжение высокого уровня с шины источника положительного напряжения питания 2, соответствующее сигналу логической «+1», на выход 30 (Q). Так ЛЭ правой циклической инверсии осуществляет преобразование «0» → «+1».

Логический элемент левой циклической инверсии троичной транзисторно-транзисторной логики устроен фактически симметрично элементу правой циклической инверсии относительно уровня +E / 2. Он содержит общую шину 1, шину источника положительного напряжения питания 2, соединенные с одноименными выводами питания 3, 4, МЭТ 5, база которого соединена через резистор 6, ограничивающий ток, с шиной источника положительного напряжения питания 2, а единственный эмиттер - с входным контактом ЛЭ 7, в коллекторную цепь МЭТ 5 включен нагрузочный резистор 22, обеспечивающий базовый ток второго транзистора 8, подключенного базовым выводом к коллектору МЭТ 5, в ситуации, когда на эмиттер МЭТ 5 подан высокий потенциал сигнала логической «1», и ток коллектора сравнительно мал. Коллектор второго транзистора 8 через нагрузочный резистор 9 соединен с шиной источника положительного напряжения 2, а эмиттер - с общей шиной 1 через диоды 15÷17 и второй нагрузочный резистор 10. Резистор 9 при этом имеет сравнительно небольшую величину, и в его функцию входит ограничение коллекторного тока транзистора 8 при открытии третьего транзистора 11, база которого подключена к верхнему по схеме выводу резистора 10. Диоды 15÷21 обеспечивают порог включения транзистора 11, при уровне входного сигнала примерно +2⋅E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нем равном примерно 0,5÷0,6 В. Коллектор транзистора 11, соединяется с шиной источника положительного напряжения 2 через нагрузочный резистор 14, обеспечивая подключение его нижнего по схеме вывода к потенциалу общей шины 1, что соответствует логическому уровню «-1». К нижнему по схеме выводу резистора 14 подключена также база транзистора 12, для которого резистор 14, представляет собой цепь смещения. Транзистор 12 совместно с транзистором 27 входит в состав ключа, коммутирующего на нагрузочное сопротивление 33 внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 12. Резистор 33 также обеспечивает запирание подключенного к нему выводом базы транзистора 31, подающего через коллекторный вывод на выходной контакт 30 (Q) логического элемента общей шины 1, что соответствует логическому уровню «-1».

К верхнему по схеме выводу резистора 33 своим выводом базы подключен также транзистор 34, обеспечивающий коммутацию через вывод коллектора подключенной к его эмиттеру общей шины 1 с нижним по схеме выводом резистора 35, включенного в его коллекторную цепь в качестве нагрузки относительно шины источника положительного напряжения 2. Резистор 35 представляет собой также цепь смещения подключенного к нему выводом базы транзистора 21, входящего в состав ключа, коммутирующего на выходной контакт 30 логического элемента совместно с транзистором 13, внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 13.

Базовым выводом к коллектору МЭТ 5 подключен также транзистор 26 типа p-n-p, коллектор которого через токоограничивающий резистор 24 соединен с общей шиной 1, а эмиттер - с источником положительного напряжения питания 2 через диоды 18÷20 и нагрузочный резистор 23, к нижнему по схеме выводу которого своим базовым выводом транзистор 28 также p-n-p-типа. Диоды 18÷20 обеспечивают порог включения транзистора 28, при уровне входного сигнала примерно +E / 3 В, благодаря тому, что каждый из диодов начинает проводить ток при падении напряжения на нем равном примерно 0,5÷0,6 В. Коллектор транзистора 28 соединяется с выходным контактом 30 (Q) логического элемента, обеспечивая подачу со своего эмиттера на выход Q потенциала шины источника положительного напряжения питания 2, что соответствует логическому уровню «+1».

К нижнему по схеме выводу резистора 23 подключен своим базовым выводом транзистор 32 p-n-p-типа, в коллекторную цепь которого включен нагрузочный резистор 25, подключенным к общей шине 1. Резистор 25 представляет собой коллекторную нагрузку транзистора 32 и цепь смещения подключенного к нему выводом базы транзистора 13, входящего в состав ключа, коммутирующего на выход Q (контакт 30) совместно с транзистором 21, внешнее напряжение +E / 2, поступающее на вывод 29, соединенный с эмиттером транзистора 13.

Логический элемент левой циклической инверсии троичной транзисторно-транзисторной логики работает следующим образом.

При подаче на вход 7 ЛЭ, а, следовательно, и на эмиттер МЭТ 5 высокого потенциала сигнала логической «+1», переход эмиттер-база этого транзистора закрыт, а переход коллектор-база МЭТ 5 открыт приложенным в прямом направлении положительным напряжением источника питания через резистор 6, ограничивающий ток базы. Ток коллекторного перехода МЭТ 5, складываясь с током, протекающим через резистор 22, проходя через переход эмиттер-база транзистора 8, максимально открывает этот транзистор. Поскольку транзистор 8 включен по схеме эмиттерного повторителя, его входное сопротивление велико, и поэтому ток, протекающий через резистор 22, мал, тем более что этот резистор шунтируется прямосмещенным переходом коллектор-база МЭТ 5. Следовательно, к базе транзистора 8 приложено практически полное напряжение питания с шины 2, которое для микросхем ТТЛ составляет +5 В. С учетом падения напряжения на токоограничивающем резисторе 9 и насыщенном транзисторе 8, напряжение на его эмиттере составит примерно 5 В - (0,8…1 В) = 4,2…4 В. Этого напряжения достаточно, чтобы открыть три диода 15÷17, падение напряжения на которых составляет примерно 3⋅(0,5÷0,6 В) = 1,5÷1,8 В, и подать высокий потенциал напряжения на базу транзистора 11. Этот высокий потенциал обеспечивает ток перехода база-эмиттер транзистора 11, открывает его и переводит в режим насыщения, в результате чего на верхнем по схеме выводе резистора 14 появляется потенциал низкого уровня с общей шины 1, который закрывает транзистор 12 сдвоенного ключа, и на верхнем по схеме выводе резистора 33 действует потенциал общей шины 1. Этот потенциал запирает ключи на транзисторах 31 и 34. В силу того что транзисторы 8 и 26 действуют в противофазе, транзистор 26 не может открыть ключи на транзисторах 28 и 32, закрытые по базам через резистор 23 высоким потенциалом с шины источника положительного напряжения питания 2. В результате через резисторы базового смещения 25 и 35 начинают протекать токи базы транзисторов 13 и 21 соответственно, что приводит к насыщению этих транзисторов. Следовательно, сдвоенный ключ на их основе открывается и пропускает на выход 30 (Q) ЛЭ внешнее напряжение +E / 2, соответствующее логическому «0», с вывода 29, соединенного с эмиттером транзистора 13. Таким образом осуществляется преобразование «+1» → «0».

Если же на входе 7 ЛЭ, а, следовательно, и на эмиттере МЭТ 5 действует потенциал низкого уровня, соответствующий логическому сигналу «-1», он открывает его переход база-эмиттер, в результате чего МЭТ 5 находится в режиме насыщения, и потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, окажется близким к потенциалу общей шины. Поскольку транзисторы 8 и 26 действуют в противофазе, транзистор 8 будет закрыт, а транзистор 26 насыщен и открыт, в результате чего ключ на транзисторе 11 окажется закрытым, а ключи на транзисторах 28 и 32 - насыщены и открыты, в результате чего на верхнем по схеме выводе резистора 25 появляется потенциал высокого уровня, который закрывает транзистор 13 сдвоенного ключа, и сам сдвоенный ключ. Потенциал высокого уровня с верхнего по схеме выводе резистора 25 закрывает также транзистор 27 сдвоенного ключа и сам сдвоенный ключ на транзисторах 27 и 12, что приводит к закрытию транзисторных ключей 31 и 34 через резистор 33 потенциалом низкого уровня с общей шины 1. В итоге лишь открытый ключ на транзисторе 28 подаст напряжение высокого уровня с шины источника положительного напряжения питания 2, соответствующее сигналу логической «+1», на выход 30 (Q). Так ЛЭ левой циклической инверсии осуществляет преобразование «-1» → «+1».

Когда на входе 7 ЛЭ левой циклической инверсии, а, следовательно, и на единственном эмиттере МЭТ 5 действует потенциал уровня +E / 2, соответствующий логическому сигналу «0», потенциал уровня +E / 2, на эмиттере МЭТ 5 ниже потенциала +E на его базе, следовательно, переход база-эмиттер МЭТ 5 будет открыт. МЭТ 5 в результате этого войдет в режим насыщения, и потенциал на его коллекторе будет превышать потенциал +E / 2, примерно на 0,2 В. Этот потенциал на базах транзисторов 8 и 26, включенных по схеме эмиттерных повторителей, не позволит каждому из них открыть диоды 15÷17 и 18÷20 в своих эмиттерных цепях, поскольку напряжение на эмиттерах с учетом падения напряжения на токоограничивающих резисторах 9 и 24 примерно на 0,8…1 В меньше потенциала на базах. Следовательно, ключи на транзисторах 28, 32 и 11 окажутся запертыми потенциалами, подаваемыми на их базы через резисторы 23 и 10 с шины источника положительного напряжения 2 и общей шины 1 соответственно. Это приведет к тому, что через резисторы базового смещения 14 и 25 начнут протекать токи базы транзисторов 12 и 27 соответственно, что приводит к насыщению этих транзисторов. Следовательно, сдвоенный ключ на их основе открывается и подключает верхний по схеме вывод резистора 33 к потенциалу +E / 2 с вывода 29, соединенного с эмиттером транзистора 12. Этот потенциал откроет одновременно ключи на транзисторах 31 и 34, последний из которых закроет напряжением низкого уровня с общей шины 1 транзистор 21 сдвоенного ключа, а, следовательно, и сам сдвоенный ключ на транзисторах 21 и 13.

В это же время открытый ключ на транзисторе 31 подаст напряжение низкого уровня с общей шины 1, соответствующее сигналу логической «-1», на выход 30 (Q). Так ЛЭ левой циклической инверсии осуществляет преобразование «0» → «-1».

С целью апробации в пакете схемотехнического моделирования (Карлащук В.И. Электронная лаборатория на IBM PC. Программа Electronics Workbench и ее применение. - М.: СОЛОН-Пресс, 2016. - 726 c.) были разработаны модели заявляемых устройств на основе SPICE-моделей биполярных транзисторов, соответствующих распространенным отечественным полупроводниковым триодам типа КТ3102, КТ3107, и исследованы свойства логических элементов при подаче на вход 7 пилообразного напряжения амплитудой 2,5 В и постоянной составляющей 2,5 В.

Результаты исследования представлены на фиг. 3 и фиг. 4. На фиг. 3 изображены осциллограммы входного сигнала (A) и сигнала на выходе (Q) ЛЭ правой циклической инверсии. Очевидно, что на выходе 30 (Q) ЛЭ формировался трехуровневый сигнал, соответствующий правилу преобразования входных логических уровней: «+1»→«-1»; «-1»→«0»; «0»→«+1», что подтверждает работоспособность заявляемой схемы (фиг. 1).

Осциллограммы на фиг. 4 иллюстрируют форму входного сигнала (A) и сигнала на выходе (Q) ЛЭ левой циклической инверсии. Согласно осциллограммам, на выходе 30 (Q) ЛЭ формировался трехуровневый сигнал, соответствующий правилу преобразования входных логических уровней: «+1»→«0»; «0»→«-1»; «-1»→«+1», что подтверждает работоспособность заявляемой схемы (фиг. 2).

Таким образом, при подаче на входы 7 ЛЭ потенциалов, соответствующих троичным логическим уровням «-1», «0», «+1», они работают в соответствии с таблицей истинности 1.

Таблица 1

Х

О

Д

А

Таким образом, продемонстрирована работоспособность заявляемых базовых элементов троичной транзисторно-транзисторной логики - троичных циклических инверторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Быстродействующий микромощный логический элемент и-или/и-или-не | 1977 |

|

SU624369A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Элемент троичной логики | 1984 |

|

SU1262694A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Элемент троичной логики | 1984 |

|

SU1262695A1 |

| Элемент транзисторно-транзисторной логики | 1986 |

|

SU1336225A1 |

| Транзисторно-транзисторный логический элемент "и-или-не | 1977 |

|

SU790331A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2016 |

|

RU2618901C1 |

Группа изобретений относится к автоматике, к цифровой вычислительной технике и предназначена для построения логических элементов (ЛЭ) транзисторно-транзисторной логики (ТТЛ), реализующих функции троичной циклической инверсии. Техническим результатом группы изобретений является повышение производительности логических элементов троичной транзисторно-транзисторной логики и расширение их функциональных возможностей. Логический элемент циклической инверсии троичной транзисторно-транзисторной логики содержит общую шину и шину источника положительного напряжения, соединенные с одноименными выводами питания, входной каскад на основе многоэмиттерного транзистора (МЭТ) и выходной инвертирующий каскад. Схемотехнически выходной каскад выполнен таким образом, что он способен формировать на выходе ЛЭ троичные логические уровни, соответствующие функциям циклической инверсии, из выходных сигналов входного каскада на основе МЭТ. 2 н.п. ф-лы, 4 ил., 1 табл.

1. Логический элемент правой циклической инверсии троичной транзисторно-транзисторной логики, характеризующийся тем, что содержит общую шину (1) и шину источника положительного напряжения (2), соединенные с одноименными выводами питания (3, 4),

входной каскад, включающий многоэмиттерный транзистор (5), единственный вывод эмиттера которого соединен с входным контактом (7), база и коллектор транзистора (5) через резистор (6) и резистор (22) соответственно соединены с одной из шин,

выходной каскад, включающий транзисторы (8, 11, 12, 13, 21, 26, 27, 28, 31, 32, 34), резисторы (9, 10, 14, 23, 24, 25, 33, 35) и группы последовательно соединенных диодов (15-17) и (18-20), а также дополнительный вывод питания (29),

при этом база транзистора (8) соединена с коллектором транзистора (5), коллектор транзистора (8) через токоограничивающий резистор (9) соединен с шиной источника положительного напряжения (2), а эмиттер транзистора (8) через группу диодов (15-17) и нагрузочный резистор (10) соединен с общей шиной (1),

база транзистора (26) типа p-n-p соединена с коллектором транзистора (5), коллектор транзистора (26) через токоограничивающий резистор (24) соединен с общей шиной (1), эмиттер транзистора (26) через группу диодов (18-20) и резистор (23) соединен с шиной источника положительного напряжения (2),

база транзистора (11) через резистор (10) подключена к общей шине (1) и диоду (17), коллектор транзистора (11) соединен с выходным контактом (30) логического элемента, эмиттер транзистора (11) соединен с общей шиной (1),

база транзистора (32) через резистор (10) подключена к общей шине (1) и диоду (17), коллектор транзистора (32) соединен с базами транзисторов (27 и 31), а через резистор (14) - с шиной источника положительного напряжения (2), эмиттер транзистора (32) соединен с общей шиной (1),

база транзистора (27) через резистор (14) подключена к шине источника положительного напряжения питания (2) и к коллектору транзистора (32), коллектор транзистора (27) подключен к базе транзистора (34), а через резистор (33) - к шине источника положительного напряжения питания (2), эмиттер транзистора (27) соединен с коллектором транзистора (12), база которого соединена с общей шиной (1) через резистор (25) и с коллектором транзистора (28), эмиттер транзистора (12) соединен с дополнительным выводом питания (29),

база транзистора (31) через резистор (14) подключена к шине источника положительного напряжения питания (2) и к коллектору транзистора (32), коллектор транзистора (31) соединен с выходным контактом (30) логического элемента, а эмиттер транзистора (31) соединен с коллектором транзистора (21), база которого соединена с общей шиной (1) через резистор (35) и с коллектором транзистора (34), эмиттер транзистора (21) соединен с дополнительным выводом питания (29),

базовый вывод транзистора 28 p-n-p–типа через резистор (23) подключен к шине источника положительного напряжения питания (2) и к диоду (18), коллектор транзистора (28) соединен с базой транзистора (12), а через резистор (25) - с общей шиной (1), эмиттер транзистора (28) соединен с шиной источника положительного напряжения (2),

эмиттер транзистора (13) подключен к шине источника положительного напряжения (2), базовый вывод транзистора (13) соединен с коллектором транзистора (27), а через резистор (33) - с шиной источника положительного напряжения (2), коллектор транзистора (13) соединен с выходным контактом (30) логического элемента,

с коллектором транзистора (27), а через резистор (33) - с шиной источника положительного напряжения (2) соединена также база транзистора (34), эмиттер которого соединен с шиной источника положительного напряжения (2), а коллектор - через резистор (35) подключен к общей шине (1) и к базе транзистора (21).

2. Логический элемент левой циклической инверсии троичной транзисторно-транзисторной логики, характеризующийся тем, что содержит общую шину (1) и шину источника положительного напряжения (2), соединенные с одноименными выводами питания (3, 4),

входной каскад, включающий многоэмиттерный транзистор (5), единственный вывод эмиттера которого соединен с входным контактом (7), база и коллектор транзистора (5) через резистор (6) и резистор (22) соответственно соединены с одной из шин,

выходной каскад, включающий транзисторы (8, 11, 12, 13, 21, 26, 27, 28, 31, 32, 34), резисторы (9, 10, 14, 23, 24, 25, 33, 35) и группы последовательно соединенных диодов (15-17) и (18-20), а также дополнительный вывод питания (29),

при этом база транзистора (8) соединена с коллектором транзистора (5), коллектор транзистора (8) через токоограничивающий резистор (9) соединен с шиной источника положительного напряжения (2), а эмиттер транзистора (8) через группу диодов (15-17) и нагрузочный резистор (10) соединен с общей шиной (1),

база транзистора (26) типа p-n-p соединена с коллектором транзистора (5), коллектор транзистора (26) через токоограничивающий резистор (24) соединен с общей шиной (1), эмиттер транзистора (26) через группу диодов (18-20) и резистор (23) соединен с шиной источника положительного напряжения (2),

база транзистора (11) через резистор (10) подключена к общей шине (1) и диоду (17), коллектор транзистора (11) соединен с базой транзистора (12) и через резистор (14) - с шиной источника положительного напряжения (2), эмиттер транзистора (11) соединен с общей шиной (1),

база транзистора (28) p-n-p–типа через резистор (23) подключена к шине источника положительного напряжения (2) и диоду (18), коллектор транзистора (28) соединен с выходным контактом (30) логического элемента, эмиттер транзистора (28) соединен с шиной источника положительного напряжения (2),

база транзистора (32) p-n-p–типа через резистор (23) подключена к шине источника положительного напряжения (2) и диоду (18), коллектор транзистора (32) соединен с базами транзисторов (13 и 27), а через резистор (25) - с общей шиной (1), эмиттер транзистора (32) соединен с шиной источника положительного напряжения (2),

база транзистора (27) через резистор (25) подключена к общей шине (1) и к коллектору транзистора (32), коллектор транзистора (27) подключен к базе транзистора (34) и через резистор (33) - к общей шине (1), а эмиттер транзистора (27) соединен с коллектором транзистора (12), база которого соединена с шиной источника положительного напряжения питания (2) через резистор (14) и с коллектором транзистора (11), эмиттер транзистора (12) соединен с дополнительным выводом питания (29),

база транзистора (34) через резистор (33) подключена к общей шине (1) и к коллектору транзистора (27), коллектор транзистора (34) подключен к базе транзистора (21) и через резистор (35) - к шине источника положительного напряжения питания (2), а эмиттер транзистора (34) соединен с общей шиной (1),

базовый вывод транзистора (31) через резистор (33) подключен к общей шине (1) и к коллектору транзистора (27), эмиттер транзистора (31) соединён с общей шиной (1), а коллектор транзистора (31) соединен с выходным контактом (30) логического элемента,

базовый вывод транзистора (21) через резистор (35) подключен к шине источника положительного напряжения питания (2) и к коллектору транзистора (34), коллектор транзистора (21) соединен с выходным контактом (30) логического элемента, а эмиттер - с коллектором транзистора (13), база которого подключена к коллектору транзистора (32) и к общей шине (1) - через резистор (25), эмиттер транзистора (13) соединен с дополнительным выводом питания (29).

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Элемент троичной логики | 1984 |

|

SU1262694A1 |

| Элемент троичной логики | 1984 |

|

SU1262695A1 |

| US 4107549 A, 15.08.1978 | |||

| Устройство для изготовления пружин | 1988 |

|

SU1563821A2 |

| US 10169617 B2, 01.01.2019. | |||

Авторы

Даты

2025-03-03—Публикация

2024-10-03—Подача