Известны устройства для автоматической коррекции нелинейности измерительного канала, содержащие счетчик импульсов, дешифратор числа поправок, триггер прибавления поправки, триггер вычитания поправки, логиЧеские схемы «И, «ИЛИ и клапаны. - Предложенное устройство отличается тем. Что содержит дешифратор числа дискретных участков коррекции и коммутаторы, причем выходы дешифратора -числа поправок через коммутаторы и одну из схем «ИЛИ связаны с первыми входами схем «И, вторые входы которых соединены с дешифратором числа дискретных участков коррекции, а выходы связаны через другую схему «ИЛИ с первым установочным входом триггера вычитания поправки, второй вход которого связан с выходам первого клапана и входом второго, а выход - с первым клапаном.

Выходы схем «И через коммутатор соединены со входами другой схемы «ИЛИ, связанной с одним установочным входом триггера прибавления поправки, а его выход соединен через второй клапан с другим своим установочным входом. Это позволяет увеличить точность коррекции .нелинейности, расширить возможности и увеличить гибкость при введении поправок в устройство.

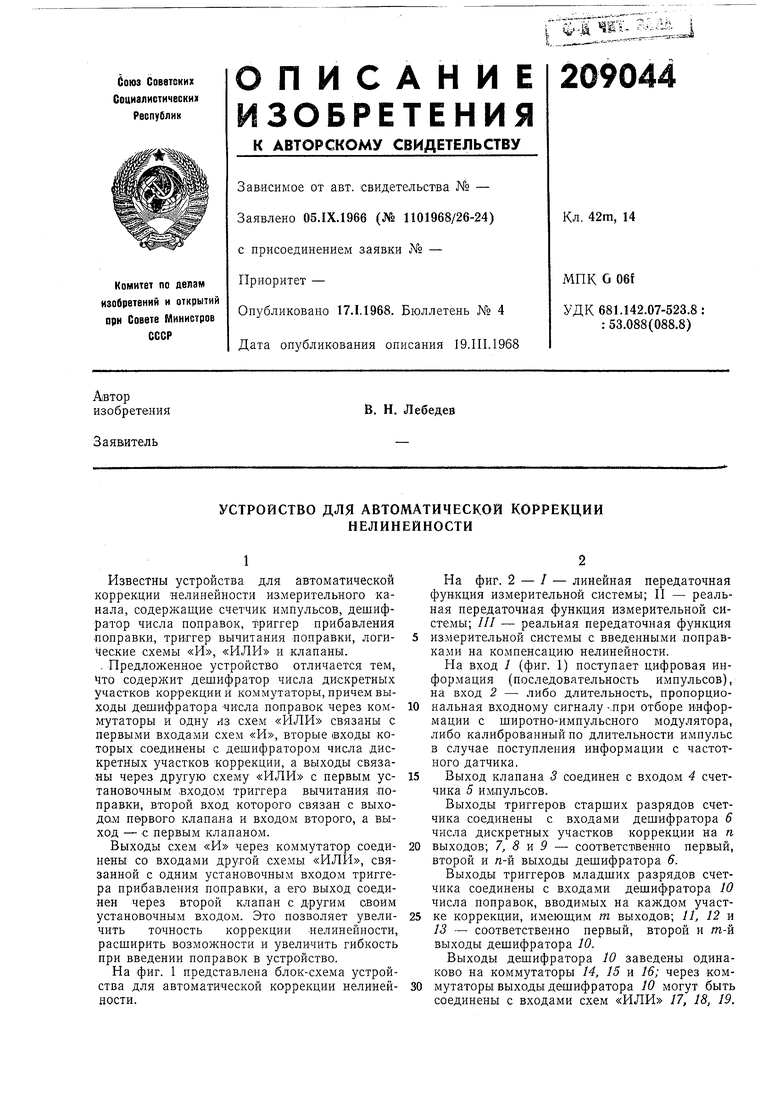

На фиг. 2 - / - линейная передаточная функция измерительной системы; II - реальная передаточная функция измерительной системы; /// - реальная передаточная функция измерительной системы с введенными поправками на компенсацию нелинейности.

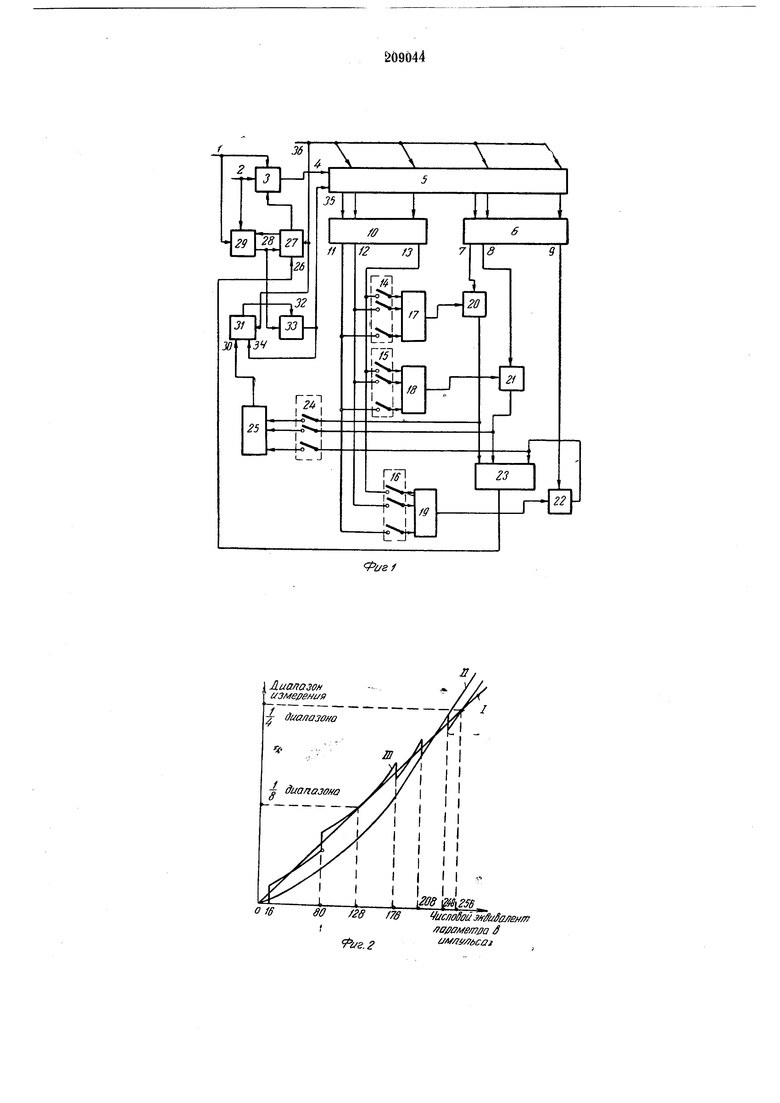

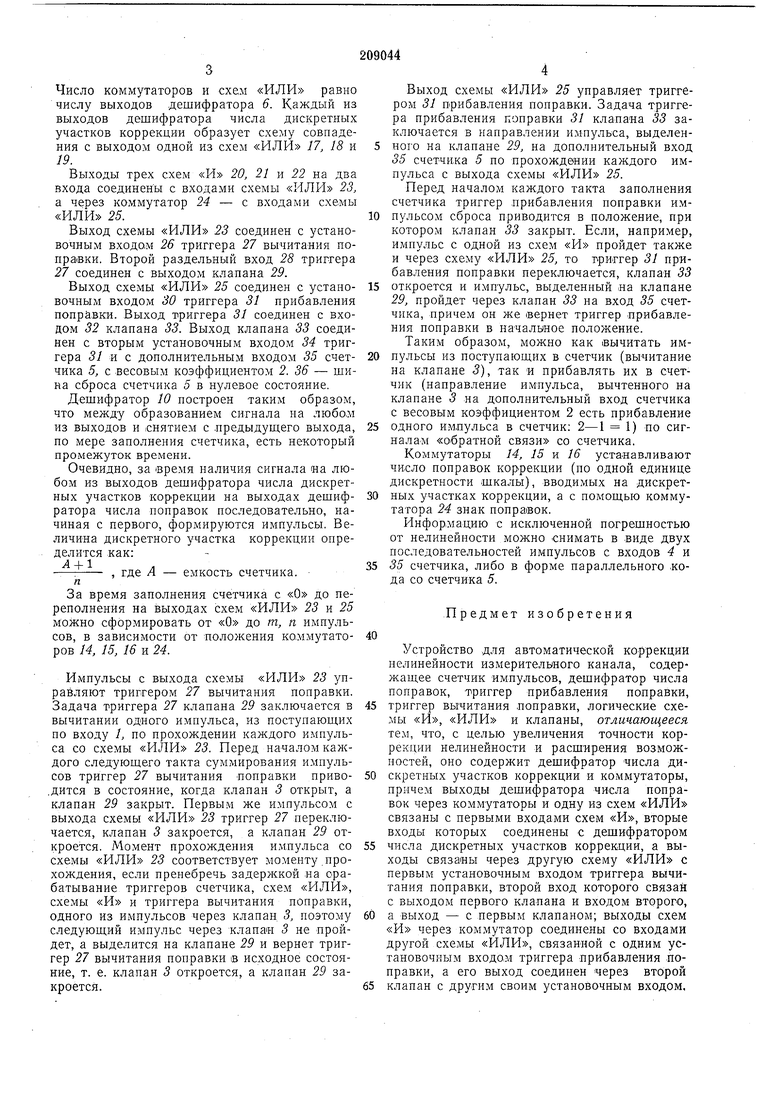

На вход 1 (фиг. 1) поступает цифровая информация (последовательность импульсов), на вход 2 - либо длительность, пропорциональная входному сигналу -.при отборе информации с широтно-импульсного модулятора, либо калиброванный по длительности импульс в случае поступления информации с частотного датчика.

Выход клапана 3 соединен с входом 4 счетчика 5 импульсов.

Выходы триггеров старших разрядов счетчика соединены с входами дешифратора 6 числа дискретных участков коррекции на п выходов; 7, 8 Е 9 - соответственно первый, второй и «-Й выходы дешифратора 6.

Выходы триггеров младших разрядов счетчика соединены с входами дешифратора 10 числа поправок, вводимых на каждом участке коррекции, имеюшим т выходов; //, 12 и 13 - соответственно первый, второй и т-й выходы дешифратора 10.

Число коммутаторов и схем «ИЛИ равно числу выходов дешифратора 6. Каждый из выходов дешифратора числа дискретных участков коррекции образует схему совпадения с выходом одной из схем «ИЛИ 17, 18 и 19.

Выходы трех схем «И 20, 21 и 22 на два входа соединены с входами схемы «ИЛИ 23, а через коммутатор 24 - с входами схемы «ИЛИ 25.

Выход схемы «ИЛИ 23 соединен с установочным входом 26 триггера 27 вычитания поиравки. Второй раздельный вход 28 триггера 27 соединен с выходом клапана 29.

Выход схемы «ИЛИ 25 соединен с установочным входом 30 триггера 31 прибавления поправки. Выход триггера 31 соединен с входом 32 клапана 33. Выход клапана 33 соединен с вторым установочным входом 34 триггера 31 и с дополнительным входом 35 счетчика 5, с весовым коэффициентом 2. 36 - шина сброса счетчика 5 в нулевое состояние.

Дешифратор 10 построен таким образом, что между образованием сигнала на любом из выходов и снятием с .предыдущего выхода, по мере заполнения счетчика, есть некоторый промежуток времени.

Очевидно, за Время наличия сигнала иа любом из выходов дешифратора числа дискретных участков коррекции на выходах дешифратора числа поправок последовательно, начиная с первого, формируются импульсы. Величина дискретного участка коррекции определится как:

+ 1,

: , где А - емкость счетчика.

За время заполнения счетчика с «О до переполнения на выходах схем «ИЛИ 23 и 25 можно сформировать от «О до т, п импульсов, в зависимости от -положения ко,ммутаторов 14, 15, 16 и 24.

Импульсы с выхода схемы «ИЛИ 23 управляют триггером 27 вычитания поправки. Задача триггера 27 клапана 29 заключается в вычитании одного импульса, из поступающих по входу /, по прохождении каждого импульса со схемы «ИЛИ 23. Иеред началом каждого следующего такта суммирования импульсов триггер 27 вычитания поправки приво.дится в состояние, когда клапан 3 открыт, а клапан 29 закрыт. Первым же импульсом с выхода схемы «ИЛИ 23 триггер 27 переключается, клапан 3 закроется, а клапан 29 откроется. Момент прохождения импульса со схемы «ИЛИ 23 соответствует моменту.прохождения, если пренебречь задержкой на срабатывание триггеров счетчика, схем «ИЛИ, схемы «И и триггера вычитания поправки, одного из импульсов через клапан 3, поэтому следующий импульс через клапан 5 не пройдет, а выделится на клапане 29 и вернет триггер 27 вычитания поправки в исходное состояние, т. е. клапан 3 откроется, а клапан 29 закроется.

Выход схемы «ИЛИ 25 управляет триггером 31 прибавления поправки. Задача триггера прибавления поправки 31 клапана 33 заключается в направлении импульса, выделенного на клапане 29, на дополнительный вход 35 счетчика 5 по прохождении каждого импульса с выхода схемы «ИЛИ 25.

Перед началом каждого такта заполнения счетчика триггер лрибавления иоправки импульсом сброса приводится в положение, при котором клапан 33 закрыт. Если, например, имиульс с одной из схем «И пройдет также и через схему «ИЛИ 25, то триггер 31 прибавления поправки переключается, клапан 33

откроется и импульс, выделенный на клапане 29, пройдет через клапан 33 на вход 35 счетчика, причем он же вернет триггер прибавления поправки в начальное положение. Таким образом, можно как вычитать импульсы из поступающих в счетчик (вычитание на клапане 5), так и прибавлять их в счетчик (направление им-иульса, вычтенного на клапане 3 на дополнительный вход счетчика с весовым коэффициентом 2 есть прибавление

одного им.пульса в счетчик; 2-1 1) по сигналам «обратной связи со счетчика.

Коммутаторы 14, 15 и 16 устанавливают число поправок коррекции (по одной единице дискретности шкалы), вводимых на дискретных участках коррекции, а с помощью коммутатора 24 знак поправок.

Информацию с исключенной погрешностью от нелинейности можно снимать в виде двух последовательностей импульсов с входов 4 и

35 счетчика, либо в форме параллельного -кода со счетчика 5.

Предмет изобретения

Устройство для автоматической коррекции нелинейности измерительного канала, содержащее счетчик импульсов, дешифратор числа поправок, триггер прибавления поправки,

триггер вычитания .поправки, логические схемы «И, «ИЛИ и клапаны, отличающееся тем, что, с целью увеличения точности коррекции нелинейности и расширения возможностей, оно содержит дешифратор числа дискретных участков коррекции и коммутаторы, причем выходы дешифратора числа поправок через коммутаторы и одну из схем «ИЛИ связаны с первыми входами схем «И, вторые входы которых соединены с дешифратором

числа дискретных участков коррекции, а выходы связаны через другую схему «ИЛИ с первым установочным входом триггера вычитания поправки, второй вход которого связан с выходом первого клапана и входом второго,

а выход - с первым клапаном; выходы схем «И через коммутатор соединены со входами другой схемы «ИЛИ, связанной с одним установочным входо,м триггера прибавления поправки, а его выход соединен через второй

Ч

36

35

ft

(2 f3

32

31

33

Г«1

А

/7

/8

еЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Система управления клапанами газораспределения с электрогидравлическим приводом | 1981 |

|

SU985338A1 |

| Устройство для введения поправок в шкалу времени | 1979 |

|

SU855601A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Устройство для программной закалки длинномерных изделий | 1982 |

|

SU1016385A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АБСОЛЮТНОЙ ВЛАЖНОСТИ | 1991 |

|

RU2019821C1 |

| Устройство для программного управления | 1985 |

|

SU1280571A1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

Г.,

Z3

/ff

-t

Даты

1968-01-01—Публикация