(21)4616751/24

(22)05.12.88

(46) 30.10.91. Бюл. № 40

(71)Институт кибернетики им.В.М.Глушкова

(72)И.В.Самус

(53) 681.325 (088.8) (56) Стахов А.И.Семнадцатиразрядный самокорректирующийся АЦП. Приборы и системы управления, 1986, К 1, с. 18.

Авторское свидетельство СССР 1356223, кл. Н 03 М 1/10, 1985. (прототип.

(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ ПОГРЕШНОСТИ

(57) Изобретение относится к вычислительной технике. Изобретение позволяет повысить точность. Это достигается введением в аналого-цифровой преобразователь преобразователя

13 код-напряжение, блоки 4 суммирования, тактового генератора 6. блока 7 ключей, счетчика 9, вычитающего устройства 10, запоминающего устройства 11, блока 12 поиска поправок, источника 13 эталонных напряжении, ана

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Цифровое силоизмерительное устройство | 1987 |

|

SU1509604A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2205500C1 |

| Адаптивный формирователь импульсов | 1990 |

|

SU1750034A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187884C1 |

(Л

о оо оо

4

со

.1

лотового ключа 14, цифрового переключателя 15 и регистра 16. Это позволяет сократить число поверенных точек диапазона преобразования и уменьшить

Изобретение относится к вычислительной технике и может быть использовано в качестве самостоятельного модуля для осуществления аналого-цифрового преобразования с высокой точностью

Цель изобретения - повышение точности.

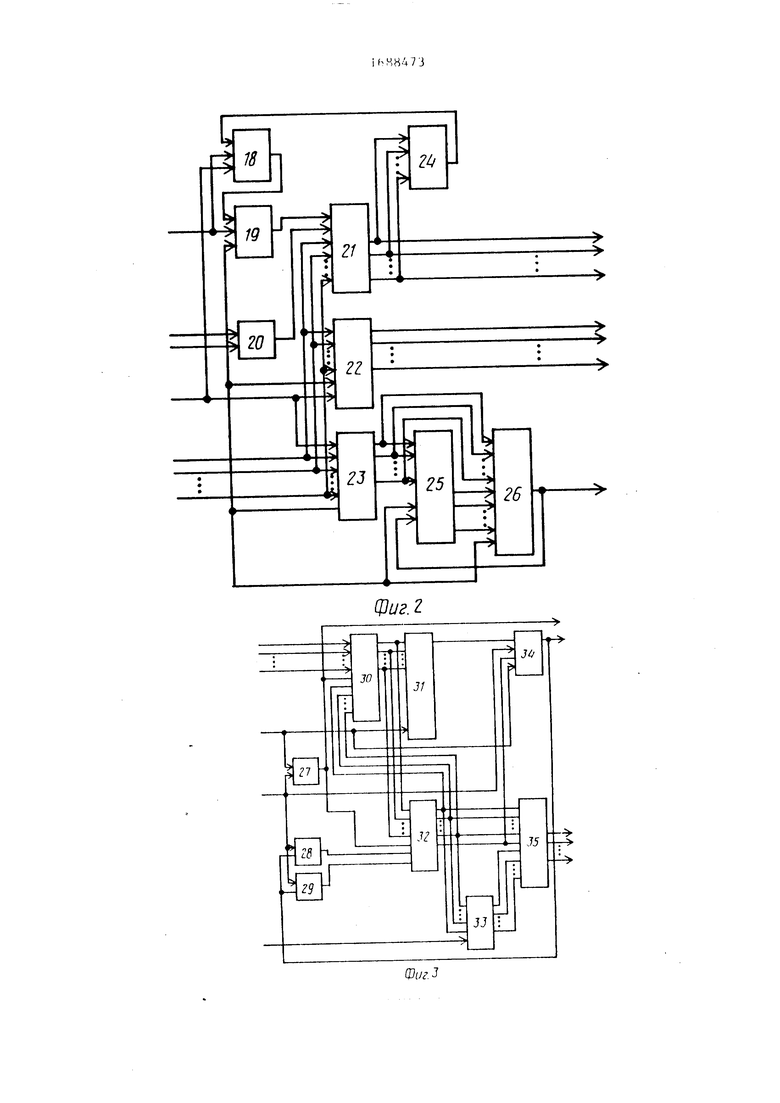

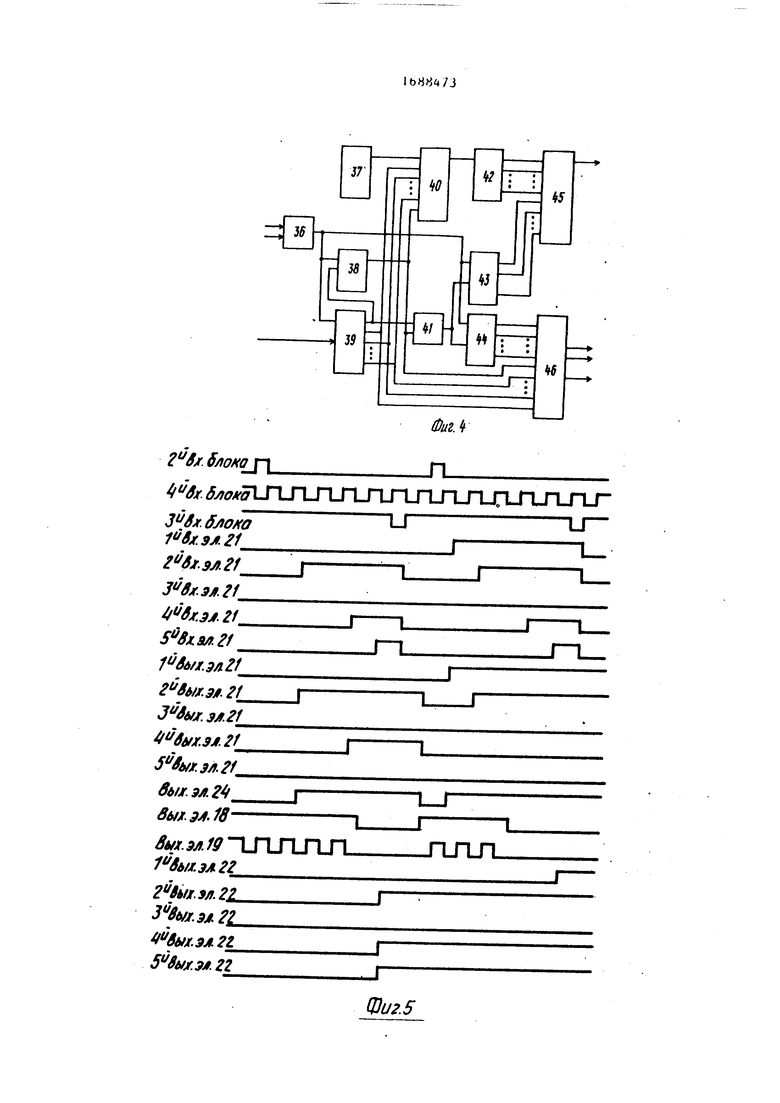

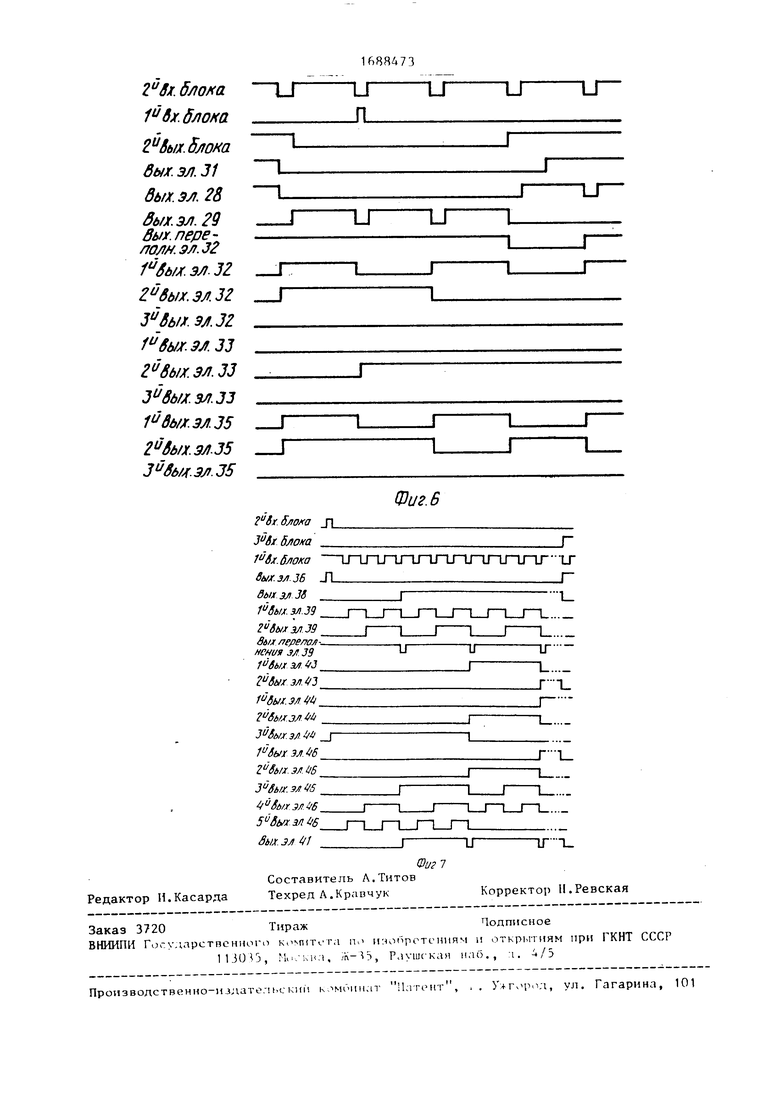

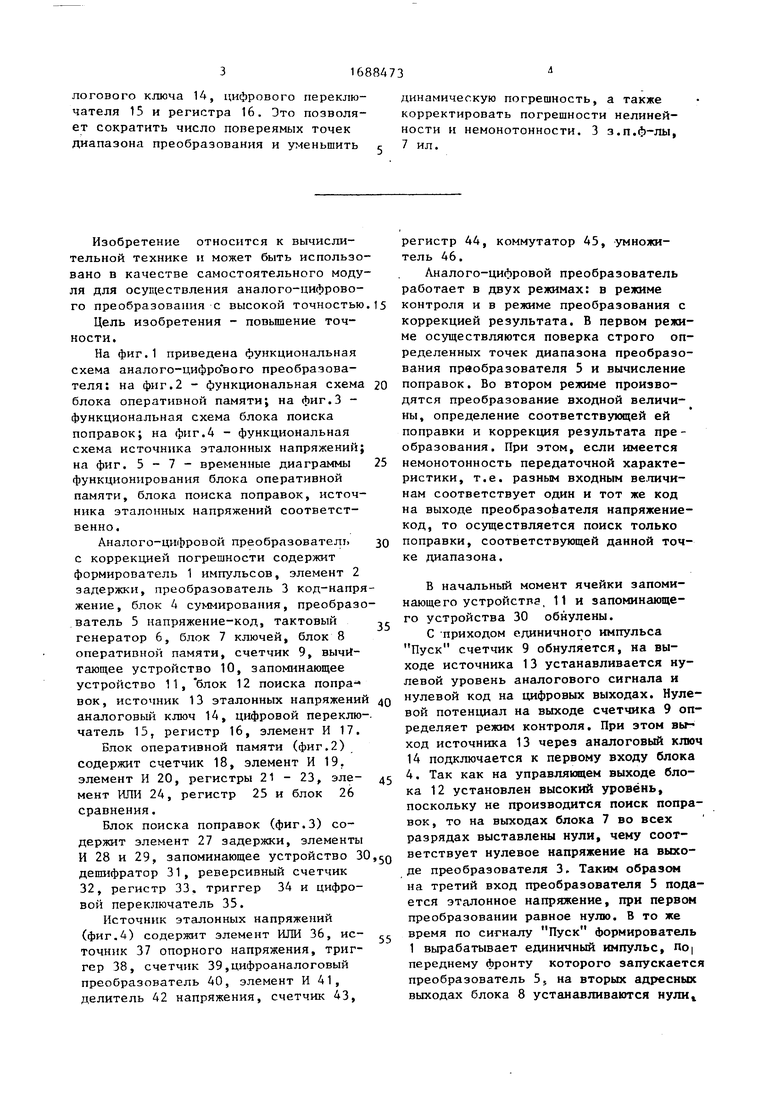

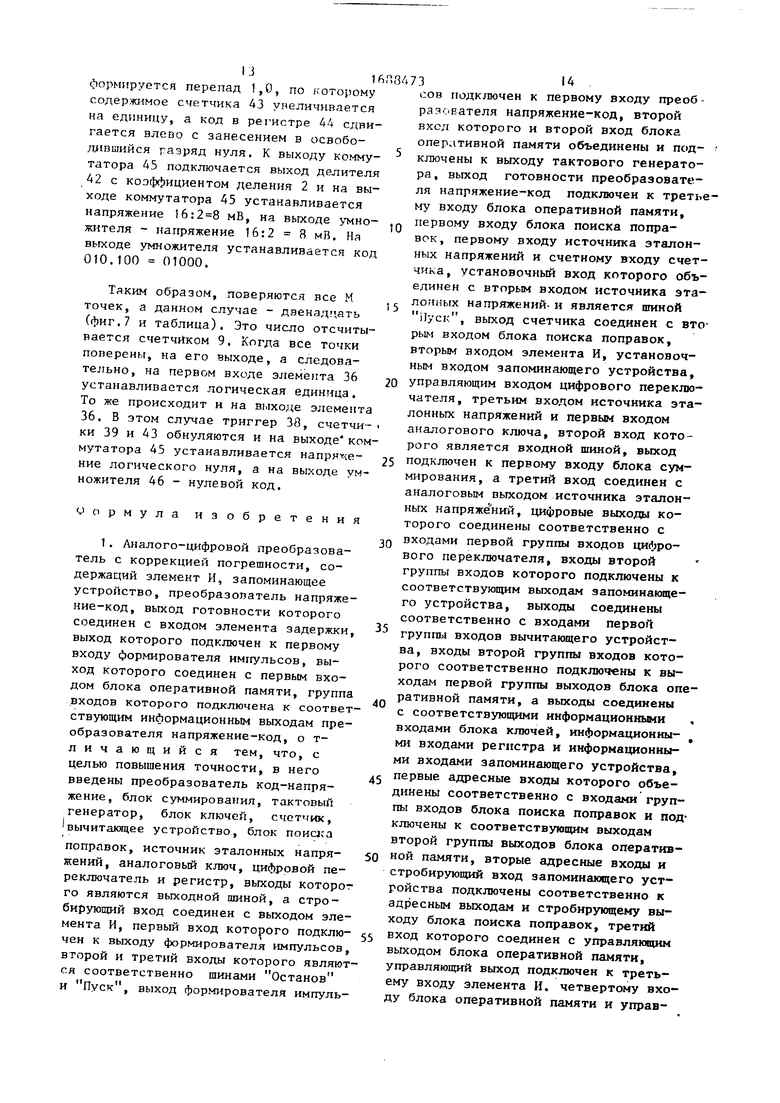

На фиг.1 приведена функциональная схема аналого-цифро вого преобразователя: на фиг.2 - функциональная схема блока оперативной памяти; на фиг.З - функциональная схема блока поиска поправок; на фиг.4 - функциональная схема источника эталонных напряжений; на фиг. 5 - 7 - временные диаграммы функционирования блока оперативной памяти, блока поиска поправок, источника эталонных напряжений соответственно.

Аналого-цифровой преобразователь с коррекцией погрешности содержит формирователь 1 импульсов, элемент 2 задержки, преобразователь 3 код-напряжение, блок 4 суммирования, преобразователь 5 напряжение-код, тактовый генератор 6, блок 7 ключей, блок 8 оперативной памяти, счетчик 9, вычитающее устройство 10, запоминающее устройство 11, блок 12 поиска попра- вок, источник 13 эталонных напряжений аналоговый ключ 14, цифровой переключатель 15, регистр 16, элемент И 17.

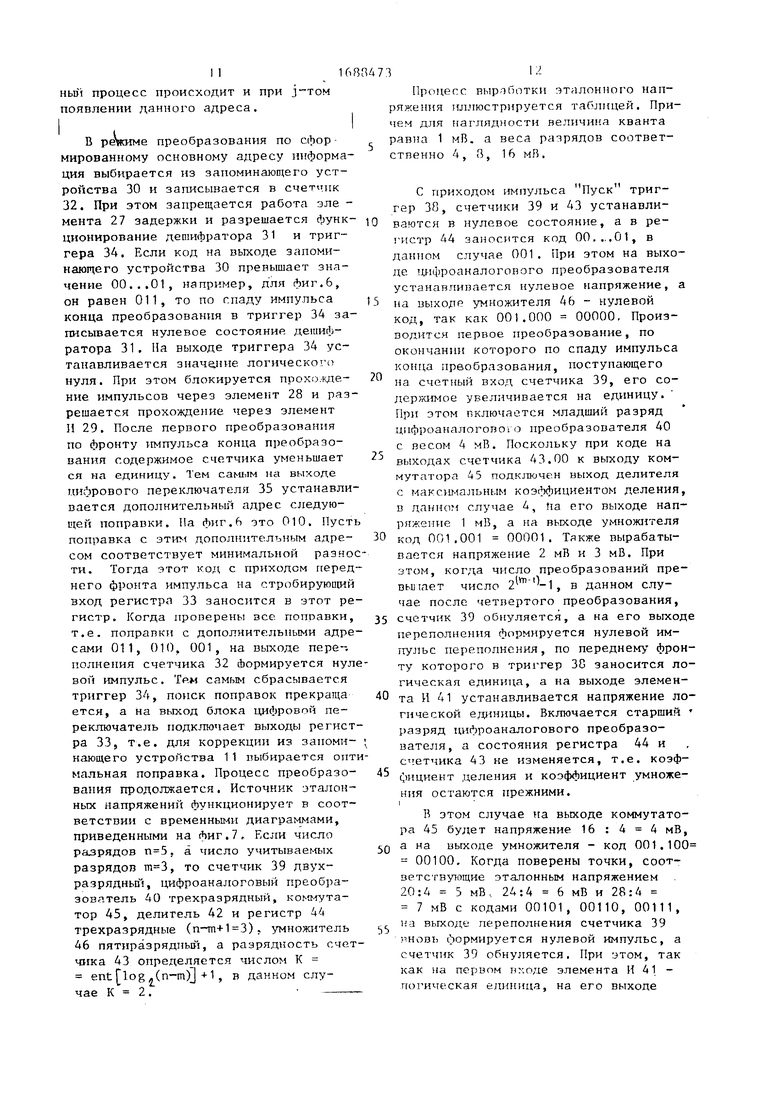

Блок оперативной памяти (фиг.2) содержит счетчик 18, элемент И 19. элемент И 20, регистры 21 - 23, эле- мент ИЛИ 24, регистр 25 и блок 26 сравнения.

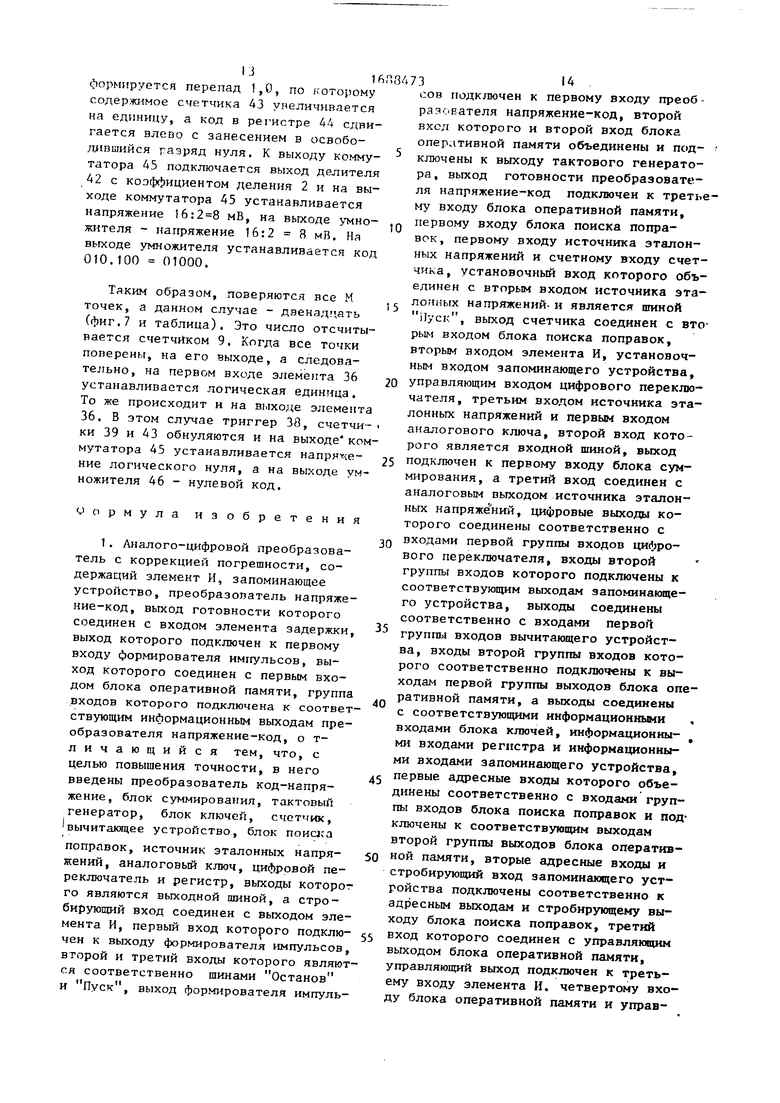

Блок поиска поправок (фиг.З) содержит элемент 27 задержки, элементы И 28 и 29, запоминающее устройство 30 дешифратор 31, реверсивный счетчик 32, регистр 33. триггер 34 и цифровой переключатель 35.

Источник эталонных напряжений (фиг.4) содержит элемент ИЛИ 36, источник 37 опорного напряжения, триггер 38, счетчик 39,цифроаналоговый преобразователь 40, элемент И 41, делитель 42 напряжения, счетчик 43,

динамическую погрешность, а также корректировать погрешности нелинейности и немонотонности. 3 з.п.ф-лы, 7 ил.

0

5

0

0

5

5

5

регистр 44, коммутатор 45, умножитель 46.

Аналого-цифровой преобразователь работает в двух режимах: в режиме контроля и в режиме преобразования с коррекцией результата. В первом режиме осуществляются поверка строго определенных точек диапазона преобразования преобразователя 5 и вычисление поправок. Во втором режиме производятся преобразование входной величины, определение соответствующей ей поправки и коррекция результата пре - образования. При этом, если имеется немонотонность передаточной характеристики, т.е. разным входным величинам соответствует один и тот же код на выходе преобразователя напряжение- код, то осуществляется поиск только поправки, соответствующей данной точке диапазона.

В начальный момент ячейки запоминающего устройства, 11 и запоминающего устройства 30 обнулены.

С приходом единичного импульса Пуск счетчик 9 обнуляется, на выходе источника 13 устанавливается нулевой уровень аналогового сигнала и нулевой код на цифровых выходах. Нулевой потенциал на выходе счетчика 9 определяет режим контроля. При этом выход источника 13 через аналоговый ключ 14 подключается к первому входу блока 4. Так как на управляющем выходе блока 12 установлен высокий уровень, поскольку не производится поиск поправок, то на выходах блока 7 во всех разрядах выставлены нули, чему соответствует нулевое напряжение на выходе преобразователя 3. Таким образом на третий вход преобразователя 5 подается эталонное напряжение, при первом преобразовании равное нулю. В то же время по сигналу Пуск формирователь 1 вырабатывает единичный импульс, ПО| переднему фронту которого запускается преобразователь 5S на вторых адресных выходах блока 8 устанавливаются нулиг

По тактовым импульсам, поступающим с выхода тактового генераторл 6 на второй вход преобразователя 5, производится поразрядное уравновешивание входной величины, и на информационных выходах преобразователя 5 формируется цифровой код, соответствующий входному напряжению с учетом погрешности. Одновременно в блоке 8 определяется адрес поправки. По окончании преобразования на выходе готовности преобразователя 5 формируется нулевой импульс, по переднему фронту которого результат заносится в блок 8 и выставляется на его первых выходах. На адресных выходах блока 12 формируется дополнительный адрес поправки, равный числу появлений данного результата преобразования в режиме конт- 20 рсходит в режим преобразования входроля, в данном случае 00...01.

Таким образом, на первых и вторых адресных входах запоминающего устройства 11 выставлен соответственно основной и дополнительный адреса поправки, а на его информационных входах - код поправки, равный

N,

л;

где Ид; 1J

N . - N ИИ oi )

Hi

N

Oi

код поправки i-тои точки диапазона;

код результата преобразования эталонного напряжения; код эталонного напряжения, соответствующего i-той точке,

поскольку на второй группе входов вычитающего устройства 10 установлен результат преобразования, а на первой группе входов - код, соответствующий эталонному напряжению, который поступает с выходов источника 13 через цифровой переключатель 15.

Через время, определяемое элементом 27 задержки блока 12, в течение нулевого импульса на выходе готовности преобразователя 5 это значение поправки записывается в запоминающее устройство 11. По окончании нулевого импульса в источнике эталонных напряжений устанавливаются следующее значение эталонного напряжения и соответствующий ему код. Содержимое счетчика 9 увеличивается на единицу и через время, определяемое элементом 2 задержки, вновь запускается формирователь 1. Производится поверка в следующей точке. При этом результат

0

5

вычислений в режиме контроля не -записывается в регистр 16, гак как на втором входе элемента 17 присутствует ну- потенциал. Таким образом поверяются все заданные точки.

В том случае, если в процессе поверки из-за немонотонности передаточной характеристики преобразователя 5 получен результат преобразования эталонного напряжения,зафиксированный ранее, т.е. по этому адресу уже поправка определена, дополнительный адрес н на выходе блока 12 увеличивается на единицу и значение поправки записывается в свободную ячейку. Когда поверены все М точек, на выходе счетчика 9 устанавливается уровень логической единицы. Тем самым устройство пеной величины.

В этом случае на аналоговом выходе источника 13 устанавливается нулевой уровень, а на его цифровых выходах нулевой код. Цифровой переключатель 15 подключается к первым входам вычитающего устройства 10 выходы запоминающего устройства 11. При этом оно переводится в режим считывания. Аналотовый ключ 14 подключает к первому входу схемы суммирования входное напряжение, и с приходом очередного запускающего импульса с выхода формирователя 1 производится преобразование входного напряжения.

По окончании преобразования по переднему фронту импульса, поступающего с выхода готовности преобразователя напряжение-код 5.результат преобразования записывается в блок 8 и выставляется на выходах первой группы блока 8, на выходах второй группы которого уже выставлен основной адрес поправки, соответствующий результату

преобразования. По этому адресу.на

выходы запоминающего устройства 11 подается код поправки, который, поступая на входы первой группы входов вычитающего устройства ТО, через цифровой

переключатель 15 вычитается из кода результата. При этом

N

К.

N... - N. ,

fli Д

где II,

- скорректированный результат

преобразования.

Этот код по переднему фронту следующего запускающего импульса, формирующегося на выходе формирователя 1,

заносится п регистр 16. Таким обратом производится М преобразований. После этого на выходе счетчика 9 вновь уста- навливается нулевой потенциал, и уст- ройство переводится в режим контроля, который, в свою очередь, сменяется режимом преобразования, и так вплоть до появления на первом входе формирователя 1 сигнала Останов, запрещаю- щего формирование запускающих импульсов.

Если в процессе преобраэопания будет получен результат, которому соответствует несколько значений попра- вок, о чем свидетельствует дополнительный код адреса на выходах блока 12, превышающий 00...01, то производится поиск соответствующей поправки. В этом случае на управляющем выходе блока 12 устанавливается нулевой уровень, чем блокируется запись результата преобразования в регистр 16, разрешается поступление кодовых комбинаций через блок 7 на входы преобразователя 3, который вь раЬатыва ет напряжение отрицательной полярнос

ти,

и запрещается изменение кода на

первых и вторых пмупдах блока R.

Поиск поправки осуществляется следующим образом.

Код поправки, выбранный по основному адресу, который не изменяется, и дополнительному адресу, который уменьшается в процессе поиска с каждым преобразованием на единицу, поб- тупает для коррекции в вычитающее устройство 10. Скорректированный результат поступает на входы преобразователя 3 код-напряжение. Преобразованный аналоговый сигнал отрицательной полярности, соответствующий скорректированному коду, поступает на второй вход блока 4, который производит суммирование его с входным напряжением. Полученная в результате такого суммирования аналоговая разность с приходом очередного запускающего импульса преобразуется преобразователем 5 и запоминается в блоке 8. При этом по переднем фронту импульса конца преобразования формирующегося на выходе готовности преобразователя 5,, дополнительный адрес уменьшается на единицу и осуществляется следующее преобразование разности входного напряжения преобразователя 3, соответствующего г оррек

5

0

5

0

5

0

5

0

тигюн ишому результату с учетом нового значения поправки. Коды разностей сравниваются в блоке 8 и дополнительный адрес поправки, соответствующий наименьшей разности, запоминается в блоке 12. Эти операции осуществляются для всех поправок, принадлежащих данному основному адресу.

Поиск поправки прекращается, а в качестве истинной принимается поправка, соответствующая минимальной разности. На управляющем выходе блока 12 устанавливается уровень логической единицы, и результат, скорректированный на значение найденной поправки, по переднему фронту очередного запускающего импульса записывается в регистр 1Г){ Так как число преобразований, подсчитываемое счетчиком 9, равное II фиксировано и в процессе поиска поправки счетчик ) не блокируется, чем больше точек немонотонности передаточной характеристики, тем чаще осуществляется переход в резшм контроля.

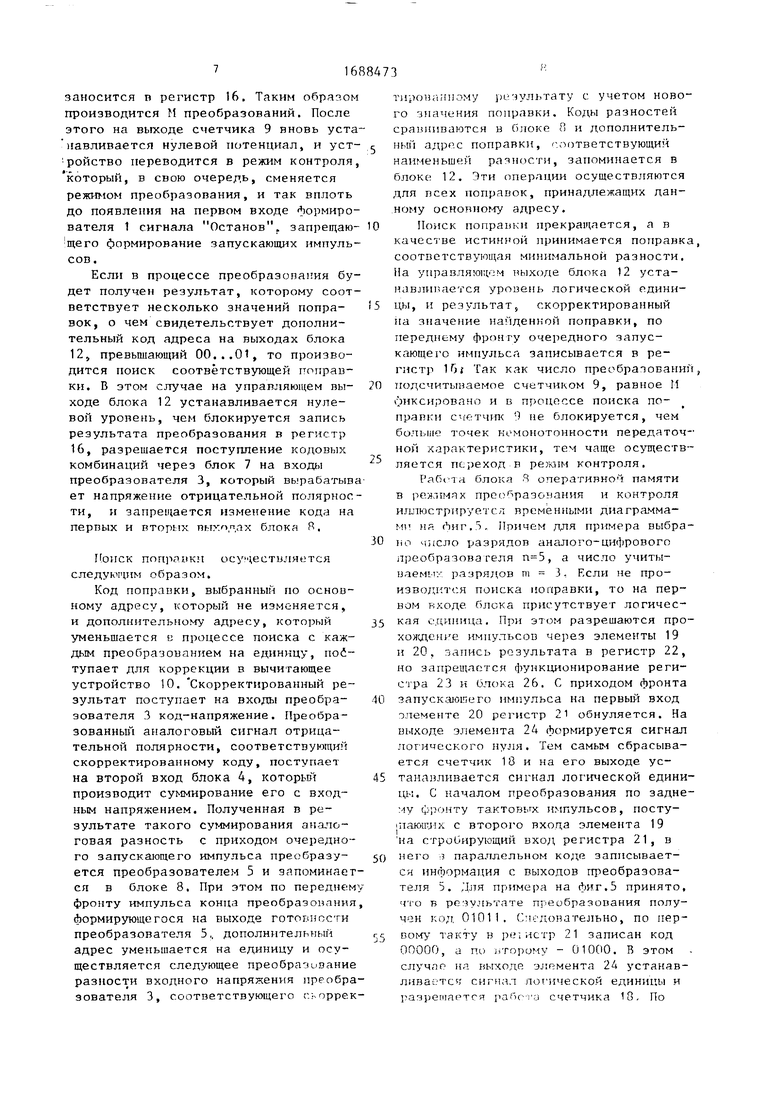

PaOiia блока Я оперативно памяти в режимах преобразования и контроля иллюстрирует ел временными диаграммами HP Лиг,), Причем для примера выбра- ьо число разрядов аналого-цифрового преобразователя , а число учитываем г.- разрядов m 3. Если не производится поиска поправки, то на первом ьходе блока присутствует логическая единица. При этом разрешаются прохождение импульсов через элементы 19 и 20. -запись результата в регистр 22, но запрещается функционирование регистра 23 и олока 26. С приходом фронта запускающего импульса на первый вход элементе 20 регистр 21 обнуляется. На выходе элемента 24 формируется сигнал логического нуля. Тем самым сбрасывается счетчик 18 и на его выходе устанавливается сигнал логической единицы. С началом преобразования по заднему фронту тактовых импульсов, поступающих с второго входа элемента 19 на строОирующий вход регистра 21, в него з параллельном коде записывается информация с выходов преобразователя 5. Для примера на фиг.5 принято, чiо в результате преобразования получен код 01011, Отеяовательно, по первому такту в pei .IOTP 21 записан код 00000, а по ь-ropoMV - 01000. В этом - случаи нл выходе элемента 24 устанав- лива.тсч сигнал логической единицы и разрешается рабе i счетчика 18, По

переднему дронту третьего Ti Tiu oro импульса в счетчик 18 записывается единица, а по спаду в регистр 21 - код ОЮОО. По переднему фронту чет- вертого импульса содержимся счетчика 10 составляет число два, а по спаду в регистр 21 записывается код 01010. По переднему фронту содержимое счетчика составляет чисто три, н его выходе устанавливается нупевой уровень, что блокирует прохождение тактовых импульсов через элемечт 19. Поэтому содержимое регистра 21 не изменяется, хотя после пятого импульса на его входах код 01011, т.е. основной адрес поправки определяет я только n-старшимн разрядами кода, в данном случае тремя, начиная с первого включенного. По окончании пресбразо- вания по переднему фронту импульса, поступающего на стробирующнй вход ре гистра 22, о него заносится код ре- зультата преобразования. На фиг.5 приведен процесс формирования основ- ного адреса поправки для кода результата преобразования 11011. В этом случае основной адрес составляет 11000.

Если производится поиск поправки, то на первом входе блока устанавливается нулевой уровень. При этом запрещаются прохождение импульсов через элементы 19 и 20, а следовательно, изменение содержимого регистров 21 и 22, в которых хранится основной адрес и результат преобразования точки диапазона, находящейся на участке немонотонности. В то же время разрешается работа регистра 23 и блока 26, а в регистр 25 в параллельном коде заносится код 11 ... 1 1. После первого преобразования разности входной и скорректированной величины результат по фронту окончания импуль- са преобразования, поступающего на стробирующий вход регистра 23, заносится к этот регистр и сравнивается блоком 26 с содержимым регистра 25. Если код регистра 23 меньше содержи- мого регистра 25, а при первом преобразовании это выполняется всегда, то на выходе блока 26 формируется передний фронт единичного импульса, по которому содержимое регистра 23 переписывается в регистр 25,, а в блоке 12 в регистр 33 переписывается соответствующий этой разности дополнительный адрес поправки. Посколь

JQ ii 20 25

30 э5 40 45 50

5

ку пос.гч, занесения содержимое рс- гнсгрсв 23 и 5 ня выход.4 блока 2Ь устанавливав.ся нулевой уровень, Таким образом, по окончании поиска в регистре 2rj оказывается код наименьшей разности, р в регистре 33 блока 12 - соответствующий ей дополните пьныч адрес поправки.

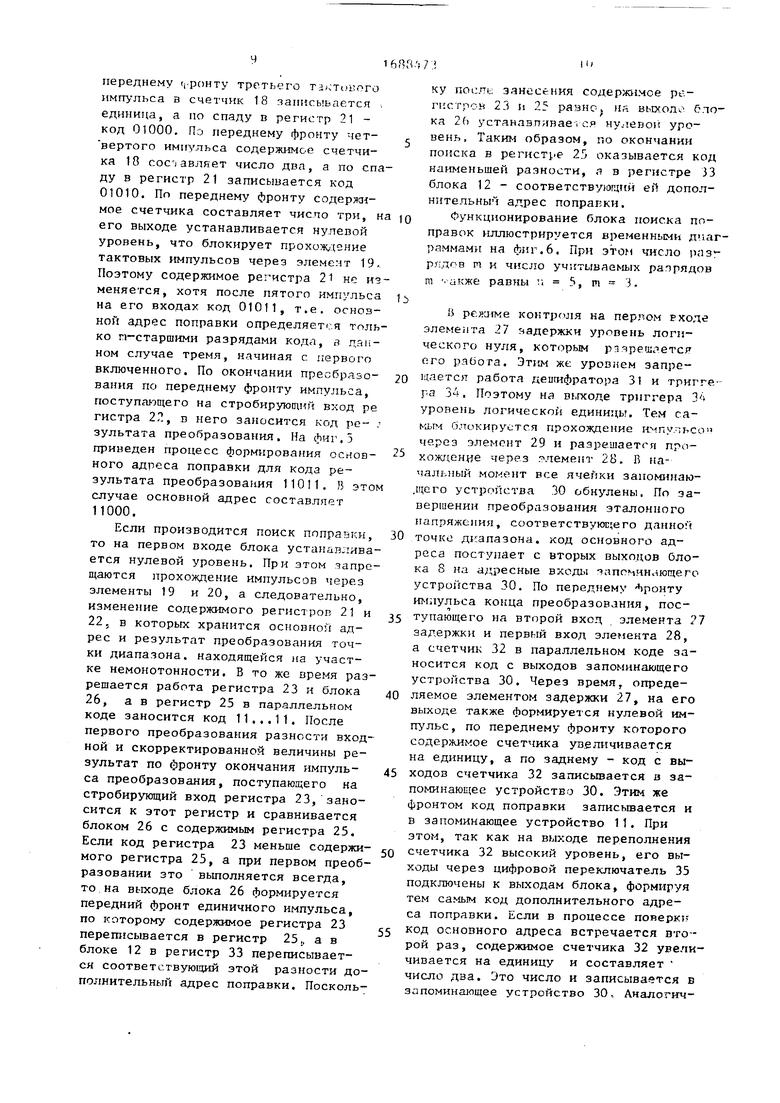

Функционирование блока поиска поправок иллюстрируется временными диаграммами на фиг.6. При этом число рпз- PJ цов п и число учитываемых разрядов m акже равны 5, т i.

ii режиме контроля на пергом Рходе элемента 27 задержки уровень логического нуля, которым рпреш ется его работа. Этим же уровнем запрещается работа дешифратора 31 и тригге pa . Ппэтому на выходе триггера 3 уровень логической единицы. Тем са- кым блокируется прохождение nvny ibCO через элемент 29 и разрешается прохождение через ленент 28, В начальный момент все ячейки запоминаю- .щсго устройства 30 обнулены. По завершении преобразования эталонного напряжения, соответствующего данном точке диапазона, ход основного адреса поступает с вторых выходов блока 8 на адресные входы ялпомчн.чющего устройства 30. По переднему Фронту импульса конца преобразования, поступающего на второй вход элемента 7 задержки и первый вход элемента 28, а счетчик 32 в параллельном коде заносится код с выходов запоминающего устройства 30. Через время, определяемое элементом задержки 27, на его выходе также формирует ся нулевой импульс, по переднему фронту которого содержимое счетчика увеличивается на единицу, а по заднему - код с выходов счетчика 32 записывается и за- поминакш(ее устройство 30. Этим же Фронтом код поправки записывается и в запоминающее устройство 11. При этом, так как на выходе переполнения счетчика 32 высокий уровень, его выходы через цифровой переключатель 35 подключены к выходам блока, формируя тем самым код дополнительного адреса поправки. Ьсли в процессе поверю- код основного адреса встречается второй раз, содержимое счетчика 32 увеличивается на единицу и составляет число два. Это число и записывается в запоминающее устройство 30- АналогичII1688473

ный процесс происходит и при j-том появлении данного адреса.

р ч р с

В преобразования по сфор мированному основному адресу информация выбирается из запоминающего устройства 30 и записывается в счет«ик 32. При этом запрещается работа зле - мента 27 задержки и разрешается функционирование дешифратора 31 и триггера 34. Если код на выходе запоминающего устройства 30 превышает значение 00...01, например, для фиг.6, он равен 011, то по гпаду импупьса конца преобразования в триггер 34 записывается нулевое состояние дешифратора 31. На выходе триггера 34 устанавливается значение логического нуля. При этом блокируется прохокде- ние импульсов через элемент 28 и разрешается прохождение через элемент И 29. После первого преобразования по фронту импульса конца преобразования содержимое счетчика уменьшает ся на единицу. Тем самым на выходе цифрового переключателя 35 устанавливается дополнительный адрес следующей поправки. На фиг.6 это 010. Пусть поправка с этим дополнительным адресом соответствует минимальной разности. Тогда этот код с приходом переднего фронта импульса на стробирующий вход регистра 33 заносится в этот регистр. Когда проверены асе поправки, т.е. поправки с дополнительными адресами 011, 010. 001, на выходе переполнения счетчика 32 Формируется нулевой импульс. Тем самым сбрасывается триггер 34, поиск поправок прекраща ется, а на выход блока цифровой переключатель подключает выходы регистра 33, т.е. для коррекции из запоми- нающего устройства 11 выбирается оптимальная поправка. Процесс преобразования продолжается. Источник эталонных напряжений функционирует в соответствии с временными диаграммами, приведенными на Лиг.7. Если число разрядов , а число учитываемых разрядов , то счетчик 39 двух- разрядный, цифроаналоговый преобразователь 40 трехразрядныи, коммутатор 45, делитель 42 и регистр 44 трехразрядные (n-m+1 3). умножитель 46 пятиразрядный, а разрядность счетчика 43 определяется числом К ent Јlog .(n-m)J +1 , в данном случае К 2. -

5

0

5

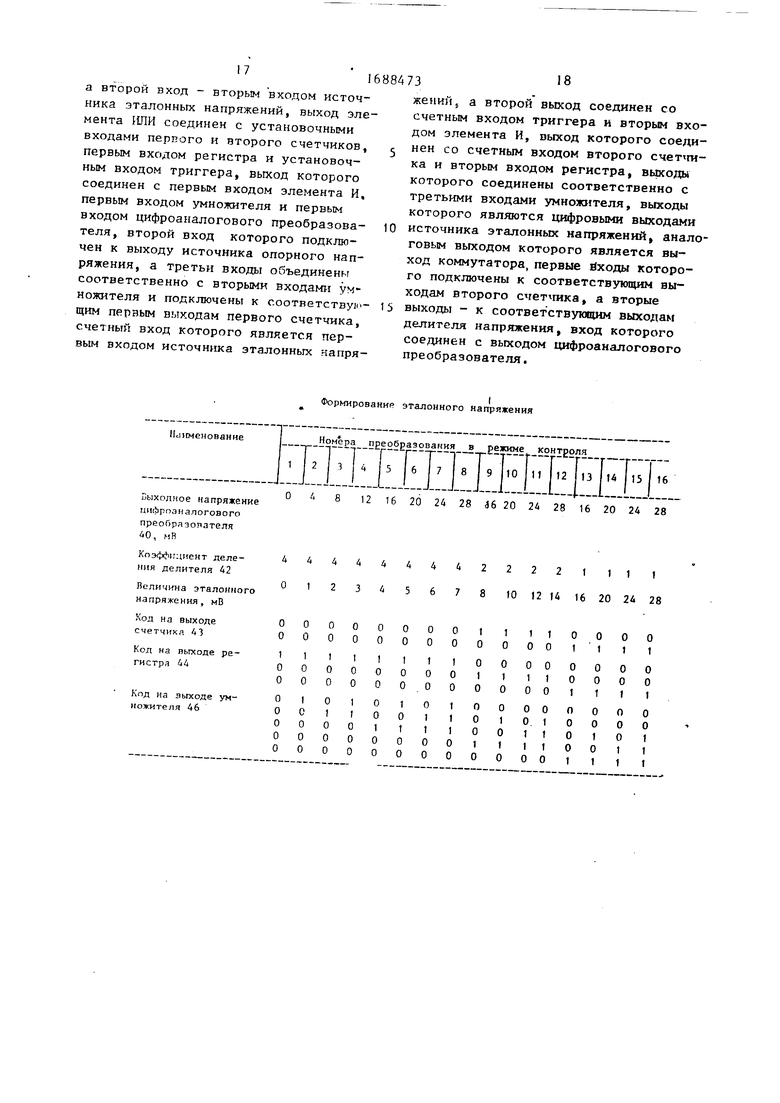

Процесс выработки эталонного напряжения иллюстрируется таблицей. Причем для наглядности величина кванта равна 1 мВ. а веса разрядов соответственно 4, Я, 16 мВ.

С приходом импульса Пуск триггер 38, счетчики 39 и 43 устанавливаются в нулевое состояние, а в регистр 44 заносится код 00...01, в данном случае 001. При этом на выходе Щ1фроаналогового преобразователя устанавливается нулевое напряжение, а на выходе умножителя 46 - нулевой код, так как 001.000 00000, Производится первое преобразование, по окончании которого по спаду импульса конца преобразования, поступающего на счетный вход счетчика 39, его содержимое увеличивается на единицу. При этом пключается младший разряд цпфроаналогово о преобразователя 40 с весом 4 мВ. Поскольку при коде на выходах счетчика 43.00 к выходу коммутатора 45 подключен выход делителя с максимальным коэффициентом деления, в данном случае 4s на его выходе напряжение 1 мВ, а на выходе умножителя код 001.001 00001. Также вырабатывается напряжение 2 мВ и 3 мВ. При этом, когда число преобразований пре- вылает число , в данном случае после четвертого преобразования, 5 счетчик 39 обнуляется, а на его выходе переполнения формируется нулевой импульс переполнения, по переднему фронту которого в триггер 38 заносится логическая единица, а на выходе элемента И 4 1 устанавливается напряжение логической единицы. Включается старший разряд цифроаналогового преобразователя, а состояния регистра 44 и счетчика 43 не изменяется, т.е. коэффициент деления и коэффициент умножения остаются прежними.

I

В этом случае на выходе коммутатора 45 будет напряжение 16 : 4 4 мВ, а на выходе умножителя - код 001.100 00100, Когда поверены точки, соответствующие эталонным напряжением 20:4 5 мВ 24:4 6 мВ и 28:4 7 мВ с кодами 00101, 00110, 00111, на выходе переполнения счетчика 39 новь формируется нулевой импульс, а счетчик 39 обнуляется. При этом, так как на первом в у. оде элемента И 41 - логическая единица, на его выходе

0

0

45

50

5

I 3

формируется перепад 1,0, по которому содержимое счетчика 43 увеличивается на единицу, а код в регистре 44 сдвигается влево с занесением в освободившийся газряд нуля. К выходу коммутатора 45 подключается выход делителя 42 с коэффициентом деления 2 и на выходе коммутатора 45 устанавливается напряжение мВ, на выходе умножителя - напряжение 16:2 8 мВ. На выходе умножителя устанавливается код 010.100 01000.

Таким образом, поверяются все М точек, а данном случае - двенадцать (фиг.7 и таблица). Это число отсчитывается счетчиком 9. Когда все точки поверены, на его выходе, а следовательно, на первом входе элемента 36 устанавливается логическая единица. То же происходит и на выходе элемента 36. В этом случае триггер 38, счетчики 39 и 43 обнуляются и на выходе коммутатора 45 устанавливается напряжение логического нуля, а на выходе умножителя 46 - нулевой код.

V о р м у л а изобретения

поправок, источник эталонных напряжений, аналоговый ключ, цифровой переключатель и регистр, выходы которог го являются выходной шиной, а стро- бирующий вход соединен с выходом эле16

мента И, первый вход которого подклю- 55вход которого соединен с управляющим

чен к выходу формирователя импульсов,выходом блока оперативной памяти,

второй и третий входы которого являют-управляющий выход подключен к треться соответственно шинами Останов ему входу элемента И. четвертому вхои Пуск, выход формирователя импуль-ду блока оперативной памяти и управ

10

3473|4

сов подключен к первому входу преобраа рателя напряжение-код, второй вход которого и второй вход блока оперативной памяти объединены и под- ключены к выходу тактового генератора, выход готовности преобразователя напряжение-код подключен к третьему входу блока оперативной памяти, первому входу блока поиска поправок, первому входу источника эталонных напряжений и счетному входу счетчика, установочный вход которого объединен с вторым входом источника эталонных напряжений- и является шиной Пуск, выход счетчика соединен с вто рым входом блока поиска поправок, вторым входом элемента И, установочным входом запоминающего устройства, 20 управляющим входом цифрового переключателя, третьим входом источника эталонных напряжений и первым входом аналогового ключа, второй вход которого является входной шиной, выход подключен к первому входу блока сум15

25

0

5

0

5

0

мирования, а третий вход соединен с аналоговым выходом источника эталонных напряжений, цифровые выходы которого соединены соответственно с входами первой группы входов цифрового переключателя, входы второй группы входов которого подключены к соответствующим выходам запоминающего устройства, выходы соединены соответственно с входами первой группы входов вычитающего устройства, входы второй группы входов которого соответственно подключены к выходам первой группы выходов блока оперативной памяти, а выходы соединены с соответствующими информационными , входами блока ключей, информационны- , ми входами регистра и информационными входами запоминающего устройства, первые адресные входы которого объединены соответственно с входами группы входов блока поиска поправок и подключены к соответствующим выходам второй группы выходов блока оперативной памяти, вторые адресные входы и стробирующий вход запоминающего устройства подключены соответственно к адресным выходам и стробирующему выходу блока поиска поправок, третий

1Ь16

ляющему входу блока ключей, выходы которого соединены с соответствующими входами преобразователя код-напряжение, выход которого подключен к второму входу блока суммирования, выход которого подключен к третьему входу преобразователя напряжение-код.

Q 0 ,

5

316

элементах И, запоминающем устройстве, яешиЛраторе, реверсивном счетчике, регистре, триггере, цифровом переключателе и элементе задержки, первый вход которого объединен с установочным входом дешифратора и первым установочным входом триггера и является вторым входом блока, второй вход элемента задержки объединен со счетным входом триггера, первым входом первого элемента И, прямым входом второго элемента И и является первым входом блока, выход элемента задержки соединен со стробирующим входом запоминающего устройства, первым счетным входом реверсивного счетчика и является стробирующим выходом блока, группой входов которого являются адресные входы запоминающего устройства, информационные входы которого соответственно объединены с информационными входами регистра, первыми информационными входами цифрового переключателя и соединены с соответствующими первыми выходами реверсивного счетчика, выходы запоминающего устройства соединены с соответствующими информационными входами реверсивного счетчика и информационными входами дешифратора, выход которого подключен к информационному входу триггера, выход которого является управляющим выходом блока и соединен с вторым входом первого элемента И и инверсным входом второго элемента И, выход которого соединен с вторым счетным входом реверсивного счетчика, стробирующий вход которого подключен к выходу первого элемента И, а второй выход - к второму установочному входу триггера и установочному входу цифрового переключателя, выходы которого являются адресными выходами блока, а вторые информационные входы соединены с соответствующими выходами регистра, стробнрующий вход которого является третьим входом блока.

7 1

а второй вход - вторым входом источника эталонных напряжений, выход эле мента ИЛИ соединен с установочными входами первого и второго счетчиков, первым входом регистра и установочным входом триггера, выход которого соединен с первым входом элемента И, первым входом умножителя и первым входом цифроаналогового преобразователя, второй вход которого подключен к выходу источника опорного напряжения, а третьи входы объединены соответственно с вторыми входами умножителя и подключены к соответствую щим первым выходам первого счетчика, счетный вход которого является первым входом источника эталонных напря

Формирование эталонного напряжения

8847318

жений5 а второй выход соединен со счетным входом триггера и вторым входом элемента И, выход которого соеди- г нен со счетным входом второго счетчика и вторым входом регистра, выходы которого соединены соответственно с третьими входами умножителя, выходы которого являются цифровыми выходами 10 источника эталонных напряжений, аналоговым выходом которого является выход коммутатора, первые входы которого подключены к соответствующим выходам второго счетчика, а вторые

15 выходы - к соответствующим выходам делителя напряжения, вход которого соединен с выходом цифроаналогового преобразователя.

UlTLJ

L

-Г

TJTLJtTLlTrUlJTJlJTJTJTJaj ffnt

д„г

f гпф

+

r

Л

л

r/«7f RQ

гг

тг w Wntr

H ™-ЩпЈ 72 nmtnl

гг wfyt nJTJ-LTLru 6i пх нд

1ft -ire f/9ff

1fyz re jr/90

tf

tirc 9nt

J

TL

Jtrt M

IZretJnl oxotrgxf nЈ

6Ј

,tf

Авторы

Даты

1991-10-30—Публикация

1988-12-05—Подача