Известны анализаторы устойчивости фазирующих устройств с дискретным управлением, содержащие распределитель на ячейках памяти с переключателем .выхода, схемы совпадения, линии задержки, генератор, динамический и статический триггеры и ячейки памяти.

Предложенное устройство отличается от известных тем, что в нем выход одной из ячеек распределителя подключен к запускающему входу динамического триггера, ;выход которого присоединен ко входу исследуемого фазирующего устройства, а остальные выходы распределителя через нереключатель соединены со входом линии задержки на двух ячейках памяти, к выходам которых подключены входы .статического триггера; выходы статического триггера соединены с управляющими входами схем совладения, вторые входы которых подключены соответственно к источникам импульсов ощибок и импульсов фронтов принимаемых посылок исследуемого фазирующего устройства, а -выходы соединены со счетчиком числа ощибок н со входом считывания ячейки памяти, вход записи которой .подключен к контакту кнопочного распределителя, а выход - ко входу запуска второго динамического триггера, соединенного выходом со счетчиком измерения фазового рассогласования.

рассогласования и вероятности ощибки при приеме кодового импульса в период вхождения исследуемого фазирующего устройства в фазу.

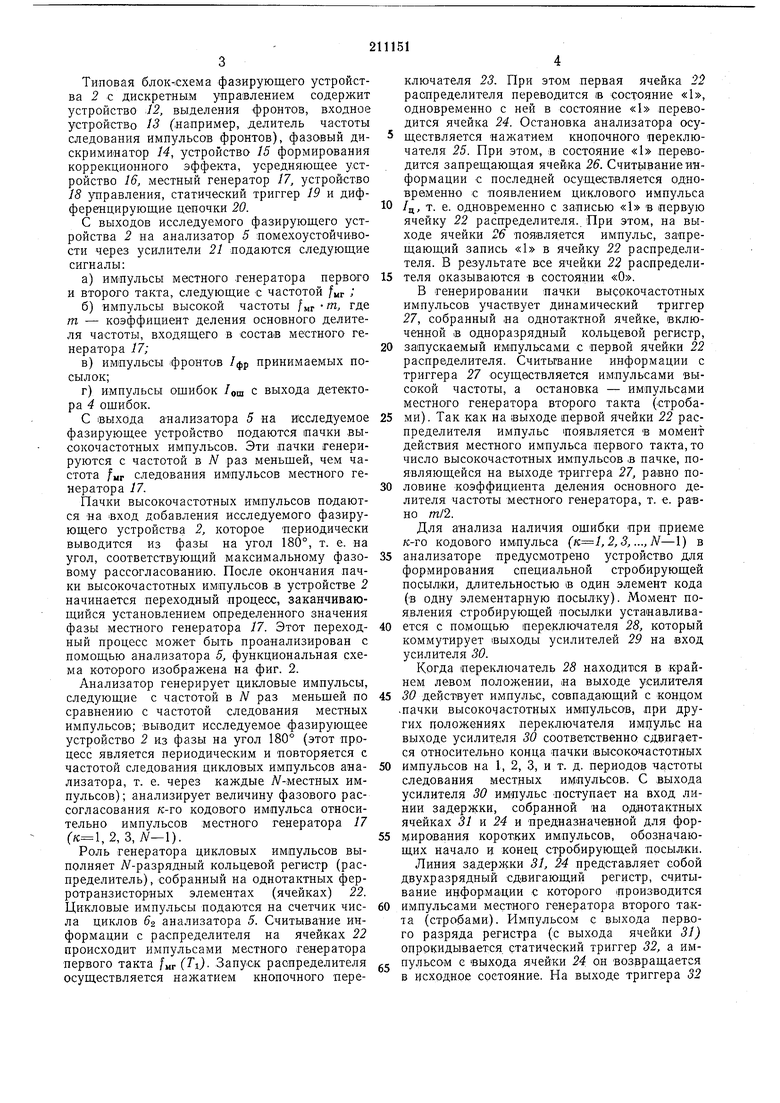

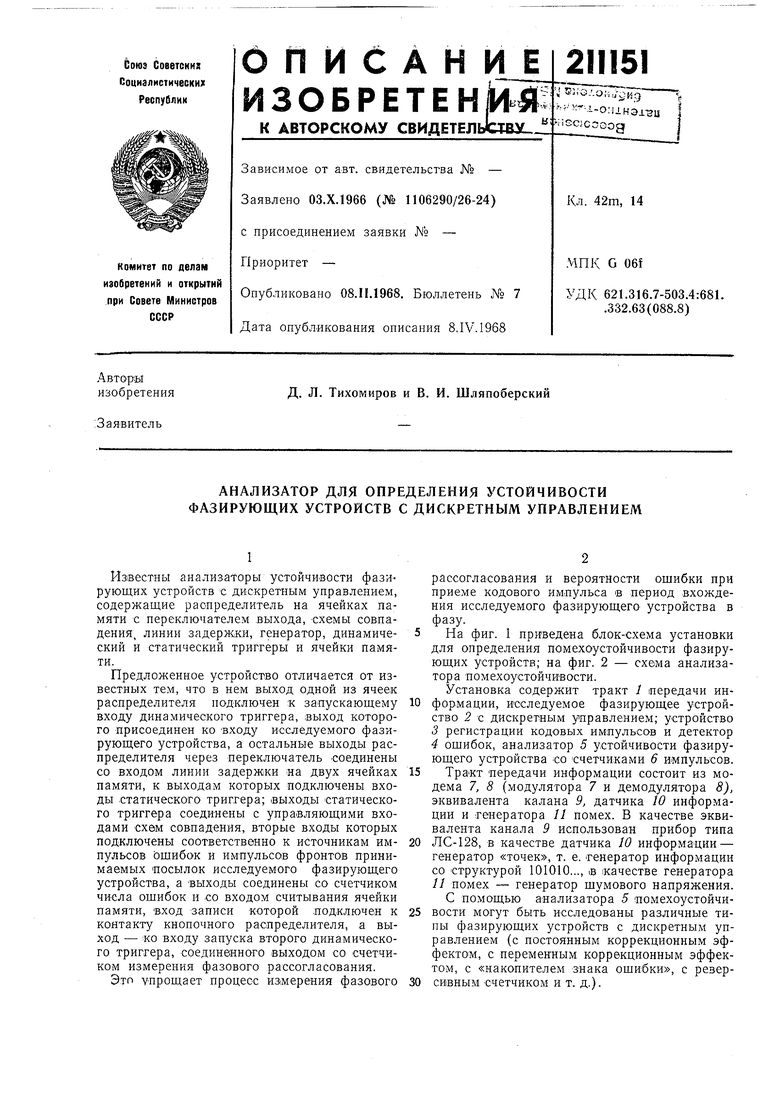

На фиг. 1 приведена блок-схема установки для определения помехоустойчивости фазирующих устройств; на фиг. 2 - схема анализатора помехоустойчивости. Установка содержит тракт / передачи информации, исследуемое фазирующее устройство 2 с дискретным управлением; устройство

3регистрации кодовых импульсов и детектор

4ощибок, анализатор 5 устойчивости фазирующего устройства со счетчиками 6 импульсов.

Тракт передачи информации состоит из модема 7, 8 (модулятора 7 и демодулятора 8), эквивалента калана 9, датчика 10 информации и генератора 11 помех. В качестве эквивалента канала 9 использован прибор типа

ЛС-128, в качестве датчика 10 информации -

генератор «точек, т. е. генератор информации

со структурой 101010..., iB качестве генератора

// помех - генератор щумового напряжения.

С помощью анализатора 5 помехоустойчивости могут быть исследованы различные типы фазирующих устройств с дискретным управлением (с постоянным коррекцнонным эффектом, с переменным коррекционным эффектом, с «накопителем знака ощибки, с резерТиповая блок-1схема фазирующего устройства 2 с дискретным управлением содержит устройство 12, выделения фронтов, входное устройство 13 (например, делитель частоты следования импульсов фронтов), фазовый дискриминатор 14, устройство 15 формирования коррекционного эффекта, усредняющее устройство 16, местный генератор 17, устройство 18 управления, статический триггер 19 и дифференцирующие цепочки 20.

С выходов исследуемого фазирующего устройства 2 на анализатор 5 помехоустойчивости через усилители 21 подаются следующие сигналы:

а)импульсы местного генератора первого и второго такта, следующие с частотой /«г

б)нмпульсы высокой частоты f „г f Д т - коэффициент деления основного делителя частоты, входящего в состав местного генератора 17;

в)импульсы фронтов /фр принимаемых посылок;

г)импульсы ощибок /ош с выхода детектора 4 ошибок.

С выхода анализатора 5 на исследуемое фазирующее устройство подаются пачки высокочастотных импульсов. Эти пачки генерируются с частотой в Л раз меньщей, чем частота fttr следования импульсов местного генератора 17.

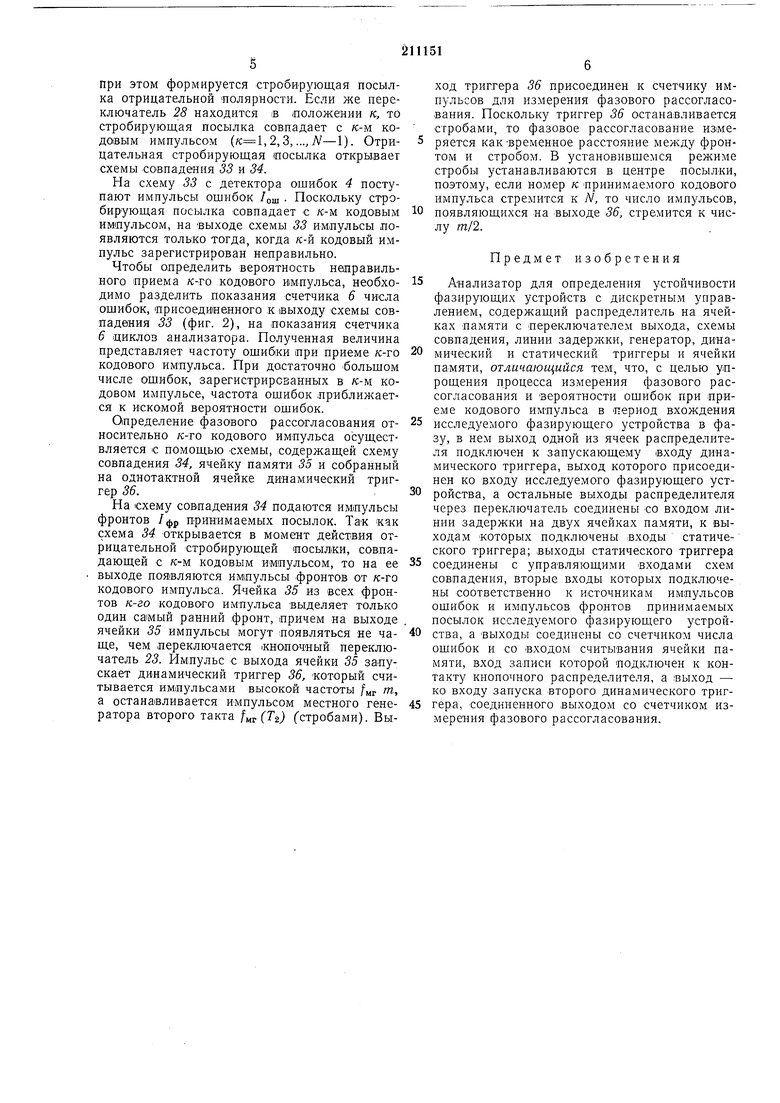

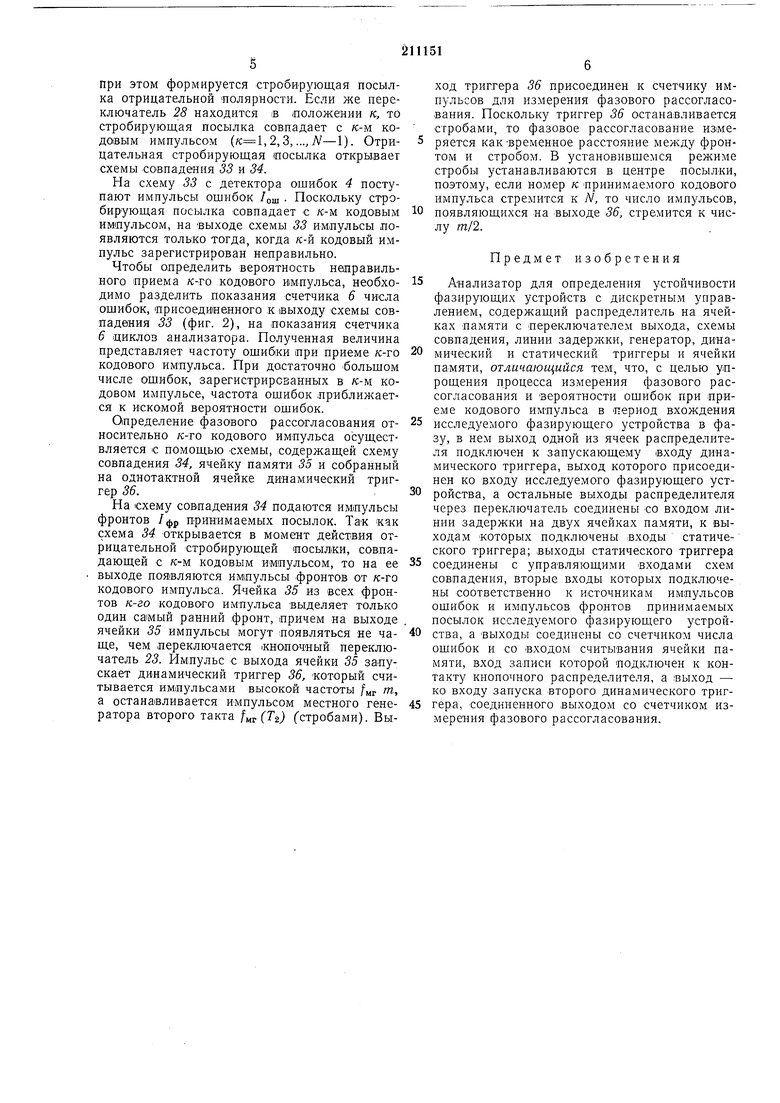

Пачки высокочастотных нмпульсов подаются на ВХОД добавления исследуемого фазирующего устройства 2, которое периодически выводится из фазы на угол 180°, т. е. на угол, соответствующий максимальному фазовому рассогласованию. После окончания пачки высокочастотных импульсов в устройстве 2 начинается переходный процесс, заканчивающийся установлением определенного значения фазы местного генератора 17. Этот переходный процесс может быть проанализирован с помощью анализатора 5, функциональная схема которого изображена на фиг. 2.

Анализатор генерирует цикловые импульсы, следующие с частотой в Л раз меньщей по сравнению с частотой следования местных импульсов; выводит исследуемое фазирующее устройство 2 нз фазы на угол 180° (этот процесс является периодическим и повторяется с частотой следования цикловых импульсов анализатора, т. е. через каждые /-местных импульсов); анализирует величину фазового рассогласования к-го кодового импульса относительно импульсов местного генератора 17 ,2, 3,//-1).

Роль генератора цикловых импульсов выцолняет Л -разрядный кольцевой регистр (распределитель), собранный на однотактных ферротранзисторных элементах (ячейках) 22. Цикловые импульсы подаются на счетчик числа циклов 6z анализатора 5. Считывание информации с распределителя на ячейках 22 происходит импульсами местного генератора первого такта /„г (T-i). Запуск распределителя осуществляется нажатием кнопочного переключателя 23. При этом первая ячейка 22 распределителя переводится в состояние «1, одновременно с ней в состояние «1 переводится ячейка 24. Остановка анализатора осуществляется нажатием кнопочного переключателя 25. При этом, в состояние «1 переводится запрещающая ячейка 26. Считывание информации с последней осуществляется одновременно с появлением цпклового импульса

/д, т. е. одновременно с записью «1 в первую ячейку 22 распределителя. При этом, на выходе ячейки 26 поя;вляется импульс, запрещающий запись «1 в ячейку 22 распределителя. В результате все ячейки 22 распределителя оказываются в состоянии «О.

В генерировании пачки высокочастотных импульсов участвует динамический триггер 27, собранный на однотактной ячейке, включенной в одноразрядный кольцевой регистр,

запускаемый импульсами с первой ячейки 22 распределителя. Считывание информации с триггера 27 осуществляется импульсами высокой частоты, а остановка - импульсами местного генератора второго такта (стробами). Так как на выходе первой ячейки 22 распределителя импульс появляется в момент действия местного импульса первого такта, то число высокочастотных импульсов в пачке, появляющейся на выходе триггера 27, равно половине коэффициента деления основного делителя частоты местного генератора, т. е. равно т/2.

Для анализа наличия ощибки при приеме к-го кодового импульса (,2,3,..., N-1) в

анализаторе предусмотрено устройство для формирования специальной стробирующей посылки, длительностью в один элемент кода (в одну элементарную посылку). Момент появления стробирующей -посылки устанавливается с помощью переключателя 28, который коммутирует выходы усилителей 29 на вход усилителя 30.

Когда переключатель 28 находится в крайнем левом положении, на выходе усилителя

30 действует импульс, совпадающий с концом .пачки высокочастотных импульсов, при других положениях переключателя импульс на выходе усилителя 30 соответственно сдвигается относительно конца пачки высокочастотных

импульсов на I, 2, 3, и т. д. периодоэ частоты следования местных импульсов. С выхода усилителя 30 импульс -поступает на вход линии задержки, собранной на одяотактных ячейках 3} и 24 и предназначенной для формирования коротких импульсов, обозначающих начало и конец стробирующей посылки. Линия задержки 31, 24 представляет собой двухразрядный сдвигающий регистр, считывание информадин с которого производится

импульсами местного генератора второго такта (стробами). Импульсом с выхода первого разряда регистра (с выхода ячейки 31) опрокидывается статический триггер 32, а нмпри этом формируется стробирующая поськака отрицательной Полярности. Если же переключатель 28 находится в /положении к, то стробирующая посылка совпадает с к-м кодовым импульсом (,2,3,.... Л-1). Отрицательная стробирующая посылка открывает схемы совпадения 33 и 34. На схему 33 с детектора ошибок 4 поступают импульсы ощибок /ош Поскольку стробирующая посылка совпадает с к-м кодовым импульсом, на выходе схемы 33 импульсы появляются только тогда, когда /с-й кодовый импульс зарегистрирован неправильно. Чтобы определить вероятность неправильного приема к-го кодового импульса, необходимо разделить показания счетчика 6 числа ошибок, присоединенного к выходу схемы совпадения 33 (фиг. 2), на показания счетчика 6 циклов анализатора. Полученная величина представляет частоту ошибки при приеме /с-го кодового импульса. При достаточно большом числе ошибок, зарегистрирсзанных в /с-м кодовом импульсе, частота ошибок приближается к искомой вероятности ошибок. Определение фазового рассогласования относительно /с-го кодового импульса осуществляется с помощью схемы, содержащей схему совладения 34, ячейку памяти 35 и собранный на однотактной ячейке динамический триггер 36. На схему совпадения 34 подаются импульсы фронтов /фр принимаемых посылок. как схема 34 открывается в момент действия отрицательной стробирующей посылки, совпадающей с к-м кодовым импульсом, то на ее выходе появляются импульсы фронтов от к-го кодового импульса. Ячейка 35 из всех фронтов к-го кодового импульса выделяет только один самый ранний фронт, причем па выходе ячейки 35 импульсы могут появляться не чаще, чем переключается .кнопочный переключатель 23. Импульс с выхода ячейки 35 запускает динамический триггер 36, который считывается импульсами высокой частоты /„г т, а останавливается импульсом местного генератора второго такта 1(1) (стробами). Выход триггера 36 присоединен к счетчику импульсов для измерения фазового рассогласования. Поскольку триггер 36 останавливается стробами, то фазовое рассогласование измеряется какВременное расстояние между фронтом и стробом. В установившемся стробы устанавливаются в центре посылки, поэтому, если номер к принимаемого кодового импульса стремится к Л , то число импульсов, появляющихся на выходе 36, стремится к числу т/2. Предмет изобретения Анализатор для определения устойчивости фазирующих устройств с дискретным управлением, содержащий распределитель на ячейках памяти с переключателем выхода, схемы совпадения, линии задержки, генератор, динамический и статический триггеры и ячейки памяти, отличающийся тем, что, с целью упрощения цроцесса измерения фазового рассогласования и вероятности ошибок при приеме кодового импульса в период вхождения исследуемого фазирующего устройства в фазу, в нем выход одной из ячеек распределителя подключен к запускающему входу динамического триггера, выход которого присоединен ко входу исследуемого фазирующего устройства, а остальные выходы распределителя через переключатель соединены со входом линии задержки на двух ячейках памяти, к выходам которых подключены входы статического триггера; выходы статического триггера соединены с управляющими входами схем совпадения, вторые входы которых подключены соответственно к источникам импульсов ошибок и импульсов фронтов принимаемых посылок исследуемого фазирующего устройства, а выходы соединены со счетчиком числа ошибок и со входом считывания ячейки памяти, вход записи которой подключен к контакту кнопочного распределителя, а выход - ко входу запуска второго динамического триггера, соединенного выходом со счетчиком измерения фазового рассогласования.

г/г/

Риг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Приемник двухтонального многочастотного сигнала | 1990 |

|

SU1758909A1 |

| Устройство для декодирования циклических кодов | 1985 |

|

SU1241480A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| УСТРОЙСТВО для ФАЗИРОВАНИЯ ПО РАБОЧИЛ\ ПОСЫЛКАМ | 1969 |

|

SU254558A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1554153A1 |

| Устройство для синхронизации кодовых комбинаций,ограниченных стандартными паузами | 1977 |

|

SU660289A2 |

Даты

1968-01-01—Публикация