Известно устройство для формирования вычетов по модулю три, содержащее регистр с с двумя феррит-транзисторными ячейками на разряд с выходами прямым и обратным кодом соответственно и логическую сеть на трансформаторах.

Предлагаемое устройство отличается от известных тем, что в нем выход ячейки обратного кода нечетного разряда регистра соединен с обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками передачи «О, «1 и «2 предыдущего четного разряда. Выход ячейки прямого кода предыдущего нечетного разряда регистра соединен с обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками трансформаторов передачи «2, «О и «1 предыдущего четного разряда. Выход ячейки обратного кода четного разряда регистра соединен с входными обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками трансформаторов передачи «О, «1 и «2 предыдущего нечетного разряда. Выход ячейки прямого кода предыдущего четного разряда соединен с обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно подключены к выходным

обмоткам трансформаторов передачи «1, «2 и «О предыдущего нечетного разряда. Это позволит повысить надежность и быстродействие устройства, а также уменьшить количество оборудования.

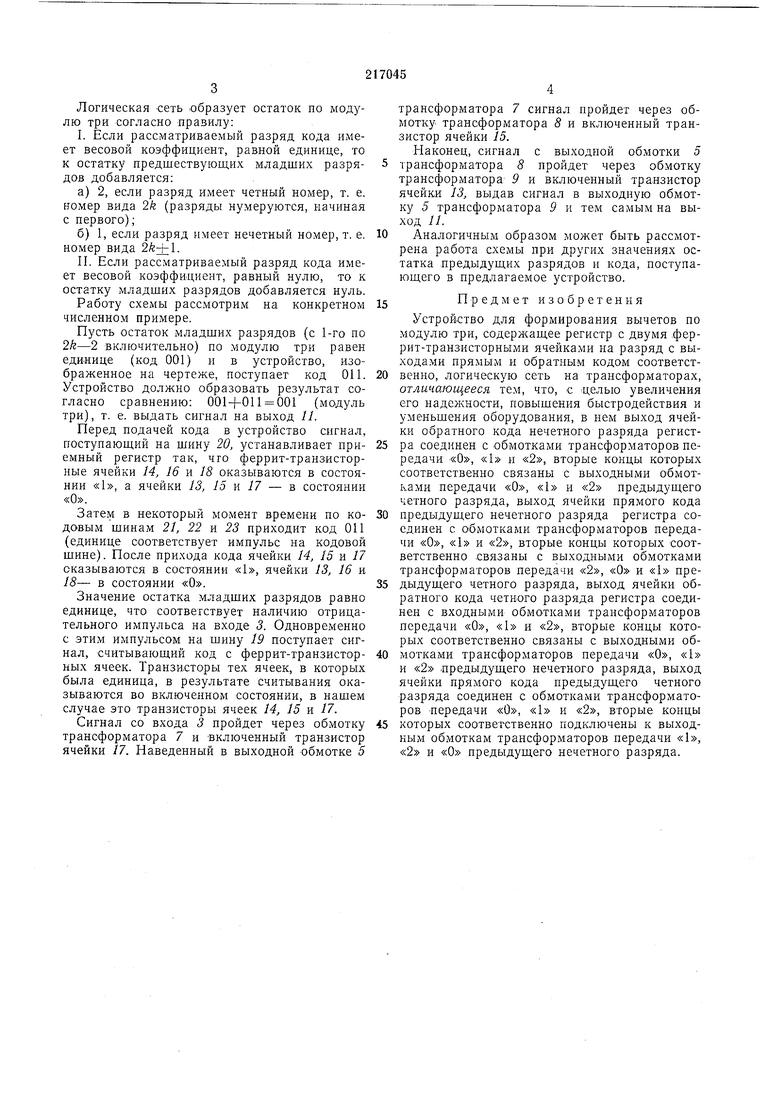

На чертеже изображена принципиальная схема устройства.

Устройство содержит феррит-транзисторные ячейки 1, вход 2 «О, вход 3 «1, вход 4

«2, выходную обмотку 5 трансформатора, трансформаторы 6-9 логической сети, выход 10 «О, выход 11 «1, выход 12 «2, ферриттранзисторные ячейки 13-18 приемного регистра, шину 19 считывания с ячеек регистра,

щину 20 установки ячеек, кодовую щину 21, кодовую шину 22, «2k-1 -ю кодовую щину 23.

На чертеже изображены три разряда устройства. В состав устройства входят приемный регистр, образованный феррит-транзисторными ячейками 13-18, и логическая сеть, которую составляют трансформаторы 6-9.

Сигналы, соответствующие значению остатка по модулю три младщих (с 1-го по 2/г - 2 включительно) разрядов кода, поступают на один из входов устройства. Суммарное значение остатка с учетом трех рассматриваемых разрядов поступает на один из выходов. Логическая -сеть образует остаток по модулю три согласно правилу: I. Если рассматриваемый разряд кода имеет весовой коэффициент, равной единице, то к остатку предшествующих младших разрядов добавляется: а)2, если разряд имеет четный номер, т. е. ьомер вида 2/г (разряды нумеруются, начиная с первого); б)1, если разряд имеет нечетный номер, т. е. Ю номер вида 2k+l. и. Если рассматриваемый разряд кода имеет весовой коэффициент, равный нулю, то к остатку младших разрядов добавляется нуль. Работу схемы рассмотрим на конкретном 15 численном примере. Пусть остаток младших разрядов (с 1-го по 2k-2 включительно) по модулю три равен единице (код 001) и в устройство, изображенное на чертеже, поступает код 011. 20 Устройство должно образовать результат согласно сравнению: 001+011 001 (модуль три), т. е. выдать сигнал на выход //. Перед подачей кода в устройство сигнал. поступающий на шину 20, устанавливает при- 25 емный регистр так, чго феррит-транзисторные ячейки 14, 16 и 18 оказываются в состоянии «1, а ячейки 13, 15 н 17 - в состоянии «О. Затем в некоторый момент времени по ко- 30 довым шинам 21, 22 и 23 приходит код 011 (единице соответствует импульс на кодовой шине). После прихода кода ячейки 14, 15 и 17 оказываются в состоянии «1, ячейки 13, 16 и 18- в состоянии «О. Значение остатка младших разрядов равно единице, что соответствует наличию отрицательного импульса на входе 3. Одновременно с этим импульсом на шину 19 поступает сигнал, считывающий код с феррит-транзистор- 40 ных ячеек. Транзисторы тех ячеек, в которых была единица, в результате считывания оказываются во включенном состоянии, в нашем случае это транзисторы ячеек 14, 15 и 17. Сигнал со входа 3 пройдет через обмотку 45 трансформатора 7 и включенный транзистор ячейки 17. Наведенный в выходной обмотке 5 5 35 трансформатора 7 сигнал пройдет через обмотку трансформатора 8 и включенный транзистор ячейки 15. Наконец, сигнал с выходной обмотки 5 трансформатора 8 пройдет через обмотку трансформатора 9 и включенный транзистор ячейки 13, выдав сигнал в выходную обмотку 5 трансформатора 9 и тем самым на выход 11. Аналогичным образом может быть рассмотрена работа схемы при других значениях остатка предыдущих разрядов и кода, поступающего в предлагаемое устройство. Предмет изобретения Устройство для формирования вычетов по модулю три, содержащее регистр с двумя феррит-транзисторными ячейками на разряд с выходами прямым и обратным кодом соответственно, логическую сеть на трансформаторах. отличающееся тем, что, с целью увеличения его надежности, повыщения быстродействия и уменьшения оборудования, в нем выход ячейки обратного кода нечетного разряда регистра соединен с обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками передачи «О, «1 и «2 предыдущего четного разряда, выход ячейки прямого кода предыдущего нечетного разряда регистра соединен с обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками трансформаторов передачи «2, «О и «1 предыдущего четного разряда, выход ячейки обратного кода четного разряда регистра соединен с входными обмотками трансформаторов передачи «О, «1 и «2, вторые концы которых соответственно связаны с выходными обмотками трансформаторов передачи «О, «1 и «2 предыдущего нечетного разряда, выход ячейки прямого кода предыдущего четного разряда соединен с обмотками трансформаторов лередачи «О, «1 и «2, вторые концы которых соответственно подключены к выходным обмоткам трансформаторов передачи «1, «2 и «О предыдущего нечетного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ИНВЕРТИРУЮЩИЙ РЕГИСТР.ВОГООЮЗНАЯ^^^^•^•Ш1штт^''Б лис ТЕТКА | 1972 |

|

SU332578A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ ПОДЪЕМНО-ТРАНСПОРТНЫХ И ШАХТНЫХ УСТАНОВОК | 1970 |

|

SU270348A1 |

| КОММУТАТОР ПЕРВОЙ СТУПЕНИ ДВУХСТУПЕНЧАТОЙ | 1973 |

|

SU369709A1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU311403A1 |

| Дешифратор | 1974 |

|

SU572922A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1967 |

|

SU198128A1 |

| Преобразователь двоичного кода во временной интервал | 1981 |

|

SU1039028A1 |

Даты

1968-01-01—Публикация