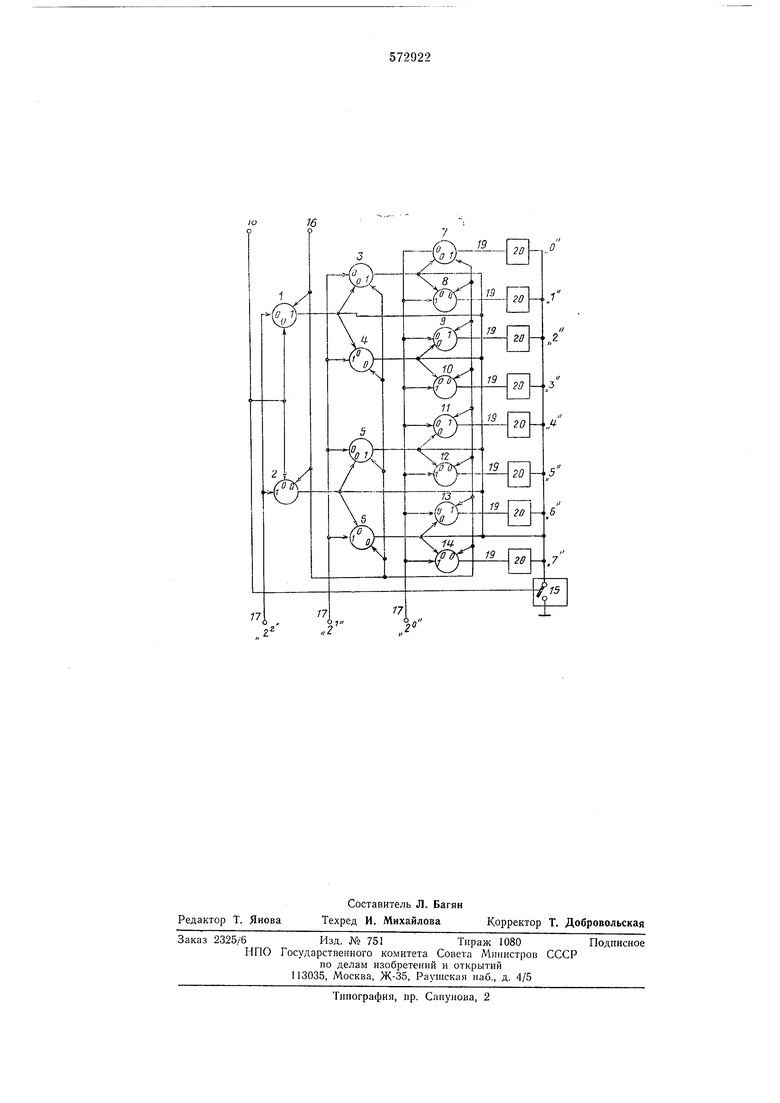

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах, построенных на феррит-транзисторных элементах. Известен дешифратор на ферротранзисторных элементах, использующий принцип запрета записи и выдачи информации 1. Однако известное устройство требует значительного количества мощных усилителей тока и технологически . Известен дещифратор, содержащий ферриттранзисторные ячейки, входные обмотки которых подключены к разрядным щинам, шину опроса, соединенную со входом управления ключа, который связан с выходами дещифратора через нагрузки 2. Однако это устройство обладает низкой нагрузочной способностью. С целью повышения нагрузочной способности в предлагаемом дешифраторе выходы каждой феррит-транзисторной ячейки старшего разряда подключены соответственно к обмоткам считывания двух феррит-транзисторных ячеек последующего младшего разряда и через ключ - к земляной шине, а обмотки считывания феррит-транзисторных ячеек самого старшего разряда соединены с шиной опроса. На чертеже представлена принципиальная электрическая схема предложенного устройства. Дещифратор содержит феррит-транзисторные ячейки 1 -14, электронный ключ 15, шину 16 подготовки, входные (разрядные) шины 17, шину 18 опроса, выходные шины 19, внешнне нагрузки 20 дешифратора. Ячейки 1, 2 являются ячейками самого старщего разряда, их выходы подключены соответственно к обмоткам считывания ячеек 3-6 младшего разряда и к электронному ключу 15. В свою очередь, выходы ячеек 3-6 также подключены соответственно к обмоткам счнтывания ячеек 7-14 самого младшего разряда н к электронному ключу 15. Выходы ячеек 7- 14 являются непосредственно выходами дешифратора и связаны по выходным шинам 19 с внешними нагрузками дешифратора 20 и с электронным ключом 15. По числу выходов дешифратора в схеме образуется восемь направлений считывания, каждое из которых состоит из трех ячеек, составляющих последовательную цепь передачи информации от старщего разряда к самому младщему. Например, нри соответствующих условиях направление из ячеек 1, 3, 7 выдает позиционный код «О, направление из ячеек 1, 3, 8 - позиционный код «1, направление из ячеек 1, 4, 9 - позиционный код «2 и т. д. Шина подготовки

16 соединена с обмоткамн всех ячеек, шина Diipoca 18 - только с обмотками считываиия ячеек самого старшего разряда и с входом возбуждения электронного ключа. Входные 1НИ11Ы 17 нодключены к ячейкам соответствующих ио весу разрядов. В исходном состоянии сигналы на устройстве не поступают.

В первом такте на шину 16 поступает извне сигнал подготовки, который производит запись в ячейки 1, 3, 5, 7, 9, 11 и 13 и стирает информацию в ячейках 2, 4, 6, 8, 10, 12 и 14 без выдачи информации, так как электронный ключ 15 в этот момент не возбужден.

Во втором такте на входные шины 17 поступает трехразрядный двоичный код, подлежаи ий дешифрации, с весами разрядов «2°, «2, «2. Если поступаюш,ий в разряд код соответствует нулю, то входной импульс отсутствует, состояние ячеек в этом разряде дешифратора не меняется. Если поступающий в разряд код соответствует единице, то входной импульс стирает информацию в подготовительных ячейках этого разряда и подготаввливает другие ячейки этого разряда. В нагрузках ячеек, у которых стирается информация, токи не протекают, так как электронный ключ в этот момент не возбужден.

В третьем такте на шину 18 подается сигнал опроса дешифратора. Одна из ячеек 1 или 2 самого старшего разряда дешифратора срабатывает и выдает сигнал в нагрузку, т. е. на считывание ячеек 3, 4 или 5, 6 младшего разряда дешифратора. Так как сигнал опроса дешифратра поступает также и на возбул дение электронного ключа 15, то в этом такте ключ выдает стробирующий импульс для всех ячеек дешифратора, в соответствующих подготовленных ячейках происходит последовательное считывание ячеек от старших разрядов к младшим по одному из восьми направлений считывания вплоть до ячейки самого младшего разряда (одна из ячеек 7- 14). Ячейки 7-14 являются выходными ячейками дешифратора и выдают дешифрируемый позиционный код . На выходе одной из них появляется сигнал, поступающий по выходной шине 19 в нагрузку 20. Подключение ячеек 1-6 к электронному ключу необходимо для исключения возможности появления в их нагрузочных ячейках одновременного считывания и записи при подготовке.

Использование связей по считыванию между ячейками позволяет строить дешифраторы на любое число входов (без применения принципов запрета, увеличивающих аппаратурные

и технологические затраты) так как отсутствуют ограничения на количество ферротранзисторных ячеек в каждом направлении считывания. Выход ячеек старших разрядов в

этом случае электрически не связаны с транзисторами и коллекторными обмотками ячеек младших разрядов и любое увеличение количества ячеек в каждом направлении считывания (увеличение числа входов дешифратора) не увеличивает нагрузку для ячеек. Каждая ячейка старшего разряда остается подключенной только к обмоткам считывания двух ячеек младшего разряда. Нагрузочная способность выходов такого дешифратора выше известных, так как выходами его являются выходы обычных ферротранзисторных ячеек (нагрузочная способность - четыре ячейки), в то время как выходы ферротранзисторных ячеек, соединенных в схему

И, имеют более низкую нагрузочную способность, которая понижается с увеличением числа входов в схеме И. Для схемы И, состоящей из трех ячеек, нагрузочная способность составляет одну ячейку.

Надежность работы дешифратора также повышается за счет отсутствия факторов, ухудшающих параметры выходного сигнала (неодновременность отпирания транзисторов в схемах И, падение напряжения на коллекторных обмотках и транзисторах последовательно соединенных ячеек схем И) и за счет облегченного режима работы ячеек (нагрузка для каждой ячейки составляет две ячейки при

максимальной нагрузке в четыре ячейки).

Формула изобретения

40

Дешифратор, содержащий феррит-транзисторные ячейки, входные обмотки которых подключены к разрядным шинам, шину опроса, соединенную со входом управления ключа, который связан с выходами дешифратора через нагрузки, отличающийся тем, что, с целью повышения нагрузочной способности, выходы каждой феррит-транзисторной ячейки старшего разряда подключены, соответственно к обмоткам считывания двух феррит-транзисторных ячеек последующего младшего разряда и через ключ - к земляной шине, а обмотки считывания феррит-транзисторных ячеек самого старшего разряда соединены с шиной опроса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1973 |

|

SU479109A1 |

| Дешифратор | 1977 |

|

SU612405A1 |

| Дешифратор | 1978 |

|

SU809564A1 |

| Быстродействующий параллельный преобразователь кода Баркера в двоичный код | 1960 |

|

SU147026A1 |

| Двоичный счетчик с устройством контроля | 1973 |

|

SU515285A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК | 1964 |

|

SU219900A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1635203A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

Авторы

Даты

1977-09-15—Публикация

1974-12-08—Подача