Изобретение относится к области автоматики и вычислительной техники и предназначено для адресования подьемно-транспортных л-1 шахтных установок без адресоносителей на подвижных объектах.

Известны устройства адресования без адресопосителя на подвижиом объекте.

Предлагаемое устройство отличается от известных тем, что выход матрицы памяти через элемент выхода адресной информации соединен с входом, командной схемы, первый выход которой соединен с входом распределителя и с входом триггера, выход которого подключен к питающей шине распределителя.

Это позволяет автоматизнровать обслуживание участков транспортной системы, на которых не может измениться порядок следования подвижных объектов или их адрес.

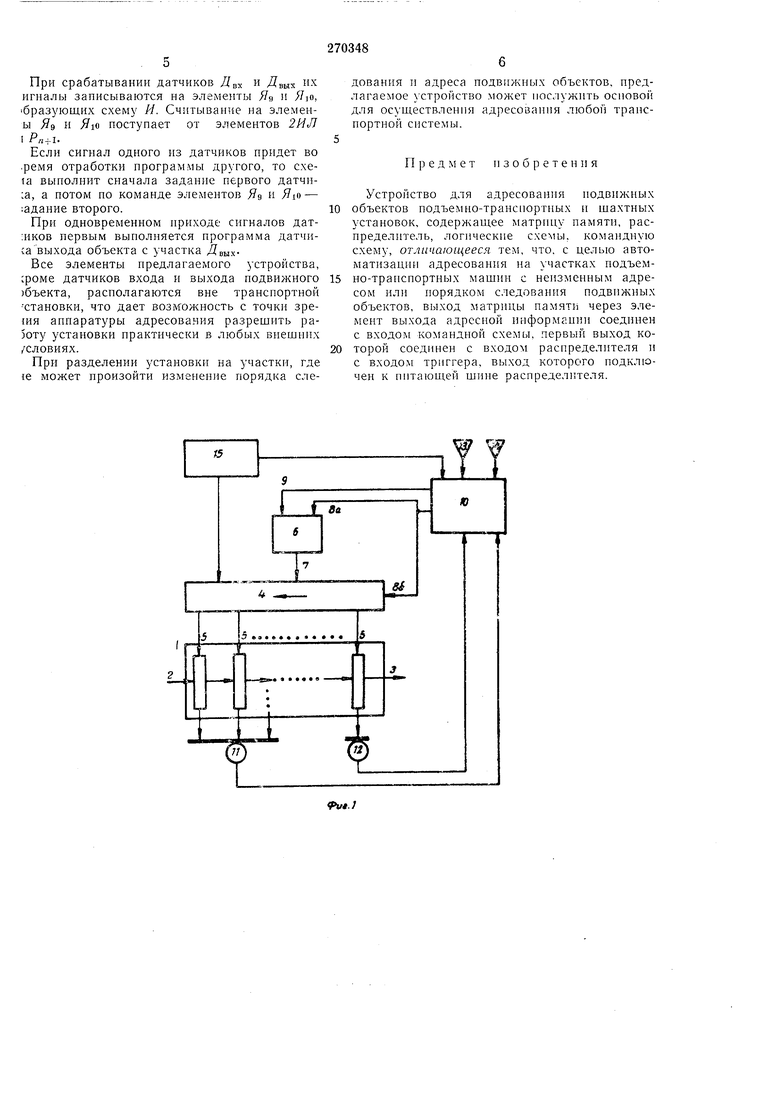

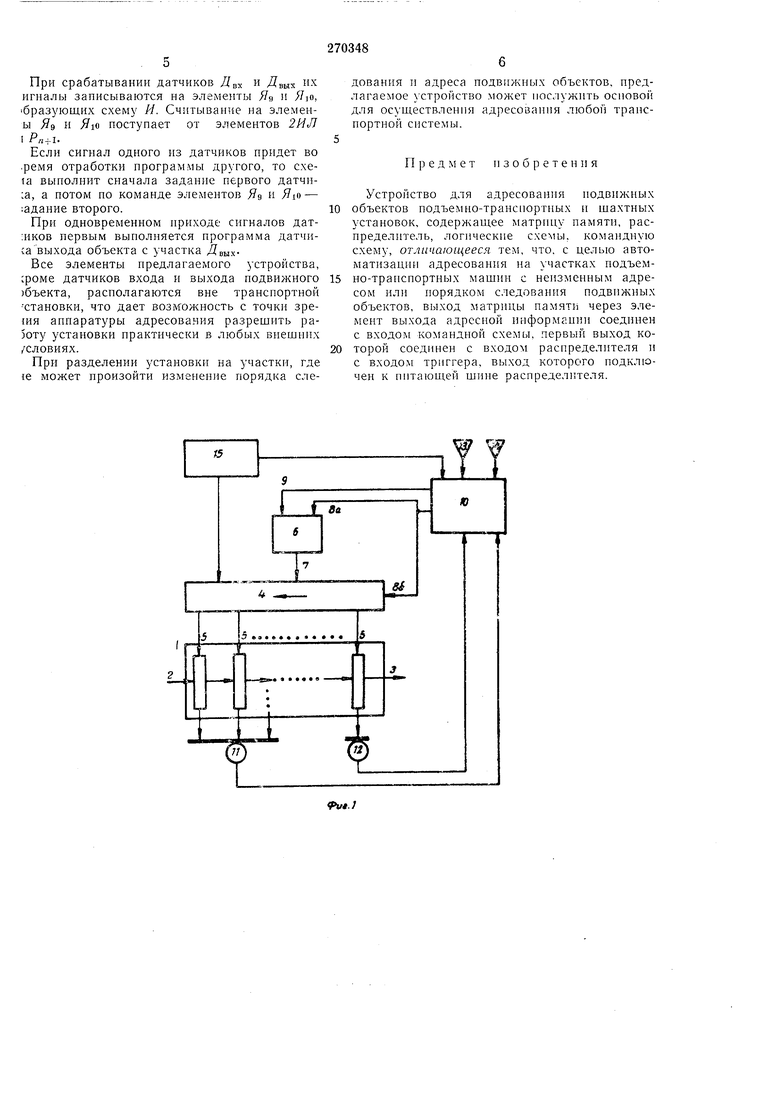

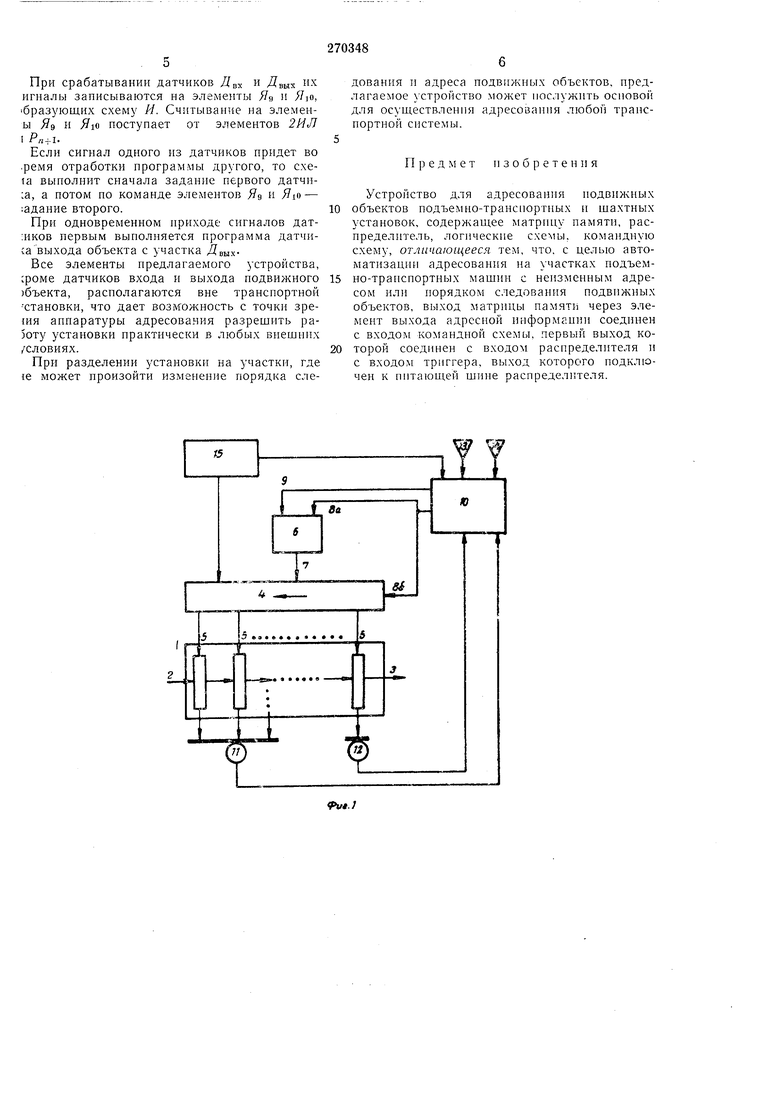

Блок-схема предлагаемого устройства дана на фиг. 1, где - матрица памяти; 2 - ввод адресной информации в матрицу памяти; 3 - вывод адресной информации из матрицы памяти; 4 - распределитель; 5 - шины считывания элементами распределителя ячеек матрицы памяти; 6 - триггер с ключевым выходом; 7 - шина питания элементов распределителя; 8а и 86 - шины включения триггера и запуска распределителя; 9 -шина выключения триггера; 10 - командная схема; И - элемент контроля продвижения адресной информации вдоль матрицы памяти; 12 - элемент выхода адресной информации с матрицы памяти; 13 - датчик входа подвижного объекта на участок; 14 - датчик выхода подвижного объекта с участка; 15 - генератор тактовых импульсов.

Стрелками внутри блоков / и 4 показаны направлення движения адресно ниформацин вдоль матрицы памяти и сигнала вдоль распределителя.

Пример выиолнения устройства на ферриттранзисторных ячейках показан на фиг. 2.

Индексами «1. «О и «Э обозначены соответственно вход записи, считывания и эмиттер транзистора феррит-транзисторного элемента.

Основу устройства образует набор параллельных регистров, которые составляют матрицу: элементы , Afis,..., Каждый регистр образует ряд матрнцы, каждый элемент одного ряда запнсывает ннформацню на вход последуюпл,его.

Элементы регистра, имеющие одинаковый порядковый номер (первую цифру в обозначении элемента), образуют строки матрицы.

Адрес подвижного объекга записывается в строку в виде двоичного кода. Количество регистров (элементов в строке) зависит от числа адресов и принятого двоичного кода. Все адреса нодвил ных объектов, находящихся в данный момент иа участке, записаны в строках матрицы в порядке поступления объектов на участок. Количество строк (элементов в регистре) равно или больше количества подвижных объектов, которые могут одновременно находиться на участке.

П-ри заходе на участок каждого нового подвижного объекта все адреса поочередно переписываются с предыдущей на последующую строчку, освоболчдая входную строку для приема нового адреса.

С этой целью на каледую строку матрицы поданы считывающие импульсы от элементов распределителя, который содержит на один элемент больще, чем регистры. Его элементы обозначены на схеме PI; Р,... Р„ Рпл ь

На раснределитель поданы двухтактные считывающие импульсы от генераторов имнульсов ГИ, выполненный, например, на транзисторном мультивибраторе и ферриттранзисторных элементах-формирователях.

Эмиттеры транзисторов расиределителя занитаны через триггер Т с ключевым выходом.

Кроме феррит-транзисторных элементов матрицы и расиределителя, в схеме устройства используются феррит-транзисторные элементы, обозначенные на фиг. 2 индексами Я, которые обеспечивают необходимые блокировки.

При заходе иодвил ного объекта на участок сработает датчик входа Двх Его импульс считает ранее записанную информацию с ячейки Я, заблокировав тем самым ввод в схему сигнала от датчика выхода Двых на время отработки программы датчика входа.

В результате срабатывания элемента Hi будет записан сигнал в ячейку Я, который под воздействием считывающих продвигающих импульсов от генератора импульсов продвинется в элемент Яз, а затем - в PI и так далее вдоль всех элементов распределителя. Одновременно при срабатывании элемента Яз включается триггер Т, подав питание на транзисторы элементов распределителя.

При прохождении сигнала но раснределителю будут последовательно во времени считаны выходная строчка матрицы, затем примыкающая к ней строчка и т. д. Все адреса подвижных объектов, хранящиеся в памяти матрицы, будут, таким образом, поочередно переписаны в последующую строчку. На освободивщуюся входную строчку матрицы по запросу элементов Р„+1 (с памяти адресователя или дополнительного выходного устройства, принявшего адрес от предыдущего аналогичного описываемому устройства адресования) перепищется адрес вновь защедщего на участок объекта. Запращивающий выход элемента Pn+i обозначен на фиг. 2 надписью: к У А.

Одновременно элемент Рпл подает сигнал 1 в ячейку Яь подготовив схему к дальнейшей работе.

адресов остальных объектов и выведен на выход матрицы. Оттуда он может ноступать в дешифратор, в дополнительное выходное устройство для передачи в устройство адресования следующего участка и т. д.

Команду на работу схемы в этом подает датчик выхода подвижного объекта с участка Двых- Сигнал датчика считывает информацию с ячейки Ях и записывает / в

элемент и в предыдущем случае, при срабатывании ячейки Я запишется / в элемент Яз, откуда под воздействием тактовых сигпалов генератора имиульсов ГИ нродвинется в

ячейку Яз, а затем в элементы распределителя.

Одновременно ячейка Яз включит триггер Г,

а ячейка Я-2 считает сигнал с элемента Я,

переписав его тем самым в элемент ЯзПри прохождении сигнала вдоль распределителя будут поочередно считываться строчки

матрицы. Когда считывается первая, занятая

адресной информацией, строчка, адрес иерепищется в последующую строку матрицы.

В то же время логические элементы ИЛИ,

1ИЛ либо 2ИЛ, которые контролируют продвижение адресной информации в матрице, подадут считывающий сигнал на ячейку Ял. Сработав, последняя через элемент задержки выключит триггер Т.

Задержка может быть выполнена, например, на феррит-транзисторной ячейки Яв, на обмотку считывания. которой подан постоянный ток подмагничивания. Выключившись, триггер Т лищит питания

транзисторы элементов распределителя. Под воздействием считывающих сигналов генератора имнульсов / хранящаяся информация в одном из элементов распределителя будет стерта, что предотвратит продвижение остальных адресов, записанных в матрице.

Если информация об адресе объекта продвигалась по внутренним строкам матрицы, то команду на выключение триггера Т подаст элемент 1ИЛ. Одновременно ои запишет 1 в

ячейку ЯтТранзисторы ячеек Я и Яз соединены последовательно, образуя схему И. При срабатывании элемента Яз через задержку Яо в элемент Яв также будет записана 1.

Под воздействием сигналов от генератора импульсов элементы Ят и Яв перепишут / в элементы Яб и Яз- Ячейка Яз, включив триггер, запишет 1 в первую ячейку распределителя. В результате начнется повторный цикл

работы схемы.

Аналогично схема .будет работать до тех пор, пока адрес объекта не будет считан с выходной строки матрицы. В этом случае команду на выключение триггера подает элемент 2ИЛ, сигнал в ячейку Я не запишется, а с ячейки Яв сигнал будет стерт тактовыми импульсами. В то же время элемент 2ИЛ запишет 1 в ячейку Яь подготовив схему к дальПри срабатывании датчиков Двх и их игиалы записываются на элеме}1ты Яв и //lo, бразующих схему И. Считывание на элемены Яд и Яю иоступает от элементов 2ИЛ I Р«.л. Если сигнал одного из датчиков нридет во .ремя отработки нрограммы другого, то схеla выиолнит сначала задание нервого датчи:а, а йотом ио команде элементов Яд и Я in - задание второго. При одновременном нриходе сигналов дат:иков первым выполняется программа датчиса выхода объекта с участка ДвыхВсе элементы иредлагаемого устройства, фОме датчиков входа и выхода подвижного )бъекта, располагаются вне транспортной становки, что дает возможность с точки зре1ИЯ анпаратуры адресования разрешить ра5оту установки нрактически в любых внешннх /словиях. При разделении установки на участки, где le может произойти изменение порядка следования и адреса подвижных объектов, предлагаемое устройство может послужить основой для осуществления адресования любой транспортной системы. Предмет изобретения Устройство для адресования иодвижных объектов подъемно-трансиортных и шахтных установок, содержащее памяти, распределитель, логические схемы, командную схему, отличающееся тем, что. с целью автоматизации адресования на участках подъемно-трапспортных мащин с неизменным адресом или иорядком следования подвижных объектов, выход матрицы памяти через элемент выхода адресной информаиии соединен с входом командной схемы, первый выход которой соединен с входом расиределителя и с входом триггера, выход которого иодключен к питающей шине распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ | 1973 |

|

SU365715A1 |

| Устройство для адресования подвижных объектов | 1977 |

|

SU676987A2 |

| Устройство для адресования грузов установок непрерывного транспорта | 1978 |

|

SU716934A1 |

| Устройство для автоматического адресования объектов | 1979 |

|

SU867819A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДВИЖЕНИЕМ ГРУЗА НА РАЗВЕТВЛЕННЫХ КОНВЕЙЕРАХ | 1967 |

|

SU224645A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯШТАБЕЛЕРОМ | 1969 |

|

SU257577A1 |

| Устройство для обработки изображений объектов | 1987 |

|

SU1495830A1 |

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU308517A1 |

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1971 |

|

SU320075A1 |

-

Ч

Авторы

Даты

1970-01-01—Публикация