Известны устройства, содержащие запоминающие триггеры, управляемые ключевые схемы, которые входами управления подсоединены к выходам запоминающих триггеров и соединены между собой в схему, отображающую граф.

Предлагаемое устройство отличается от известных применением блока кодирования и декодирования команд, соединенного с одними входами вентилей и через коммутатор - с другими входами вентилей, и соединением выходов указанных вентилей со входами запоминающих триггеров. Указанные соединения позволяют определить характеристики связности вероятностного графа и повысить скорость выполнения указанной операции.

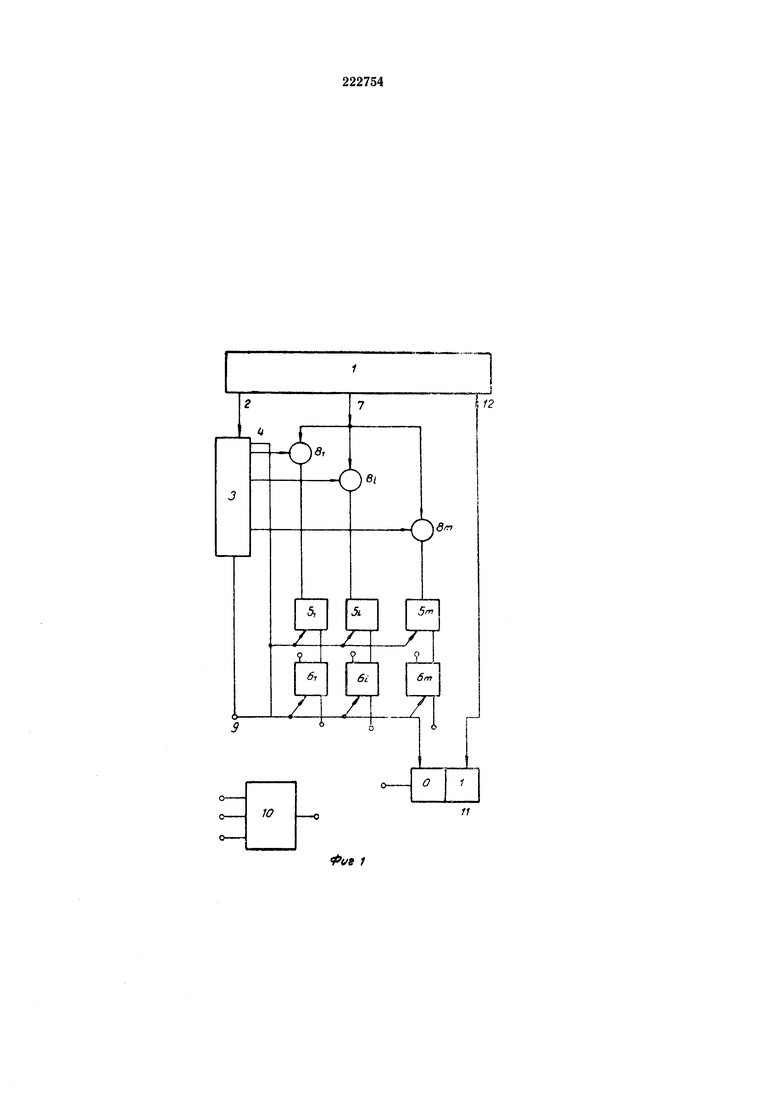

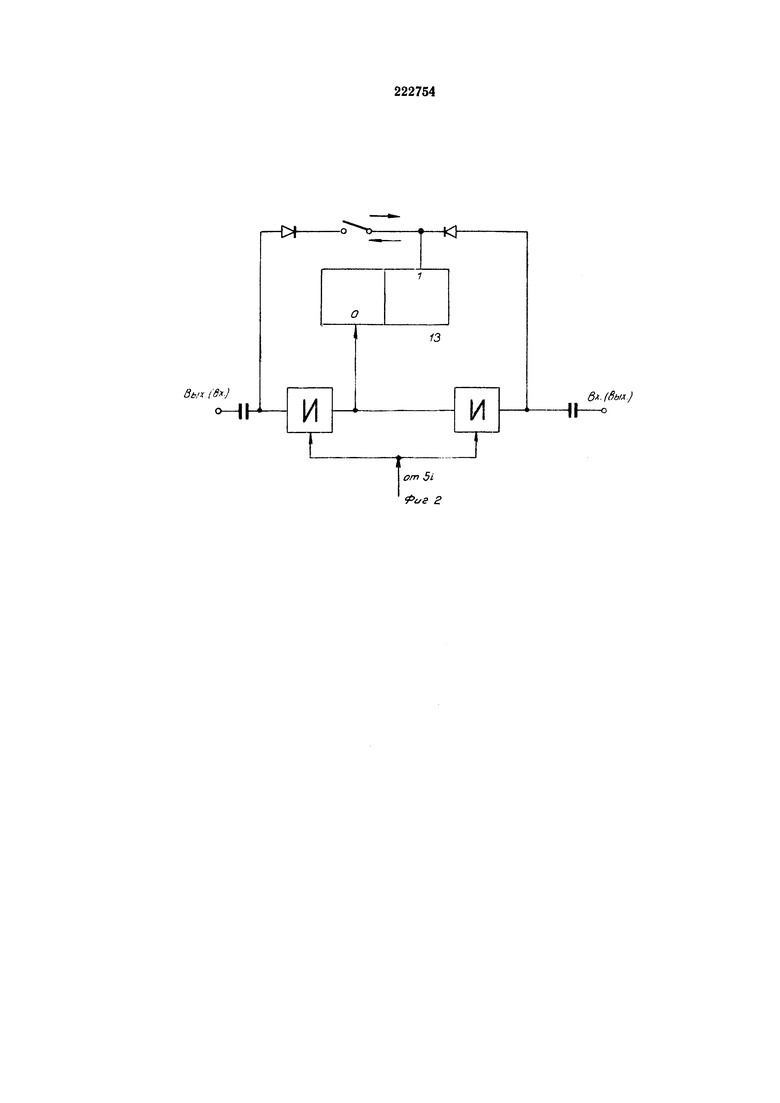

На фиг. 1 приведена схема описываемого устройства; на фиг. 2 - возможный вариант построения ключевой схемы.

Схема содержит: блок 1 кодирования и декодирования команд с электронно-вычислительной машины (ЭВМ), командную шину 2 коммутатора, электронный коммутатор 3, шину 4 сброса в «0», триггеры памяти 51, … 5i, …, 5m, управляемые ключевые схемы 61, … 6i, …, 6m, командную шину 7 вентилей, вентили 81, …, 8i, …, 8m, шину 9 проверки на проводимость, логическую схему 10, триггер 11 съема результата, шину 12 съема результата проверки на проводимость.

Функционирование устройства происходит по циклам. Каждый цикл содержит тактовые моменты τ0, τ1, …, τi, …, τm+1, τm+2, которые задаются ЭВМ, преобразуются в блоке 1 в импульсы и поступают по шине 2 в коммутатор 3, устанавливая его последовательно в состояния 0, 1, …, i, …, m+1, m+2. Коммутатор 3 в состоянии «0» выдает импульс на шину 4. Под действием этого импульса триггеры памяти 6 устанавливаются в «0» и таким образом закрывают ключевые схемы 6. В «0» устанавливаются также триггеры 13 ключевых схем (см. фиг. 2) и триггер 11. В тактовый момент τ1 вентиль 81 открыт и при наличии импульса на шине 7 триггер памяти 51 переходит в состояние «1», открывая ключевую схему 61. Наличие или отсутствие импульса на шине 7 задается ЭВМ и определяется соответственно наличием или отсутствием дуги графа в розыгрыше, соответствующем состоянию τi. Аналогично происходит функционирование в моменты τ2, …, τi, …, τm. В момент τm+1 с коммутатора 3 по шине 9 поступает импульс на испытание схемы, отображающий граф, на проводимость между отмеченными вершинами. Переброс триггера 11 в состояние «1» под действием импульса, прошедшего через схему, отображающую граф, и логическую схему 10 означает, что соответствующие отмеченные характеристики графа равны 1 или 0. В момент τm+2 информация с триггера 11 по шине 12 через блок 1 поступает в ЭВМ. Затем начинается новый цикл. Подсчет количества циклов и обработка полученной информации производится ЭВМ.

Устройство для моделирования вероятностного графа, содержащее запоминающие триггеры, управляемые ключевые схемы, которые входами управления подсоединены к выходам запоминающих триггеров и соединены между собой в схему, отображающую граф; вентили, коммутатор и блок кодирования и декодирования команд, поступающих от электронной вычислительной машины, отличающееся тем, что, с целью повышения быстродействия устройства при определении характеристик связности вероятностного графа, в нем блок кодирования и декодирования команд соединен с первыми входами вентилей и через коммутатор - с их вторыми входами, а выходы вентилей соединены со входами запоминающих триггеров.

Авторы

Даты

1968-10-29—Публикация

1967-01-30—Подача