Предложенное устройство относится к области цифровых преобразователей для интегрирования разностной частоты двух сигналов.

Известны устройства для разделения входных имиульсов реверсивного счетчика, содержащие формирователи, два триггера сравниваемых частот, триггер управления шинами реверсивного счетчика, схемы совпадения и схему «ИЛИ.

Однако в этих устройствах интегрирования разностной частоты ири помощи реверсивного счетчи ка наблюдается «мигание индикатора первых декад реверсивного счетчика из-за непрерывной работы триггеров этих декад, что делает невозможным визуальное наблюдение и затрудняет съем информации.

Предложенное устройство отличается тем, что в нем между выходом формирователей и входом реверсивного счетчика включена логическая схема, сравнивающая относительную длительность интервалов между дифференциалами фронтов обоих сигналов, так что выходы формирователей соединены со входами схем совпадения и с раздельными входами высо1кочастотного триггера, а выходы этого триггера через линии задержки подключены ко вторым входам схем совпадения, выход второго формирователя, соединенный с единичным входом высокочастотного триггера.

подключен к нулевому входу дополнительного триггера, а нулевой его выход через линию задержки включен на .вход схемы совпадения, связанной со вторым формирователем, выходы обеих схем совпадения соединены со счетными входами реверсивного счетчика и через схему «ИЛИ со входом управления реверсивного счетчика, выход схемы «ИЛИ соединен с нулевым входом триггера блокировали,

нулевой выход триггера через реле времени подключен к единичному входу, единичный выход соединен со входами обеих схем, совпадения.

Это позволяет повысить точность отсчета

текущего значения разности двух частот.

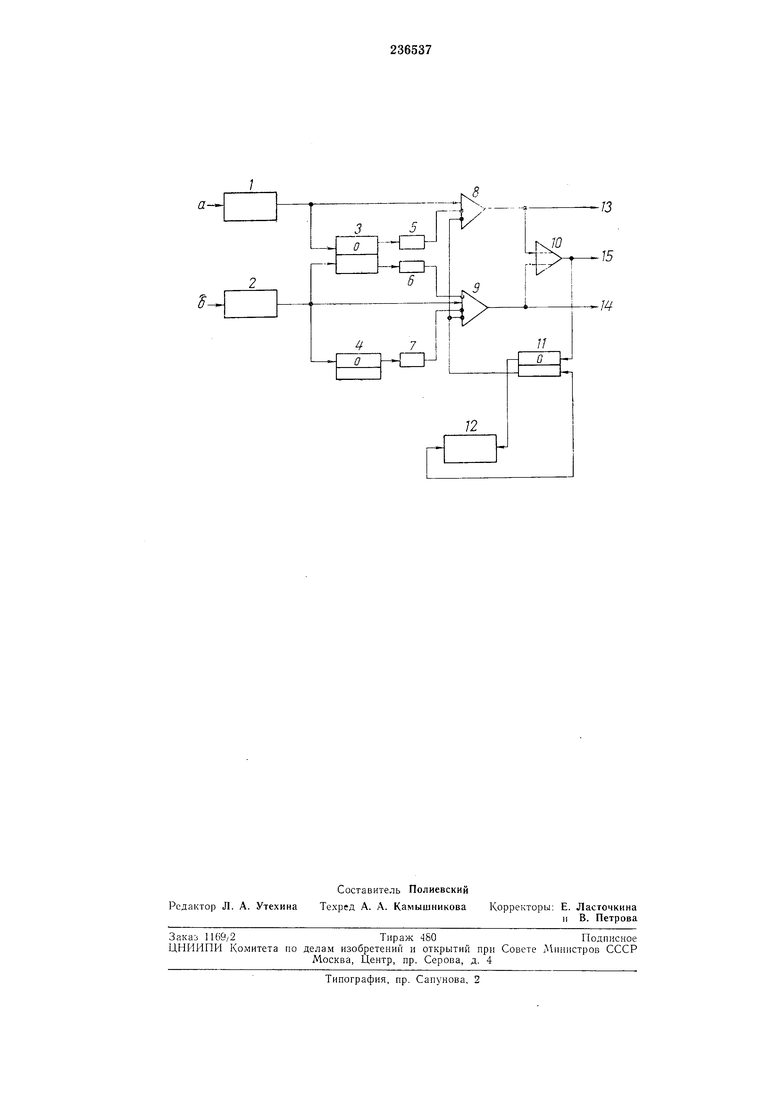

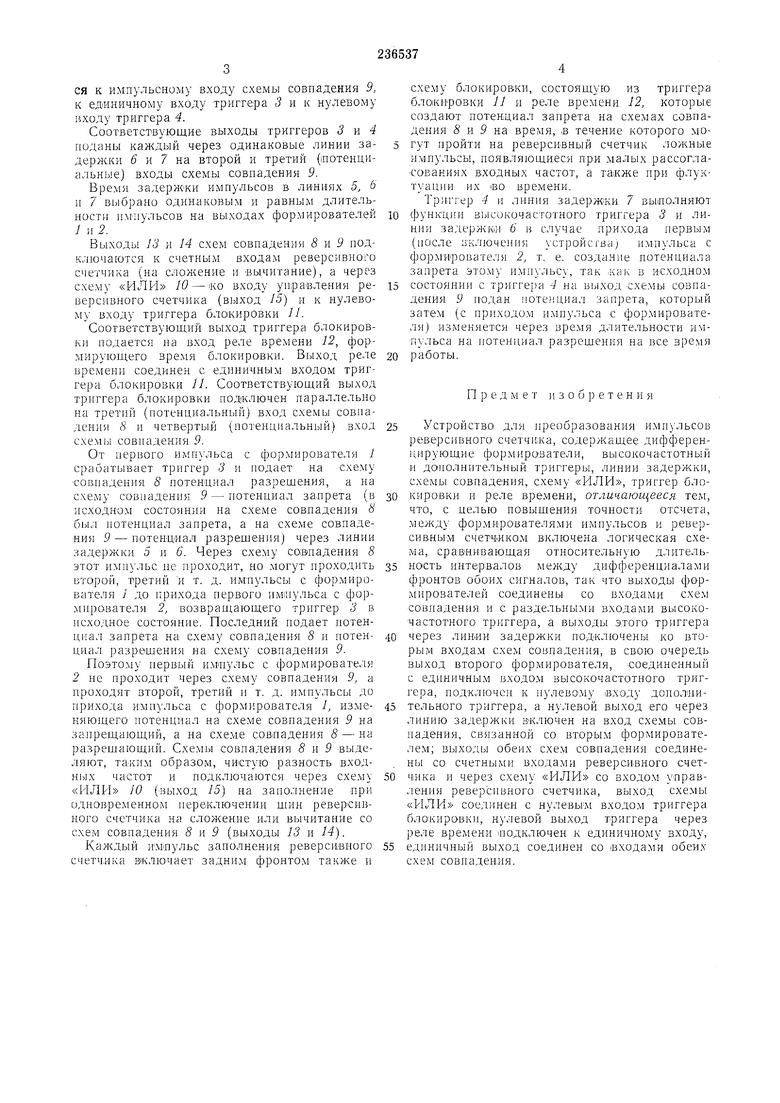

Логическая схема предложенного устройства приведена на чертеже.

Схема состоит из дифференцирующих формирователей / и 2, высокочастотного и дополнительного 4 триггеров, линий задержки 5-7, схем совпадения 8 и 9, соединенных с реверсивным счетчиком (на чертеже не показан), схемы «ИЛИ 10, триггера блокировки 1 и реле времени 12.

Выход формирователя 1 подключен к импульсному входу схемы совпадения S и к нулевому входу триггера 3. Нулевой выход этого триггера через линию задержки 5 подан на второй (потенциальный) вход схемы совпася к импульсному входу схемы совладения 9, к единичному входу триггера 3 и к нулевому входу триггера 4.

Соответствующие выходы триггеров 3 и 4 поданы каждый через одинаковые линии задержки 6 и 7 на второй и третий (потенциальные) входы схемы совпадения 9.

Время задерж ки импульсов в линиях 5, 6 и 7 выбрано одинаковым и равным длительности импульсов на выходах формирователей У и 2.

Выходы J3 и 14 схем совиадения 5 и 5 подключаются к счетным входам реверсивного счетчика (на сложение и вычитание), а через схему «ИЛИ /О - «о входу управления реверсивного счетчика (выход /5) и к нулевому входу триггера блокировки 11.

Соответствуюш,ий выход триггера блокировки подается на вход реле времени 12, формирующего время блокировки. Выход реле времени соединен с единичным входом триггера блокировки //. Соответствующий выход триггера блокировки подключен параллельно на третий (потенциальный) вход схемы совпадения 8 и четвертый (потенциальный) вход схемы совиадения 9.

От первого импульса с формирователя 1 срабатывает триггер 3 и подает на схему Совпадения 8 потенциал разрешения, а на схему совпадения 9-потенциал залрета (в исходном состоянии на схеме совпадения 6 был потенциал запрета, а на схеме совпадения 9-потенциал разрешения) через линии задержки 5 и 6. Через схему совпадения 8 этот импульс ПС проходит, но .могут ироходить второй, третий и т. д. импульсы с формирователя 1 до прихода первого имлульса с формпрователя 2, возвращающего трпггер 3 в исходное состояние. Последний иодает потенциал запрета на схему совпадения 8 и потенциал )азрешения на схему совпадения 9.

Поэтому первый имиульс с формирователя 2 не проходит через схему совпадения 9, а проходят второй, третий и т. д. импульсы до прихода импульса с формирователя 1, изменяющего потенциал на схеме совпадения 9 на залрещающий, а на схеме совладения 8 - на разрешающий. Схемы совпадения 8 и 9 выделяют, та-ким образом, чистую разность входных частот и подключаются через схему «ИЛИ 10 (ВЫХОД /5) на заполнение лри одновре.менном переключении шин реверсивного счетчика на сложение или вычитание со схем совпадения 8 и 5 (выходы 13 и 14).

Каждый имлульс заполнения реверсивного счетч.ика вичлючает задним фронтом также и

схему олокировки, состоящую из триггера блокировки 11 и реле времени 12, которые создают потенциал запрета на схемах совладения S и 9 на время, в течение которого могут пройти на реверсивный счетчик ложные имиульсы, появляющиеся при малых рассоглаСованиях входных частот, а также при флуктуации их во времени.

Триггер 4 и линия задерж1ки 7 выполняют

функции высокочастотного триггера 5 и линии задержки 6 в случае прихода первым (после включепия устройства; импульса с формирователя 2, т. е. создание потенциала запрета это.му импульсу, так как в исходном

состоянии с триггера 4 на выход схемы совпадения 9 подан потенциал запрета, который затем (с приходом импульса с формирователя) изменяется через вре.мя длительности импульса на потенциал разрешения на все вре.мя

работы.

П р е д м е т л з о б ) е т е н и я

Устройство для преобразования импульсов реверсивного счетчика, содержащее дифференцирующие формирователи, высокочастотный и дополнительный триггеры, линии задержки, схемы совпадения, схему «ИЛИ, триггер блокировки и реле времени, отличающееся тем, что, с целью повышения точности отсчета, между формирователями импульсов и реверсивным счетчиком включена логическая схема, сравнивающая относительную длительность интервалов между дифференциалами фронтов обоих сигналов, так что выходы формирователей соединены со входами схем совпадения и с раздельными входами высокочастотного триггера, а выходы этого триггера

через линии задержки подключены ко вторы.м входам схем совладения, в свою очередь выход второго формирователя, СОединенный с единичным входо.м высокочастотного триггера, подключен к пулевому еходу допол ллтельного триггера, а нулевой выход его через линию задержки включен на вход схемы совпадения, связанной со вторым формирователем; выходы обеих схем совладения соединены со счетными входами реверсивного счетЧ:ика и через схему «ИЛИ со входом управ„тения реверспвного счетчика, выход схемы «ИЛИ соединен с нулевыМ входом триггера бло кировкп, нулевой выход триггера через реле времени атодключен к единичному входу,

единичный выход соединен со входами обеих схем совпадения.

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь частотно-модулированных сигналов | 1972 |

|

SU443479A1 |

| ДИСКРЕТНЫЙ ФИЛЬТР | 1970 |

|

SU277848A1 |

| ШЧЕСКАЯ БИБЛИОТЕКА | 1970 |

|

SU261518A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ИМПУЛЬСА | 1972 |

|

SU414742A1 |

| СТАТИ СТИ Ч ЕС КИ И А НАЛ И ЗАТО РВСЕСОЮЗНАЯntTfiSTii-l •»" ч-".-("-''1HAItHihij-iLAsdiuJ БИБЛИОТЕКА | 1972 |

|

SU328476A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ УСЛОВНОЙ ДИСПЕРСИИ СЛУЧАЙНОГО ПРОЦЕССА | 1971 |

|

SU290292A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1969 |

|

SU240016A1 |

| ЦИФРОВАЯ СЕЙСМОРАЗВЕДОЧНАЯ СТАНЦИЯ | 1973 |

|

SU396648A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОБОРОТОВ | 1971 |

|

SU296138A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1971 |

|

SU427488A1 |

Даты

1969-01-01—Публикация