1

Изобретение отноеитея к нриемо-передаю1цей телевизионной технике, может быть нримеиено, например, в передающем комнлекте устройства для передачи сигналов звукового сопровождения в полосе частот телевизиопиого канала.

Известны устройства епихроиизапии, содержа идие последовательно включенные строчный аилитудный селектор, временной селектор, схему импульсной автоматической подстройкн частоты и фазы, формирователь-распределнтель вспомогательных импульсов, а также к, дровый селектор и формирователь амплитудного сигнала синхронизации.

Цель изобретения - ускорение вхождения в синхронизм, новышепие номехозаии-иденпоетн сигнала строчной синхронизации нри уменьшении временного иитервала, отведсиного для передачи еинхроинформации, а также номехоустончивое и точное выделение кадрового синхроимпульса.

Предлагаемое устройство отличается тем, что на входе времепного селектора включена схема совпадения, на другой вход которой подается снгнал с выхода триггера; его DXOды подключены к выходу ехемы совпадения п формирователю-раснределителю вспомогательных импульсов, один из выходов которого через блокинг-генератор подключен к еумматору, ирнчем на второй его вход подается сигнал с формирователя амплитудного сигнала синхронизации.

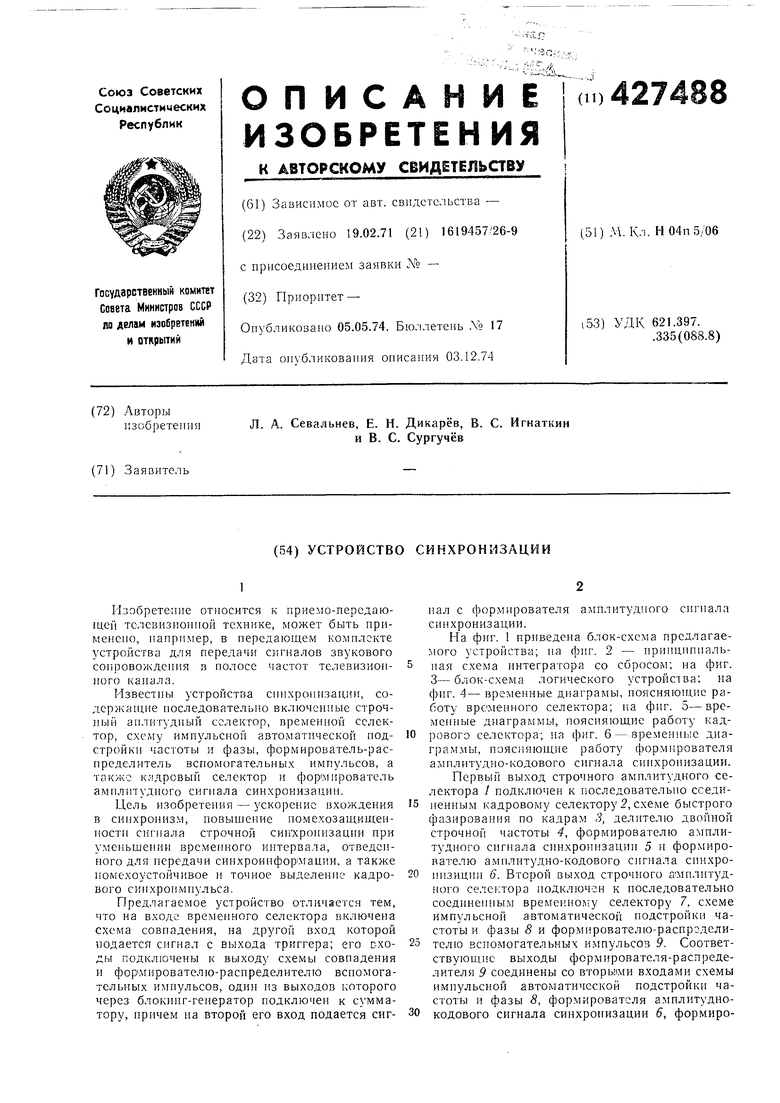

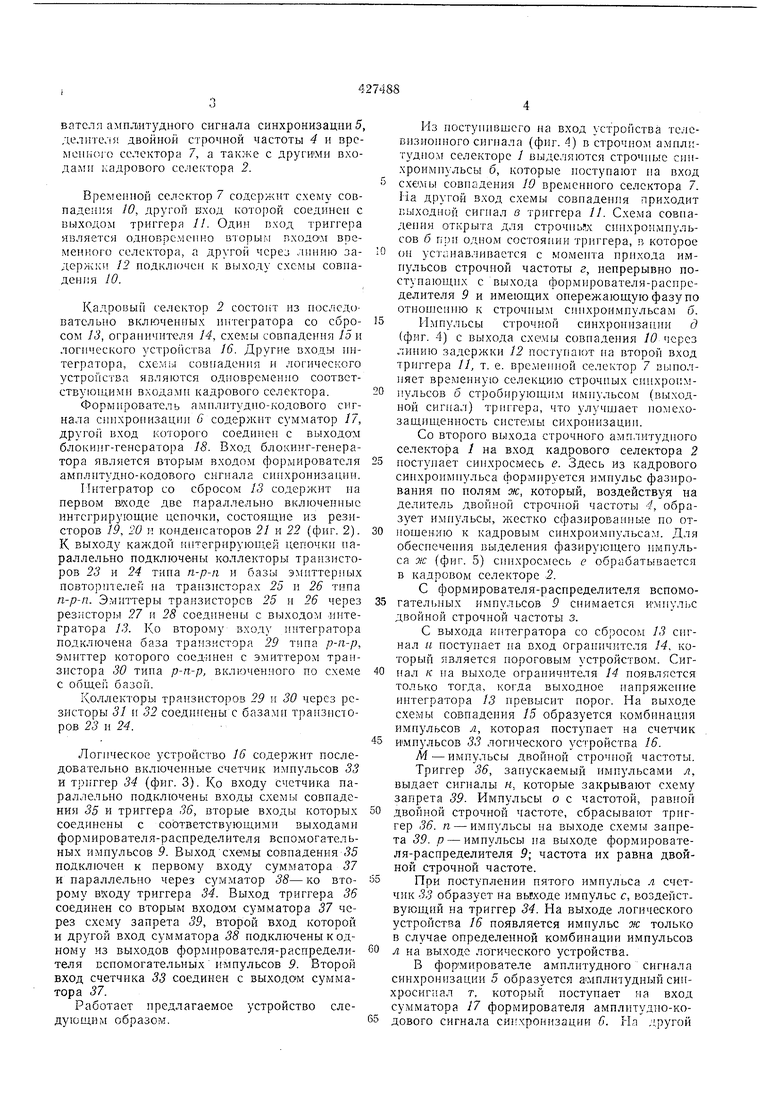

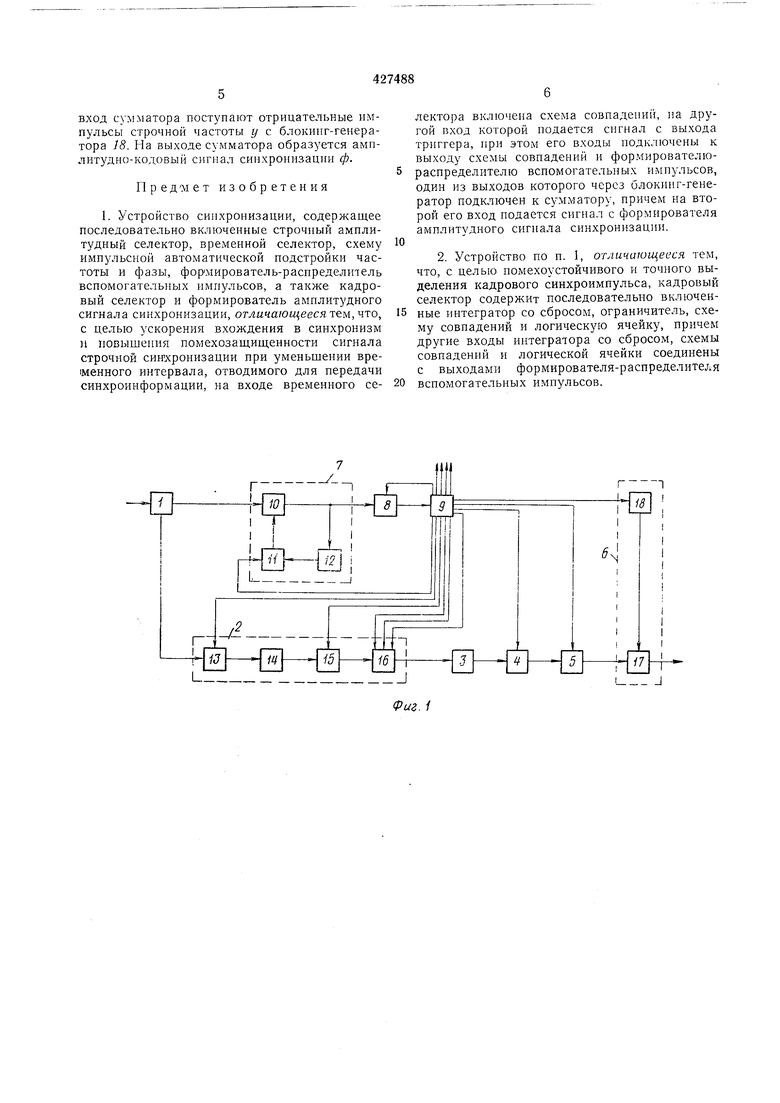

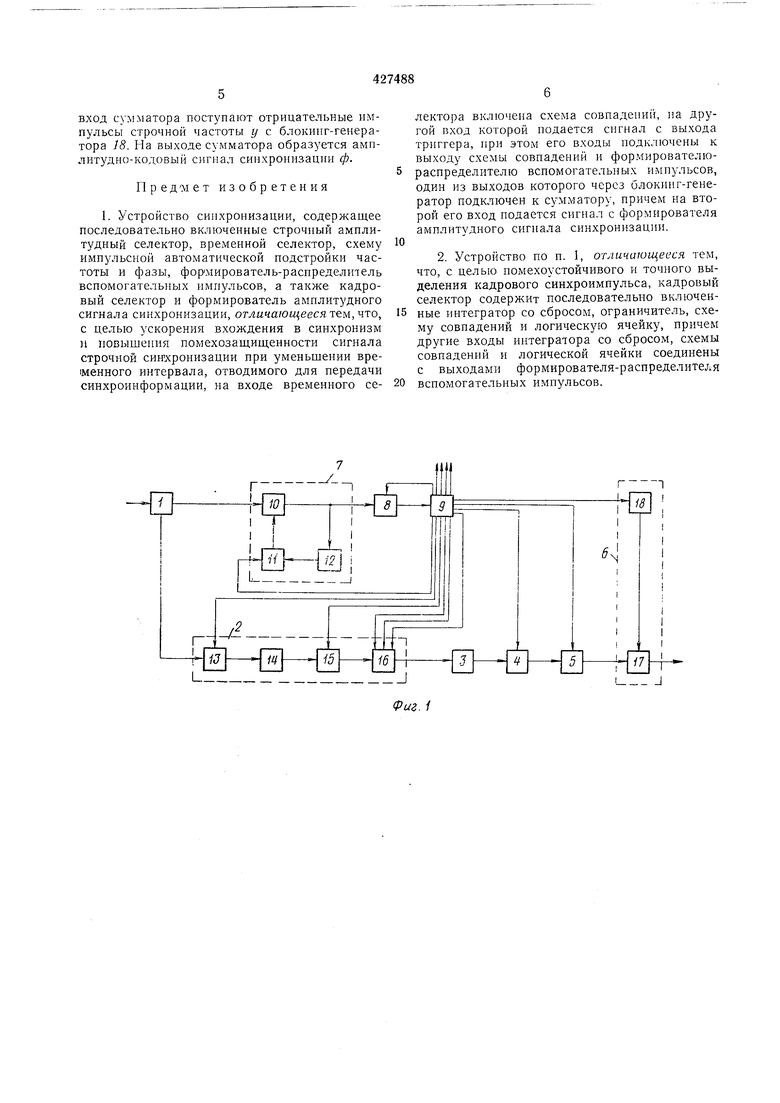

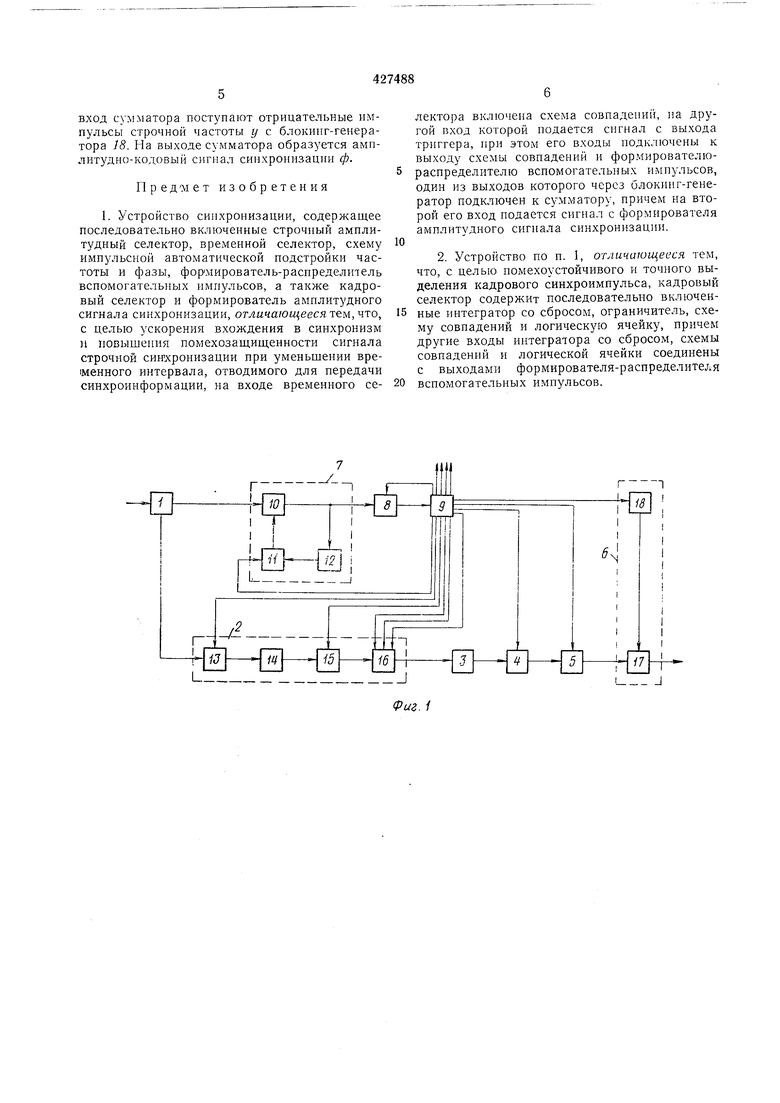

На фиг. 1 приведена блок-схема предлагаемого устройства; иа фиг. 2 - ,ипиальная схема ннтегратора со сбросом; па фиг. 3-блок-схема логического устройства; на фиг. 4- временные диаграмы, поясняюн ие работу врсменного селектора; па фнг. 5-вре.менные днаграммы, поясняющие работу кадрового селектора; на фиг. б - временные диаграммы, поясняющие работу формирователя амплитудно-кодового сигнала сиихроиизации.

Первый выход строчного амплитудного селектора / подключен к последовательно есединеиным кадровому селектору 2, ехеме быетрого фазирования по кадрам 3, делителю двойной строчной частоты 4, формирователю амплитудного еигнала синхронизации 5 и формирователю амплитудно-кодового сигнала сннхроппзиции 6. Второй выход строчного аздплитудiioro селектора нодкл10чен к последовательно соедниенным временному селектору 7, схеме импульсной автоматической подстройки частоты и фазы 5 и формнрователю-раепроделителю вспомогательных и.мнульсоз 9. Соответствующие выходы форм рователя-раепределителя 9 соединены со вторыми входами схемы импульсной автоматической подстройки частоты и фазы 8, формирователя амплитуднокодового еигнала синхронизации 6, формироватсля амплитудного сигнала синхронизации 5, делите.15 двойной строчной частоты 4 н врсмоинсяч) селектора 7, а также с другими входами кадрового селектора 2.

Временной селектор 7 содержит схему совпадения 10, другой вход которой соединен с выходом триггера 11. Один вход триггера является одновременно вторым г.ходом временного селектора, а другой через линию задерйски 12 подключен к выходу схемы совпадения 10.

Кадровый селектор 2 состоит из иоследовательио включенных интегратора со сбросом 13, ограничителя 14, схемы совпадения 15 логического устройства 16. Другие входы интегратора, cxeMLii совиадения и логического устройства являются одиоБремеи 10 соответствующими входами кадрового селектора.

Формирователь a илитyднo-кoдoвoгo сигнала синхронизацин 6 содержит сумматор 17, друго вход которого соединен с выходом блокииг-геиератора 18. Вход блокинг-генератора является вторым входом формирователя амплитудно-кодового сигнала синхронизаиии.

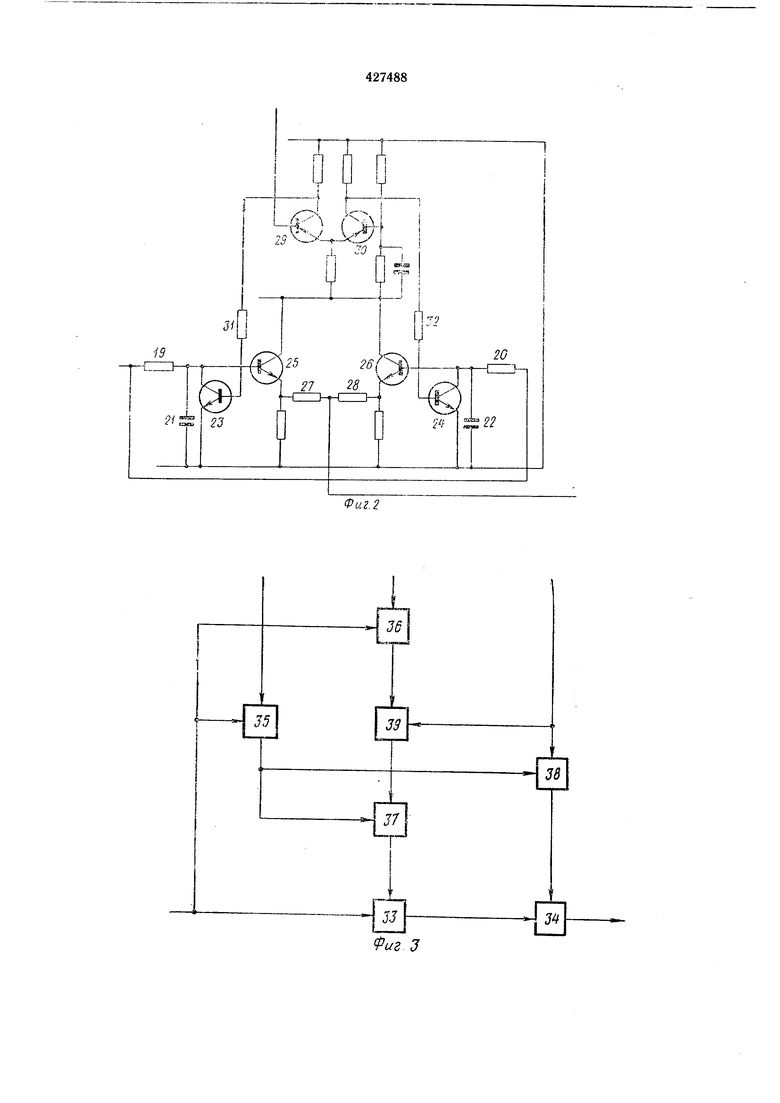

Интегратор со сбросом 13 содержит иа иервом выходе две паралле.лыю включенные интегрирующие цеиочки, состоящие из резисторов 19, 20 и коидеисаторов 21 и 22 (фиг. 2). К выходу каждой интегрирующей цепочки иараллельио подключеиы коллекторы транзисторов 23 и 24 тина п-р-п и базы эмиттерных повторителей иа траизисторах 25 и 26 тина п-р-п. Эми1теры тра1 зисторов 25 н 26 через резисторы 27 и 28 еоедииеиы с выходом иитегратора 13. Ко второму входу интегратора иодключена база транзистора 29 тииа р-п-р, эмиттер которого соедииен с эмиттером траизнстора 30 типа р-п-р, включенного но схеме с общей базой.

Коллекторы транзисторов 29 и 30 через резисторы 31 и 32 соединены с базами транзисторов 23 н 24.

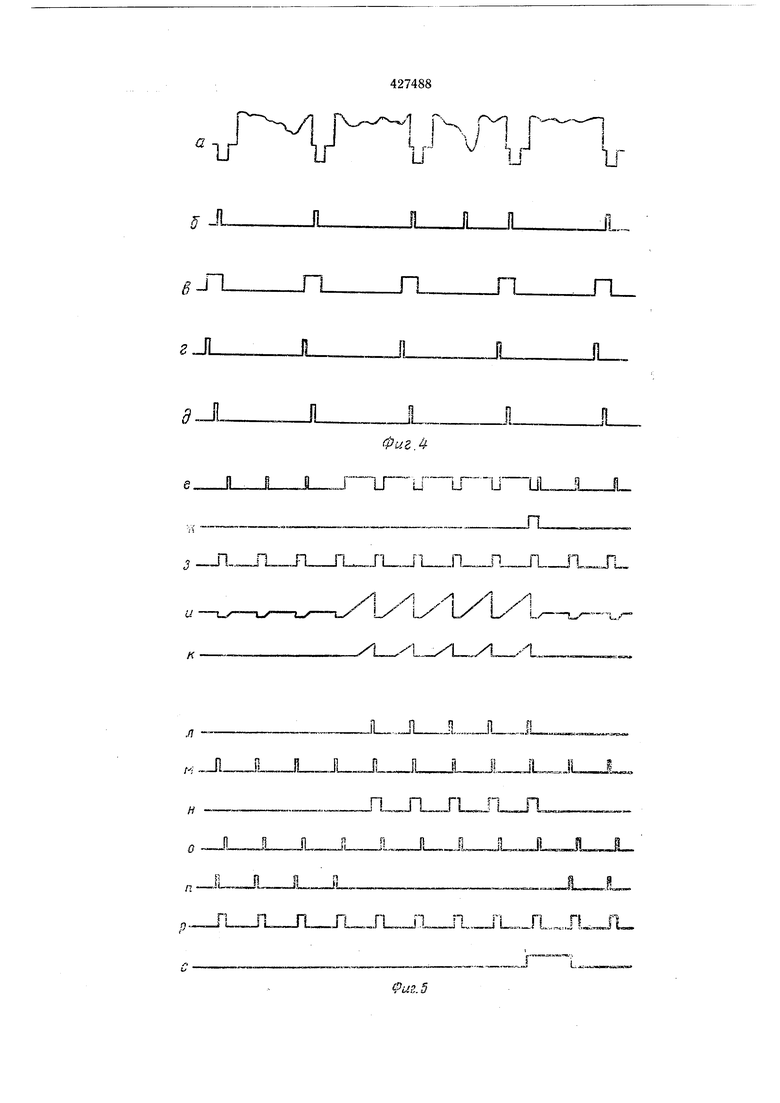

Логнческое устройство }6 содержит носледовательно включенные счетчик имиульсов 33 и триггер 34 {фиг. 3). Ко входу счетчика иараллельио нодключены входы схемы совпадения 35 и триггера 36, вторые входы которых соедииены с соответствующими выходами формирователя-распределителя вспомогательных имиульсов 9. Выход схемы совиадения 5 подключен к первому входу сумматора 37 и параллельно через сумматор 38-ко второму входу триггера 34. Выход триггера 36 соединен со вторым входом сумматора 37 через схему запрета 39, второй вход которой и другой вход сумматора 38 нодключены к одному из выходов формирователя-распределителя вспомогательных импульсов 9. Второй вход счетчика 33 соединен с выходам сумматора 37.

Работает иредлагаемое устройство следующим образом.

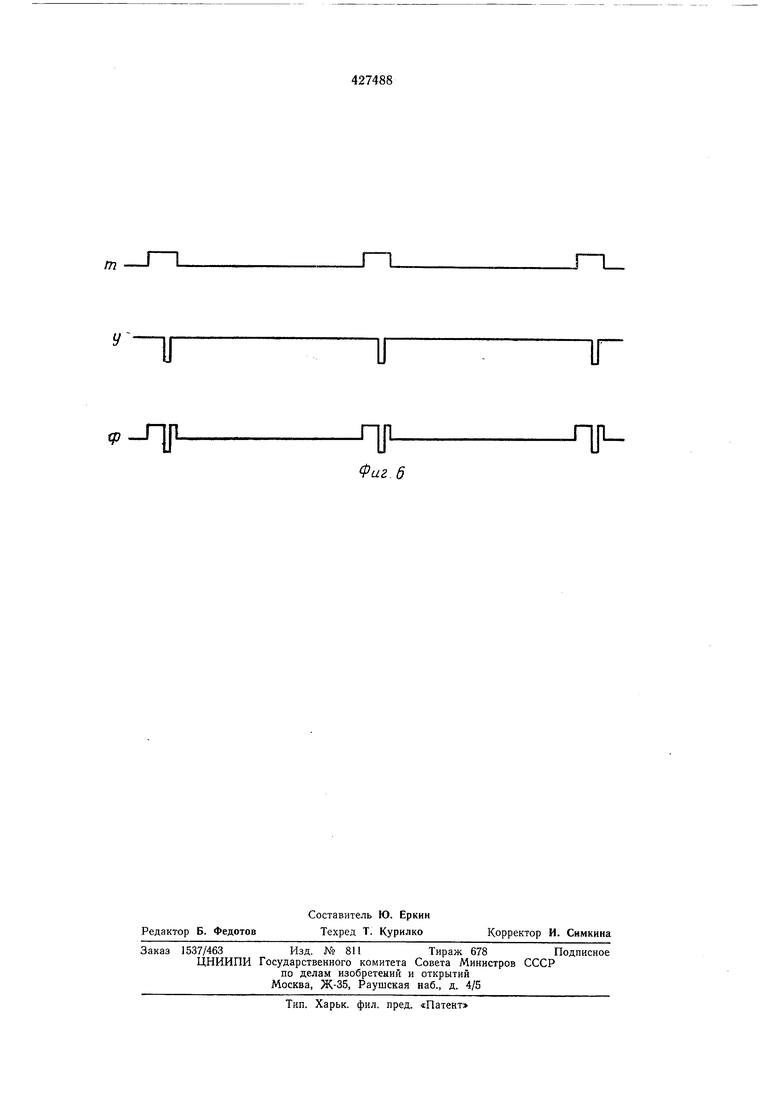

Из иостуии1зшсго на вход устройства телевизионного сигнала (фнг. 4) в строчном амплитудном селекторе 1 выделяются строчные сиихроимиульсы б, которые поступают иа вход cxeoib совиадения W временного селектора 7. На другой вход схемы совиадеиия приходит пыходной сигиал в триггера 11. Схема совиадеиия открыта для строчньк сиихроимиульсов б г;ри одном состоянии триггера, п которое

ои устг;навливается с момента нрнхода имиульсов строчной частоты г, непрерывно постуиающих с выхода формирователя-распределителя 9 и имеющих опережающую фазу по отиощеиню к строчным сннхроимнульсам б.

Имнульсы строчной синхронизаиии д (фиг. 4) с выхода схемы совиадеиия /О через лииию задержки 12 иостуиают иа второй вход триггера //, т. е. временной селектор 7 выполняет временную селекцию строчных синхроимнульсов б стробирующим импульсом (выходной сигиал) триггера, что улучщает иомехозащищенность системы сихроиизации.

Со второго выхода строчного амплитудного селектора / на вход кадрового селектора 2

поступает сиихросмесь е. Здесь из кадрового синхроийИ1ульса формируется импульс фазирования но иолям ж, который, воздействуя на делитель двойноГ строчиой частоты 4, образует имиульсы, жестко сфазированные но отнощению к кадровым синхроимпульсам. Для обесиечеиия выделеиия фазирующего имиульса УК (фиг. 5) синхросмесь е обрабатывается в кадровом селекторе 2.

С формирователя-распределителя вспомогательиых импульсов .9 сиимается И .)С двойной строчной частоты з.

С выхода интегратора со сбросом 13 сигнал и ностуиает иа вход ограничителя 14, который является пороговым устройством. Сигнал к иа выходе ограиичителя 14 появляется только тогда, когда выходное ианрял :ение иитегратора 13 иревысит порог. На выходе схемы совпадения /5 образуется комбинация импульсов л, которая поступает на счетчик

имиульсов 33 логического устройства 16.

М - имиульсы двойиой строчиой частоты.

Триггер 36, запускаемый импульсами л,

выдает сигналы н. которые закрывают схему

запрета 39. Импульсы о е частотой, равной

двойиой строчной частоте, сбрасывают триггер 36. п - имиульсы иа выходе схемы заирета 39. р - имиульсы на выходе формирователя-распределителя 9; частота их равна двойной строчной частоте.

При поступлении нятого импульса л счетчик 33 образует на вьлходе импульс с, воздействующий на триггер 34. На выходе логического устройства 16 появляется импульс ж только в случае определенной комбинации импульсов л на выходе логического устройства.

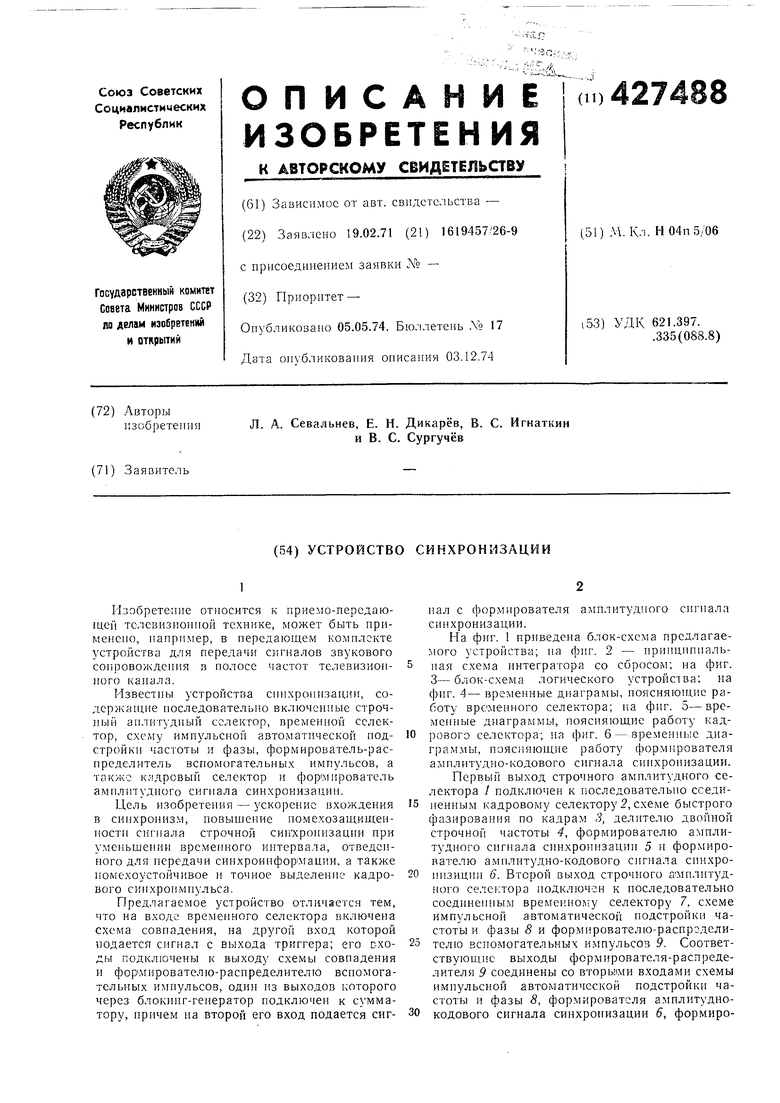

В формирователе амплитудного сигнала синхронизации 5 образуется амплитудный синхросигнал т, который поступает на вход сумматора 17 формирователя амплитудио-кодового сигнала синхронизации 6. На другой

вход сумматора поступают отрицательные импульсы строчной частоты у с блокипг-генератора 18. На выходе сумматора образуется амплитудно-кодовый сигнал синхронизации ф.

Предмет изобретения

1. Устройство синхронизации, содержащее последовательно включенные строчный амплитудный селектор, временной селектор, схему импульсной автоматической подстройки частоты и фазы, формирователь-распределитель вспомогательных импульсов, а также кадровый селектор и формирователь амплитудного сигнала синхронизации, отличающееся тем, что с целью ускорения вхождения в синхронизм 11 повышения помехозащищенности сигнала строчной синхронизации при уменьшении временного интервала, отводимого для передачи синхроинформации, на входе временного селектора включена схема совпадений, на другой вход которой подается сигнал с выхода триггера, при этом его входы подключены к выходу схемы совпадений и формирователюраспределителю вспомогательных импульсов, один из выходов которого через блокинг-генератор подключен к сумматору, причем на второй его вход подается сигнал с q)0pмиpoвaтeля амплитудного сигнала синхронизац И.

2. Устройство по п. 1, отличающееся тем, что, с целью помехоустойчивого и точного выделения кадрового синхроимпульса, кадровый селектор содержит последовательно включенные интегратор со сбросом, ограничитель, схему совпадений и логическую ячейку, причем другие входы интегратора со сбросом, схемы совпадений и логической ячейки соединены с выходами формирователя-распределителя

вспомогательных импульсов.

I

L4 /SN 4

.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ И КОНТРОЛЯ КАЧЕСТВЕННЫХ НОКАЗАТЕЛЕЙ ТЕЛЕВИЗИОННОГО ТРАКТА | 1971 |

|

SU293309A1 |

| Устройство цветовой синхронизации телевизионного приемника системы "СЕКАМ | 1980 |

|

SU985975A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФАЗЬ[ С ДИСКРЕТНЫМ | 1971 |

|

SU294264A1 |

| Устройство для передачи и приема сиг-НАлОВ СиНХРОНизАции,КОМАНд и СлужЕбНОйСВязи B РЕпОРТАжНОй KAMEPE цВЕТНОгОТЕлЕВидЕНия | 1975 |

|

SU845297A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1973 |

|

SU409149A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство для проведения телеигр | 1981 |

|

SU961731A1 |

| УСТРОЙСТВО для ЗАПИСИ и СЧИТЫВАНИЯ ПОСЛЕДОВАТЕЛЬНЫХ КОДОВ | 1970 |

|

SU274500A1 |

| Устройство синхронизации видеомагнитофона | 1981 |

|

SU965015A1 |

35

33

ЗГ

Г

3 и -ПРПР

Фиг. 6 Г ПР

Авторы

Даты

1974-05-05—Публикация

1971-02-19—Подача