Предлагаемое устройство относится к области вычислительной техники и приборостроения и может быть использовано при разработке дискретных вычислительных устройств и других приборов, предназначенных для решения статистических задач, в частности, в устройствах для вычисления математического ожидания, дисперсии, нормированного коэффициента корреляции и других характеристик случайных процессов.

Известные делители частоты, построенные на счетчиках, триггерах и логических схемах, обладая повышенным быстродействием, осуществляют деление входной частоты на один вполне определенный коэффициент.

Предлагаемое устройство позволяет осуществлять деление на переменный целочисленный коэффициент, что расширяет его логические возможности.

Это достигается тем, что в нем вход вычитания и вход сложения соответственно первого и второго реверсивных счетчиков через одну из схем совпадения соединен с единичным выходом триггера, нулевой выход которого подключен на вход второй схемы совпадения, связанной через схему сборки и непосредственно со входами сложения и вычитания соответственно первого и второго реверсивных счетчиков. Входы последних подключены соответственно к единичному и нулевому входам триггера, а также ко второй схеме сборки; выход схемы сборки является выходом делителя частоты, причем управление делителем осуществляется через триггер и схему совпадения, соединенную с входной шиной.

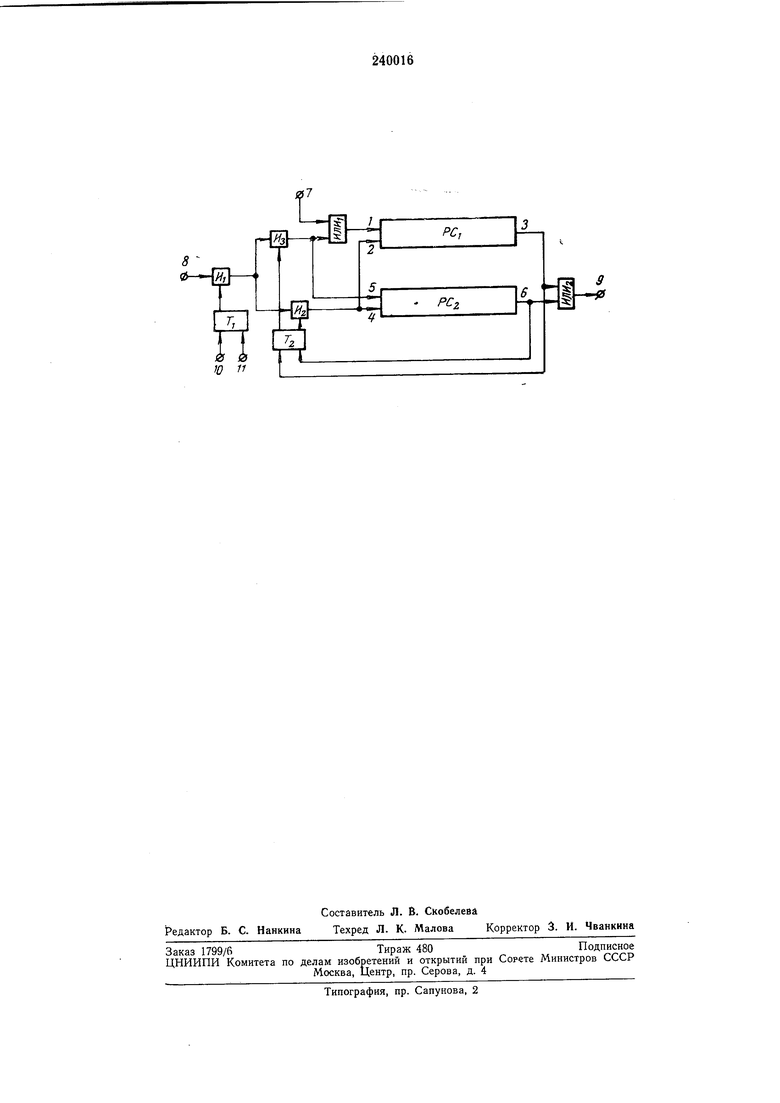

На чертеже представлена функциональная схема делителя частоты.

Делитель состоит из двух N-разрядных двоичных реверсивных счетчиков PC и РС, двух

триггеров Г и Г2, трех логических схем совпадения HI, И2, Иъ и двух логических схем сборки ИЛИ1 и ИЛИ2.

Вначале все разряды реверсивных счетчиков PCi и PCz устанавливаются в положение

единицы, а триггеры Г) и Га - в положение нуля. Каждый из реверсивных счетчиков имеет два входа и один выход. Вход / реверсивного счетчика PCi является входом сложениг., вход 2 - входом вычитания, выход 3 - мииусовым выходом. Вход 4 реверсивного счетчика PCz является входом сложения, вход 5 - входом вычитания, выход 6 - минусовым выходом. Левые входы триггеров Г и Гг - единичные, правые входы - нулевые, левые выходы - нулевые, а правые выходы - единичные. даются входные импульсы, подлежащ 1е делению, выходом делителя является выход 9 схемы сборки //Л//2, иа единичны вход 10 триггера 7 подается командный нмнульс на разрешение деления, а на нулевой вход // - командный импульс иа занрет деления. Делитель работает следующим образом. Все разряды реверсивных счетчиков PCi и PCz устанавливаются в положение единицы, а триггеры Т и Т2 - в ноложенне нуля. Па вход 7 схемы сборкн ИЛИ посылается число имиульсов, соответствующее требуемому коэффициенту деления. С выхода схемы сборки ИЛИ1 импульсы поступают на вход сложения / реверсивного счетчнка РС. Первый импульс, ностунивщнй на вход сложения / уетанавливает реверсивный счетчик PCi в нуль, При этом триггер Т не изменнт своего ноложения, так как нри установке в нуль реверсивного счетчика PCi на минусовом выходе импульс не появляется. После носылкн на вход 7 схемы сборки ИЛИ1 числа имиульсов, соответствующего требуемому коэффициенту деления, в реверсивном счетчике РС зафиксируется прямой код числа, на единицу меньщий требуемого коэффициента деления, а в реверсивном счетчике РС будет зафиксирована минус единнца в дополнительном коде. После установки коэффициента деления иа единичный вход 10 триггера TI подается командный нмнульс на разрешение деления, схема совпадения И откроется, и так как открыта схема совпадения 2, входные импульсы, поступающие на импульсный вход схемы совиадения //i, через схемы совпадения MI, Мч поступают на вход вычитання 2 реверсивного счетчика PC), и на вход сложения 4 реверсивного счетчика РС-. Первый импульс произведет установку )уля реверсивного счетчика РСч, а в реверенвном счетчике ЯС, ироизведет первое вычитание. После того как на вход 8 делителя поступнт число импульсов, соответствующее установленному коэффициенту деления, в реверсивном счетчнке РС все разряды уетановятся в полол енне единицы, на минусовом выходе 3 иоявится импульс, который установит триггер Т2 в положение единицы и, нройдя через ехему сборки ИЛИ-2, иостунит на выход 9 делителя. При этом в реверсивном счетчике РС фнкеируется число, на единицу меиьщее установленного коэффициента деления. После установки триггера Т. в положение единицы на входе схемы совиадения //3 создается управляющее напряжение, схема //3 открывается, а cxeiMa совпадения Я2 закрывается, Тенерь входные импульеы будут нроходнть через схемы совпадения //J и //3 и поступать иа вход вычитания 5 реверсивного счетчика РС, а через схему сборки ИЛИ - на вход сложения 1 реверсивногб счетчика РС. Процесс деления повторится, но будет происходить в реверенвном счетчике PCi, а в реверсивном счетчике PCi будет происходить подготовка к следующему циклу деления. На выход 9 делителя через схему сборки //////2 иоступит последовательность импульсов, сдвинутых относнтельно друг друга но фазе, еоответствующей установленному коэфф1щиенту деления. Описанный выше ироцесс деления входной частоты будет нроисходить до тех пор, пока на нулевой вход // триггера Г НС иоступит командный импульс на запрет деления. Перед тем как нроизводить деление входной частоты на коэффициент, отличный от предыдущего, необходимо установить устройство в исходное состояние, для чего все разряды обонх счетчиков устанавливаются в положение единицы, а зате.м на вход 7 схемы сборкн носылается число имнульсов, соответствующее новому коэффициенту деления, нри этом триггеры TI и Гг должны находиться в положении нуля. Установку коэффициента деления можно производить ц параллельной переписью двоичного числа в соответствующие разряды реверсивного счетчика РС по входам сложения, однако нереписываемое число должно быть .меньше требуемого коэффициента деления иа единицу. В данном елучае в исходном положении реверсивный счетчик РС должен быть установлен в нуль, а все разряды реверснвного счетчика РС2 - в положение единицы. Предмет изобретения Делитель частоты, содержащий реверсивные счетчики, триггеры, схемы совпадения и схемы сборки, отличающийся тем, что, с целью расширения логических возможностей и повышения быстродействия, в нем вход вычитания и вход сложения соответственно первого и второго реверсивных счетчиков через одну из схем совпадения соединен с единичным выходом триггера, нулевой выход которого подключен на вход второй схемы совпадення, связанной через схему сборки и непосредственно со входами сложения и вычитания соответственно первого и второго реверсивных счетчиков, выходы которых подключены соответственно к единичному и нулевому входам триггера, а также ко второй схеме сборки, выход указанной схемы является выходо.м делителя частоты, причем управление делителем осуществляется через триггер и схему совиадения, соединенную с входной щиной.

w;a

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР СЛУЧАЙНЫХ ПРОЦЕССОВВПТБ4чп2л^ iiiJijiiEaf | 1972 |

|

SU439064A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1972 |

|

SU426318A1 |

| УСТРОЙСТВО для УСРЕДНЕНИЯ ЧАСТОТЫ | 1972 |

|

SU328431A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Адаптивный аналого-цифровой преобразователь частотно-модулированных сигналов | 1972 |

|

SU443479A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| Преобразователь частотно-импульсных сигналов в цифровой код | 1972 |

|

SU445148A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для контроля реверсивного счетчика | 1973 |

|

SU444186A1 |

Даты

1969-01-01—Публикация