Известены динамические логические элементы, в которых при многофазной системе импульсного питания задержка входного сигнала осущест вляется при помощи запоминающего .конденсатора, при однофазной системе имлульсного литания - при помощи элемента задержки или колебательного Контура.

Наличие реактивностей затрудняет изготовление этих элементов средствами современной микроэлектроники и приводит к ограничению рабочей частоты или длительности выходного импульса как сверху, так и снизу. Использование многофазной системы импульсного питания сложно для генерирования этих колебаний, и, кроме того, затрудняет построение устройств, особенно при использовании печатного монтажа.

Предлолсенный динамический элемент отличается тем, что выход входной диодной схемы «И-ИЛИ соединен с коллектором коммутирующего транзистора и через диод - с базой первого транзистора управляемого одновибратора, коллектор которого подключен через резистор к шине питания. Коллектор второго транзистора подключен ко входу синхронизирующих импульсов и -через резистор - к базе переключающего транзистора, коллектор которого соединен с базой одного из транзисторов выходного триггера и через диод и резистор - со входом синхронизирующих импульсов, к которому через резистор также подключена база коммутирующего транзистора.

Это позволяет увеличить диапазон частот и осуществить задержку без применения реактивных элементов.

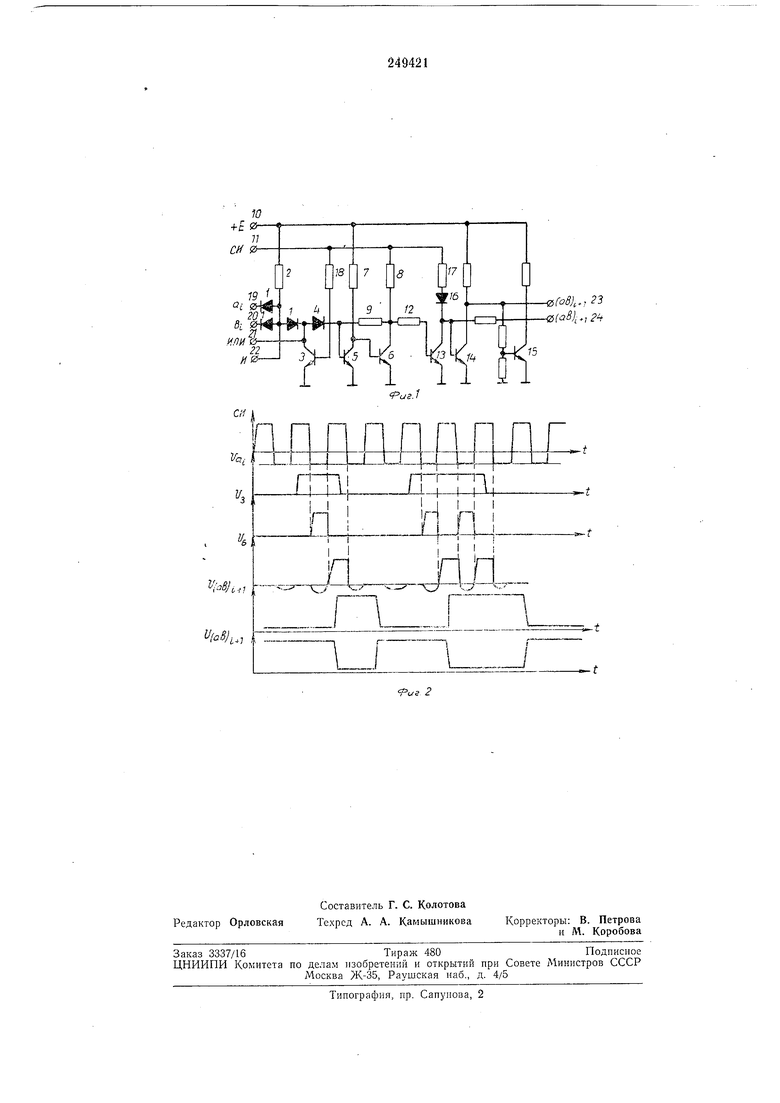

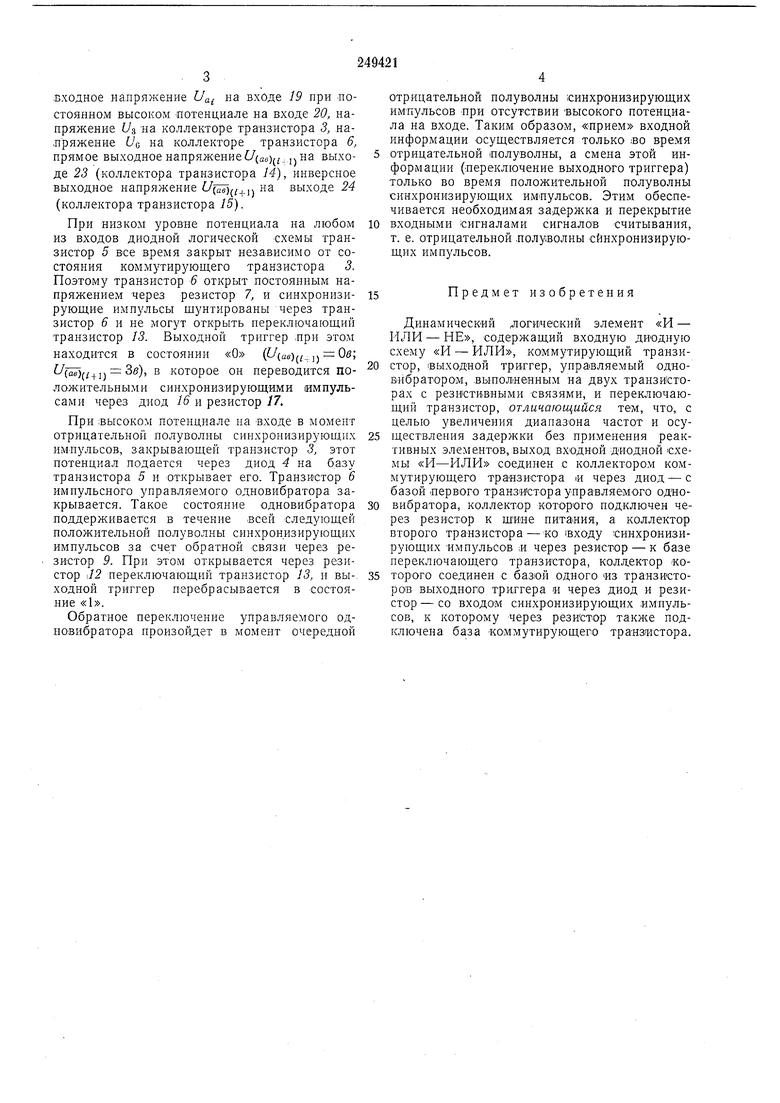

На фиг. 1 приведена схема предложенного динамического элемента; па фиг. 2 - временная диаграмма его работы.

Предложенный динамический элемент состоит из ВХОДНОЙ диодной схемы «И-ИЛИ на диодах / и резисторе 2, выход которой соединен с коллектором коммутирующего транзистора 5 управляемого одновибратора на транзисторах 5 и 6 и резисторах 7, 8 и 9. Коллекторы транзисторов 5 и б подключены к шине питания 10 ( + Е) и ко входу П синхронизирующих импульсов. Коллектор транзистора б

через резистор /2 соединен с базой переключающего транзистора 13, коллектор которого соединен с базой транзистора /4 выходного триггера на транзисторах )4 и 5 и через диод М и резистор 77-со входом 11 синхронизирующих импульсов, к которому через резистор 18 также подключена база коммутирующего транзистора 3. Логический элемент имеет входы 19-22 и выходы 23, 24.

входное напряжение Uai на входе 19 при постоянном высоком Потенциале на входе 20, напряжение L/3 на коллекторе транзистора 3, напряжение бо на коллекторе транзистора 6, прямое выходное напряжение 6( на выходе 23 (коллектора транзистора 14), инверсное выходное напряжение (/i+i) на выходе 24 (коллектора транзистора 15).

При низком уровне потенциала на любом из входов диодной логической схемы транзистор 5 все время закрыт независимо от состояния коммутирующего транзистора 3. Поэтому транзистор 6 открыт постоянным напряжением через резистор 7, и синхронизирующие импульсы шунтированы через транзистор 6 и не могут открыть переключающий транзистор 13. Выходной триггер лри этом находится в состоянии «О (6(ав)„ j - Об; ((/+1) - ) которое он переводится положительными синхронизирующими импульсами через диод 16 и резистор 17,

При высоком потенциале на входе в момент отрицательной полуволны синхронизирующих импульсов, закрывающей транзистор 3, этот потенциал подается через диод 4 на базу транзистора 5 и открывает его. Транзистор 6 импульсного управляемого одновибратора закрывается. Такое состояние одновибратора поддерживается в течение всей следующей положительной полуволны синхронизирующих импульсов за счет обратной связи через резистор 9. При этом открывается через резистор 12 переключающий транзистор 13, и выходной триггер перебрасывается в состояние «1.

Обратное переключение управляемого одновибратора произойдет в момент очередной

отрицательной полуволны синхронизирующих импульсов при отсутствии ВЫСОКОГО потенциала на входе. Таким образом, «прием входной информации осуществляется только :во время

отрицательной полуволны, а смена этой информации (переключение выходного триггера) только во время положительной полуволны синхронизирующих им1пульсов. Этим обеспечивается необходимая задержка и перекрытие

входными сигналами сигналов считывания, т. е. отрицательной полуволны синхронизирующих импульсов.

Предмет изобретения

Динамический логический элемент «И - 11ЛИ - НЕ, содержащий входную диодную схему «И - ИЛИ, коммутирующий транзистор, выходной триггер, управляемый одновибратором, .выполненным на двух транзисторах с резистивными связями, и переключающий транзистор, отличающийся тем, что, с целью увеличения диапазона частот и осуществления задержки без применения реактивных элементов, выход входной диодной схемы «И-ИЛИ соединен с коллектором коммутирующего траязистора и через диод - с базой .первого транзистора управляемого одновибратора, коллектор которого подключен через резистор к шине питания, а коллектор второго транзистора- ко входу синхронизирующих пмпульсов :и через резистор - к базе переключающего транзистора, колл.ектор «оторого соединен с базой одного из транзисторов выходного триггера и через диод и резистор - со входом син.хронизирующих имнульсов, к которому через резистор также подключена база коммутирующего транзистора.

19

П П П П П П П Г +ШН:Ь1±Н:± Щ-

СИ

еСо8),., 23 e(aSl,,2

--i

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU298072A1 |

| Импульсный стабилизатор постоянного напряжения | 1984 |

|

SU1182499A1 |

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| Устройство контроля импульсных сигналов | 1981 |

|

SU1003323A1 |

| ЛОГИЧЕСКИЙ ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ «НЕ—ИЛИ» НА ТРАНЗИСТОРАХ | 1968 |

|

SU218528A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1972 |

|

SU329673A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1457056A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

Даты

1969-01-01—Публикация