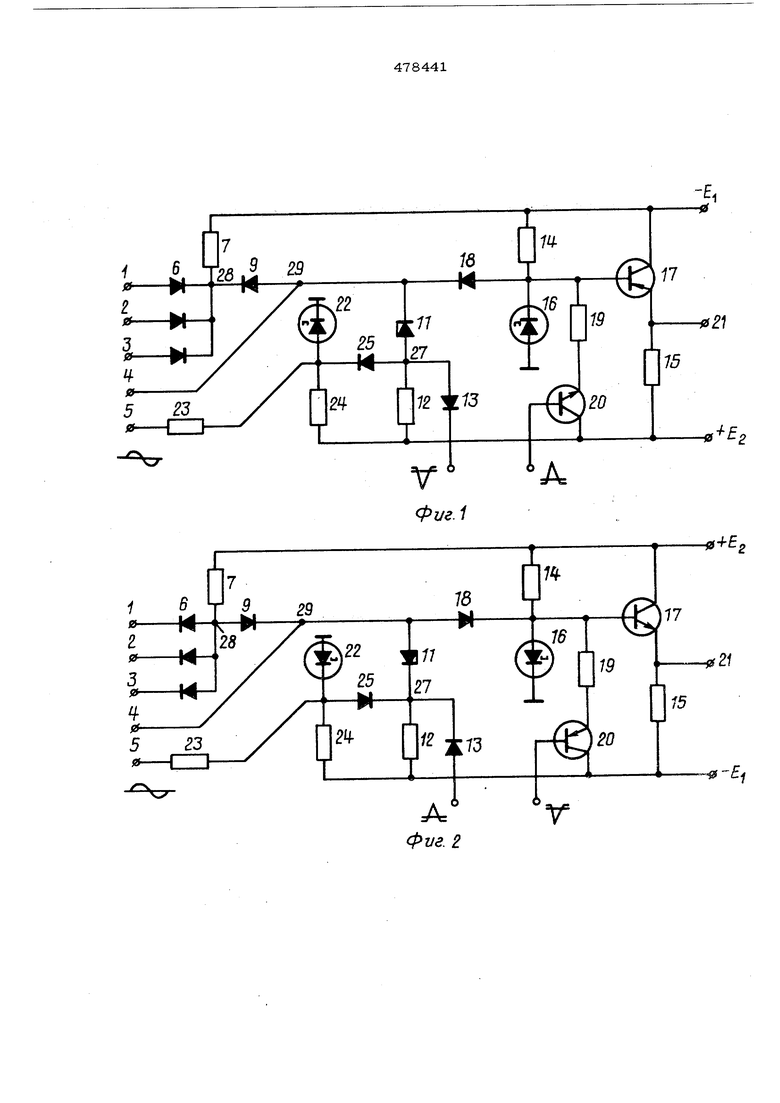

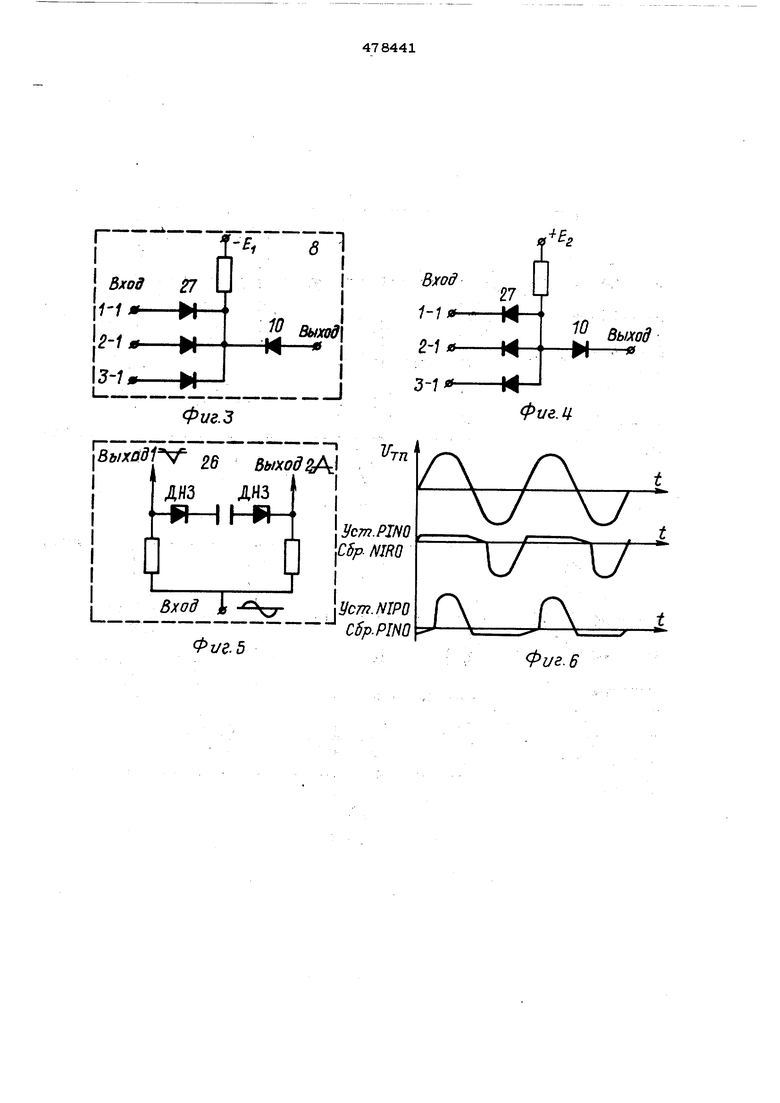

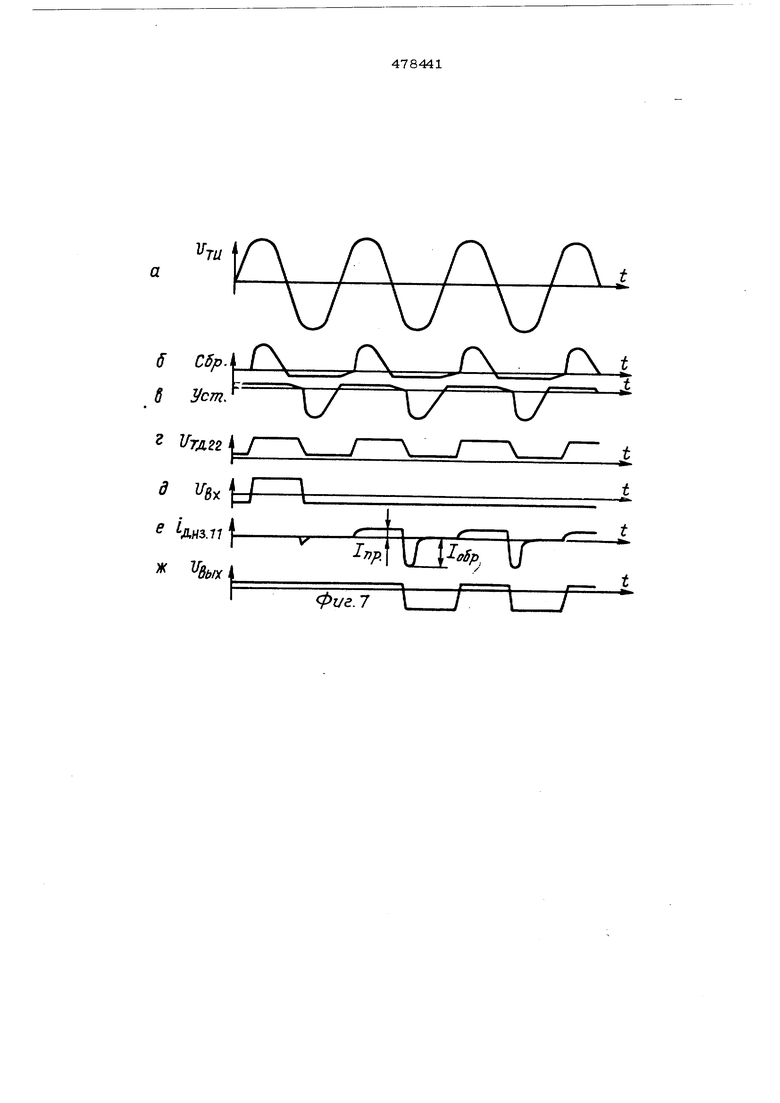

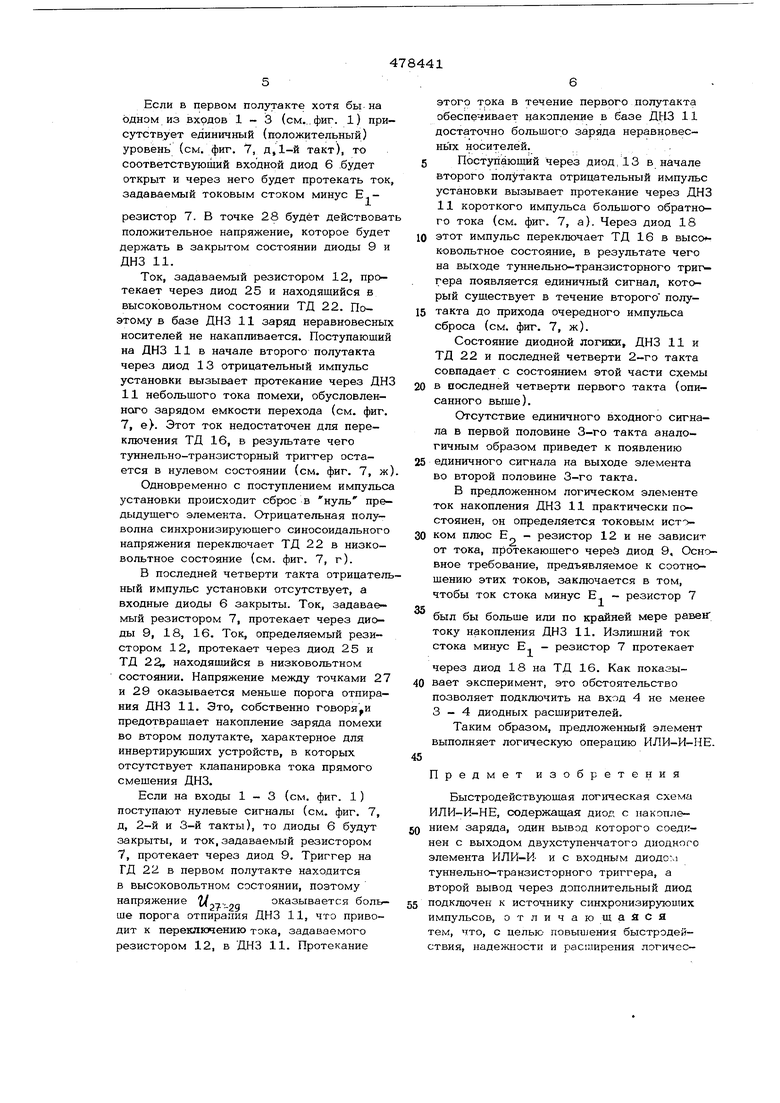

(54) БЫСТРОДЕЙСТВУЮЩАЯ ЛОГИЧЕСКАЯ СХЕМА ИЛИ-И-НЕ фиг. 7 - временная диаграмма работы элемента ИЛИ-И-НЕ PINO Один формирователь импульсов обеспе чивает работу двух элементов - одного элемента и одного N1PO - и позволяет осуществлять синхронизацию работы схем одним источником синусоидального напряжения. Элемент ИЛИ-И-НВ PINQ содержит (см, фиг. 1) входы 1, 2, 3, 4, 5, элемента PINO. входные диоды 6, резис тор 7 и источник напряжения Е.. Ком ненты 1-7 вместе с источником напрян Е образуют элемент сборки едиженияничных сигналов. При подключении на вх 4 двухступенчатого диодного элемента ИЛИ-И 8, (см. фиг. 3), диод 9 элемен та PINO и диод 10 элемента 8 составл ют элемент совпадения для единичных (положительных) сигналов. Диод с накоплением заряда 11, резис тор 12 (см. фиг. 1 и 2), обеспечивающи совместно с источником напряжения +Е„ ток прямого смешения на ДНЗ 11, и дио 13, через который подаются отрицательные импульсы установки, образуют диодный усилитель тока. Резисторы 14, 15, туннельный- диод (ТД) 16 и транзистор- 17 составляют бистабильный триггер логического элемента. Диод 18 является входным диодом туннельно-транзисторного триггера, а резистор 19 и транзистор 20 обеспе- чивавэт сброс этого триггера в нуль . Выход 21 туннельно-транзисторного триг гера является выходом логического элемента. Бистабильный триггер на ТД 22, резисторах 23, 24 и диоде 25 предназначе для предотвращения накопления заряда в базе ДНЗ 11 в полутакте сброса в нуль управляющего (предыдущего) элемента. Элемент ИЛИ-И-НЕ PINO работает следующим образом. Входные сигналы элементов N1PO (см. фиг. 2) поступают на входы 1-3 элемента PINO (см. фиг. 1) и принимаю два уровня: нулевой минус 0,3 В и единичный плюс 0,6 В. Сигналы с выхода 2 элемента PINO поступают на входы 1 - 3 элемента |Ч1РО и принимают два уровн нулевой плюс 0,3 В и единичный минус 0,6 В. На фиг. 7, Q, показано синхронизирующее синусоидальное напряжение, поступаю шее на вход 5 элемента PINO и вход формирователя 26 на ДНЗ (м. фиг. 5). На фиг. 7, б, в, показаны сформированные из этого напряжения импульсы установки и сброса. На фиг. 7, г показаны клапанирующие импульсы, сформированные на ТД 22. На фиг. 7 д, е, ж приведены диаграммы входного сигнала, тока ДНЗ 11 и выходного сигнала соответственно. Особенность работы триггера на ТД 22, обеспечивающего предотвращение накопления заряда помехи в базе ДНЗ 11 путем клапанировки тока прямого смещения ДНЗ 11, заключается в следующем. Управление переключением этого триггера осуществляется через резистор 23 синусоидальным напряжением синхронизации, поступающим на вход 5. Положительная полуволна переключает триггер на ТД 22 в высоковольтное состояние, а отрицательная полуволна - в низковольтное. Длительность сформированных на ТД 22 импульсов (см. фиг. 7, г) равна половине такта и практически совпадает по времени с приходом- входного сигнала. Таким образом, ток прямого смещения, задаваемый резистором 12, может протекать через ДНЗ 11 только в полутакте поступления входных сигналов. При этом единичные входные сигналы не разрещают протекание тока через ДНЗ 11, а нулевые - разрешают. В начале каждого такта на базу транзистора 20 поступает положительный и} пульс сброса. Эмиттерный ток этого транзистора через резистор 19 .устанавливает ТД 16 в низковольтное (нулевое) состоял ние. Из фиг. 7 а, г. видно, что с приходом положительной полуволны синхронизирующей синусоиды (по достижении примерно 3/4 амплитуды) триггер на ТД 22 переключается в высоковольтное состояние, что приводит к повыщению положительного напряжения в точке 27. Это является необходимым, но недостаточным условием отпирания ДНЗ 11 и переключения в него тока, определяемого токовым истоком +Е: резистор 12. Для отпирания ДНЗ 11, а следовательно и диода 9, необходимо, чтобы разность потенциалов в точках 27 и 28 превыщала суммарный порог отпирания диодов 9 и 11. А это возможно при достаточно большом отрицательном потенциале в точке 28 (не менее - 0,6 В) при высоковольтном состоянии ТД 22.

Если в первом полутакте хотя бы- на одном из входов 1-3 (см...фиг. 1) присутствует единичный (положительный) уровень (см. фиг. 7, д,1-й такт), то соответствующий входной диод 6 будет открыт и через него будет протекать ток задаваемый токовым стоком минус Е резистор 7. В точке 28 будет действоват положительное напряжение, которое будет держать в закрытом состоянии диоды 9 и ДНЗ 11.

Ток, задаваемый резистором 12, протекает через диод 25 и находящийся в высоковольтном состоянии ТД 22. Поэтому в базе ДНЗ 11 заряд неравновесных носителей не накапливается. Поступающий на ДНЗ 11 в начале второго полутакта через диод 13 отрицательный импульс установки вызывает протекание через ДН 11 небольщого тока помехи, обусловленного зарядом емкости перехода (см. фиг. 7, е). Этот ток недостаточен для переключения ТД 16, в результате чего туннельно-транзисторный триггер остается в нулевом состоянии (см. фиг. 7, ж

Одновременно с поступлением импульса установки происходит сбрюс в нуль предыдущего элемента. Отрицательная полуволна синхронизирующего синосоидального напряжения переключает ТД 22 в низковольтное состояние (см. фиг. 7, г).

В последней четверти такта отрицательный импульс установки отсутствует, а входные диоды 6 закрыты. Ток, задаваемый резистором 7, протекает через диоды 9, 18, 16. Ток, определяемый резистором 12, протекает через диод 25 к ТД 2 Я находящийся в низковольтном состоянии. Напряжение между точками 27 и 29 оказывается меньше порога отпирания ДНЗ 11. Это, собственно говоря и предотвращает накопление заряда помехи во втором полутакте, характерное для инвертирующих устройств, в которых отсутствует клапанировка тока прямого смещения ДНЗ.

Если на входы 1 - 3 (см. фиг. 1) поступают нулевые сигналы (см. фиг. 7, д, 2-й и 3-й такты), то диоды 6 будут закрыты, и ток, задаваемый резистором 7, протекает через диод 9. Триггер на ГД 22 в первом полутакте находится в высоковольтном состоянии, поэтому напряжение t/лт;- од оказывается больше порога отпирания ДНЗ 11, что приводит к переключению тока, задаваемого резистором 12, в ДНЗ 11. Протекание

этого тока в течение первого полутакта обеспечивает накопление в базе ДЬ13 11 достаточно большого заряда неравнрвесных носителей.

5 Поступающий через диод, 13 в начале второго полутакта отрицательный импульс установки вызывает протекание через ДНЗ 11 короткого импульса большого обратного тока (см. фиг. 7, а). Через диод 18

10 этот импульс переключает ТД 16 в высо ковольтное состояние, в результате чего на выходе туннельно-транзисторного триггера появляется единичный сигнал, который существует в течение второго полу5 такта до прихода очередного импульса сброса (см. фиг. 7, ж).

Состояние диодной логики, ДНЗ 11 и ТД 22 и последней четверти 2-го такта совпадает с состоянием этой части схемы

0 в последней четверти первого такта (описанного выще).

Отсутствие единичного входного сигнала в первой половине 3-го такта аналогичным образом приведет к появлению

5 единичного сигнала на выходе элемента во второй половине 3-го такта.

В предложенном логическом элементе ток накопления ДНЗ 11 практически постоянен, он определяется токовым истт0 ком плюс Е - резистор 12 и не зависит от тока, протекающего черей диод 9, Основное требование, предъявляемое к соотношению этих токов, заключается в том, чтобы ток стока минус Е - резистор 7

5

был бы больше или по крайней мере равен

току накопления ДНЗ 11. Излишний ток стока минус Е - резистор 7 протекает

через диод 18 на ТД 16. Как покааы0 вает эксперимент, это обстоятельство

позволяет подключить на вход 4 не менее

3-4 диодных расширителей.

Таким образом, предложенный элемент

выполняет логическую операцию ИЛИ-И-НЕ. 5

Предмет изобретения

Быстродействующая логическая схема ИЛИ-И-НЕ, содержащая диод с пакоплеQ нием заряда, один вывод которого соединен с выходом двухступенчатого диодного элемента ИЛИ-И- и с входным диодом туннельно-транзисторного триггера, а второй вывод через дополнительный диод

подключен к источнику синхронизирующих импульсов, отличающаяся тем, что, с целью- повышения быстродействия, надежности и расллирения логичес78

ких возможностей, в эпекгент ИЛИ-И-НЕнапряжения и через разделительный диод

введен бистабильный триггер на туннель-подсоединена к второму выводу диода

ном диоде, общая точка вход - выходс накоплением заряда, подключенному

которого через резистор подключена кчерез токозадаюший резистор к шине

источнику управляющего синусоидального5 источника питания.

478441

Фг/г.д

Фиг. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| ОЗНАЯ ПАТЕНТШ-г^АН^Г'Е^ИАЯ | 1971 |

|

SU304700A1 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| Логический элемент | 1974 |

|

SU572930A2 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| ВСЕСОЮЗНАЯ ПАТГ..,.Ч?СКАЙбиблиотека wsBAВ. Е. Мельник | 1972 |

|

SU336812A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| Управляемый триггер | 1974 |

|

SU541290A1 |

| Однотактный регистр сдвига | 1972 |

|

SU447761A1 |

| Формирователь импульсов | 1980 |

|

SU921065A1 |

| Вторичный источник питания | 1989 |

|

SU1686655A1 |

Авторы

Даты

1975-07-25—Публикация

1973-03-05—Подача