Известны логические динамические элементы «НЕ-ИЛИ на транзисторах, содержащие запоминающий конденсатор и диодную переключающую схему.

П.редлол ;енный логический динамический Элемент отличается от известных тем, что запоминающий конденсатор включен между эмиттером входного транзистора и обиХей щиной, а база выходного транзистора через резистор соединена с эмиттером входного транзистора и через резистор и диод - с источником тактовых импульсов.

Это повыщает быстродействие и увеличивает помехоустойчивость.

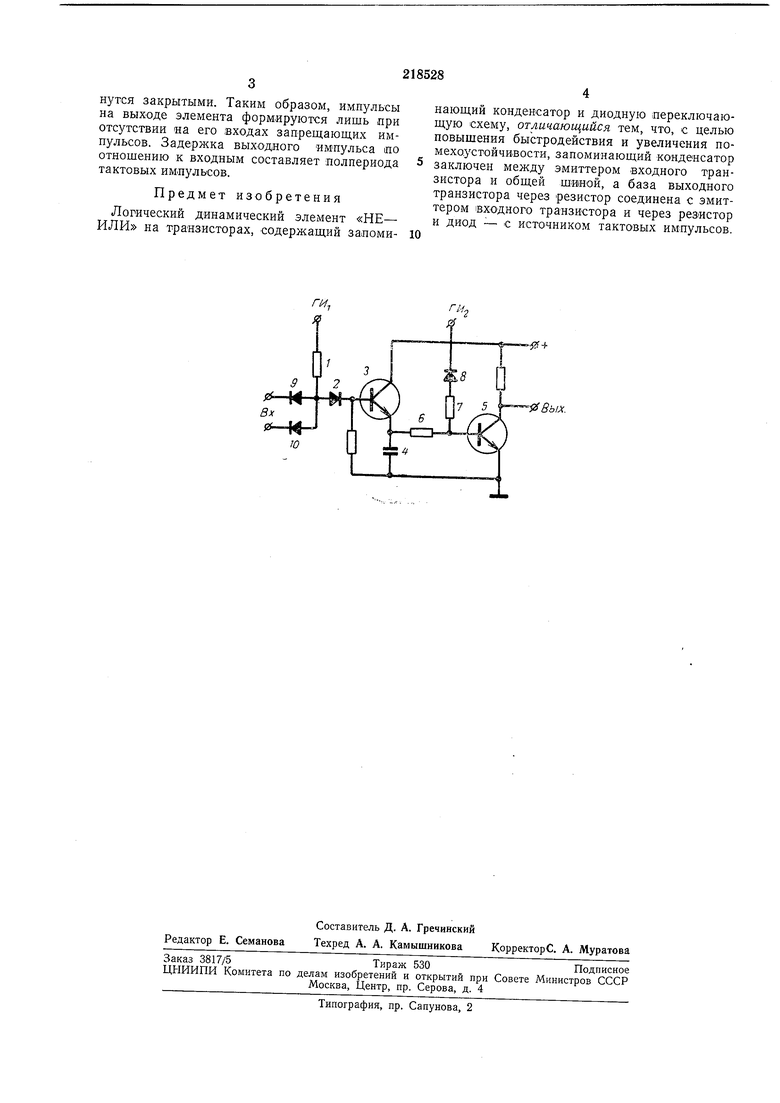

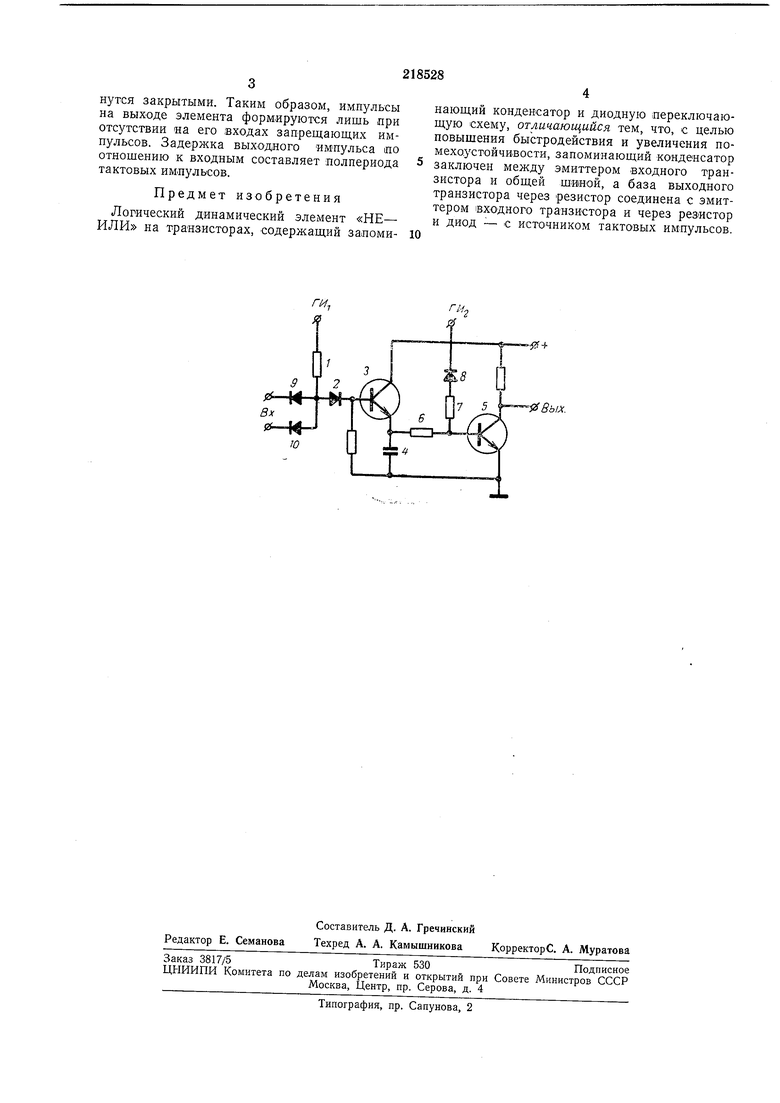

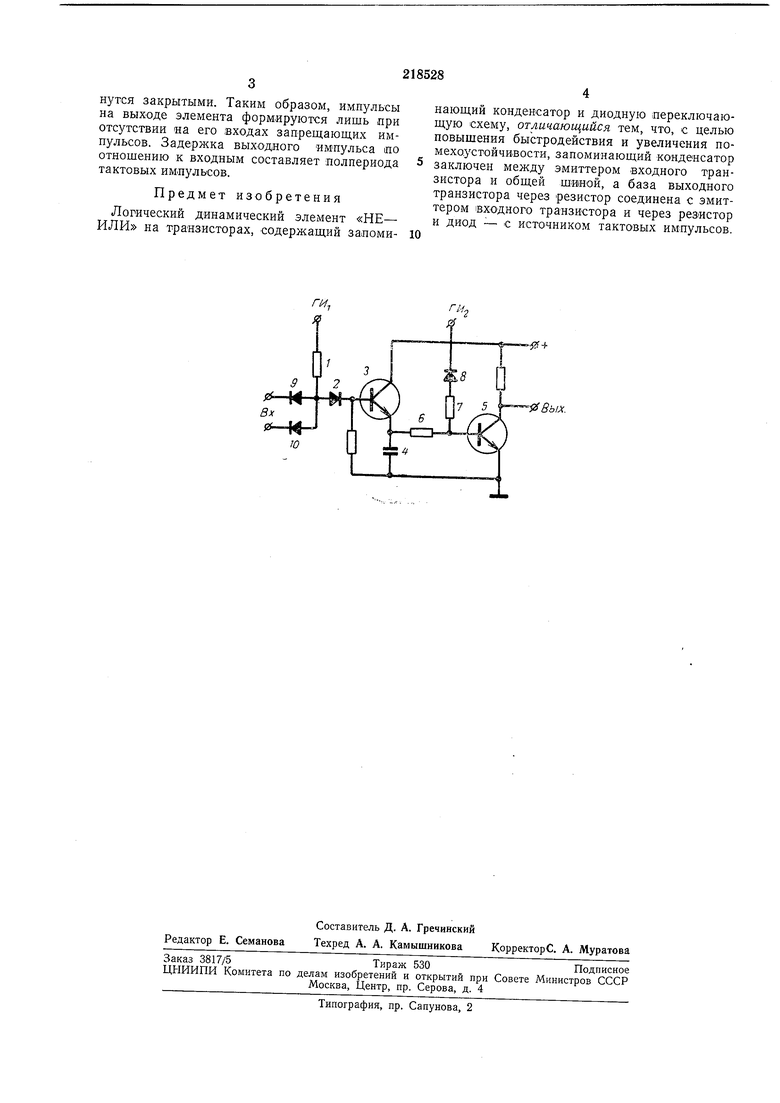

На чертеже приведена принципиальная электрическая схема логического элемента.

Источник тактовых импульсов ГИ через резистор 1 и диод 2 подключен к базе транзистора 3, эмиттер которого соединен с запоминающим конденсатором 4. База выходного транзистора 5 через резистор 6 соединена с эмиттером транзистора 3, а через резистор 7 и диод 8 - с источником тактовых импульсов ГИ, причем импульсы ГЯо сдвинуты относительно импульсов ГИ на полпериода. Если на входе элемента нет запрещающих импульсов, то от источника тактовых импульсов ГИ через резистор /, диод 2 и транзистор 3 происходит заряд конденсатора

4, при этом транзистор 3 выполняет функции усилителя тока.

Напряжение на конденсаторе 4 от некоторого отрицательного значения в исходном состоянии увеличивается сначала до нуля, а затем становится положительным. При достижении уровня отпирания транзистора 5, последний открывается и входи г в насыщение. После окончания положительной полуволны диоды 2, S и транзистор 3 закрываются. Транзистор 5 продолжает оставаться в насыщенном состоянии (благодаря току разряда конденсатора 4 через резистор 6 и цепь базы этого транзистора). Насыщенное состояние транзистора 5 сохраняется в течение всего полупериода.

Транзистор 5 запирается после того, как поступит отрицательная полуволна. При этом с конденсатора 4 снимается оставшийся заряд, напряжение на нем становится отрицательным и фиксируется транзистором 3 на уровне прямого падения напряжения «а переходе эмиттер-база. Выходной отрицательный импу.тьс снимается с коллектора транзистора 5.

нутся закрытыми. Таким образом, импульсы на выходе элемента формируются лишь при отсутствии на его входах запрещающих импульсов. Задержка выходного импульса по отношению к входным составляет полпериода тактовых имлульсов.

Предмет изобретения

Логический динамический элемент «НЕ- ИЛИ на транзисторах, содержащий запоминающий конденсатор и диодную переключающую схему, отличающийся тем, что, с целью повышения быстродействия и увеличения помехоустойчивости, запоминающий конденсатор заключен между эмиттером входного транзистора и общей шиной, а база выходного транзистора через резистор соединена с эмиттером входного транзистора и через резистор и диод - с источником тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

| МНОГОВХОДНОЙ ДИНАМИЧЕСКИЙ ИНВЕРТОР НА ТРАНЗИСТОРАХ | 1968 |

|

SU209838A1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И-ИЛИ», «И-ИЛИ-НЕ» | 1969 |

|

SU238599A1 |

| ИМПУЛЬСНЫЙ ДВУХФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ/И—ИЛИ—НЕ» | 1971 |

|

SU304698A1 |

| ЛОГИЧЕСКАЯ СХЕМА «И—НЕ/И» | 1970 |

|

SU262952A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1997 |

|

RU2147772C1 |

| РАЗРЯД ДИНАМИЧЕСКОГО РЕГИСТРА СДВИГА | 1972 |

|

SU324711A1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1969 |

|

SU249421A1 |

| УНИВЕРСАЛЬНЫЙ ДИНАЛ1ИЧЕСКИЙ ЭЛЕМЕНТ | 1969 |

|

SU253867A1 |

гя,

-j0Вы.

Даты

1968-01-01—Публикация