Предлагаемое устройство относится к области импульсных вычислительных устройств.

Известны ycTpoiicTBa для деления двух частотно-модулированных последовательностей импульсов, построенные на элементах цифровой вычислптельной техники.

Предлагаемое устройство отличается от известных тем, чго в нем вход делительного триггера подключен через элемент задержки к источнику сигиала-делителя, а его выход соединен с нулевым входом управляющего триггера, единичный вход которого через элемент задержки связан с тактовым входом устройства и со входом вентиля, управляющий вход которого подключен к выходу управляющего триггера, выход вентиля соединен со входом триггерного счетчика тактовых имп льсов, а выход триггера последнего разряда этого счетчика через элемент задержки связан с единичными входами всех триггеров счетчика.

Такое выполнение устройства позволяет упростить конструкцию устройства без снижения его точности.

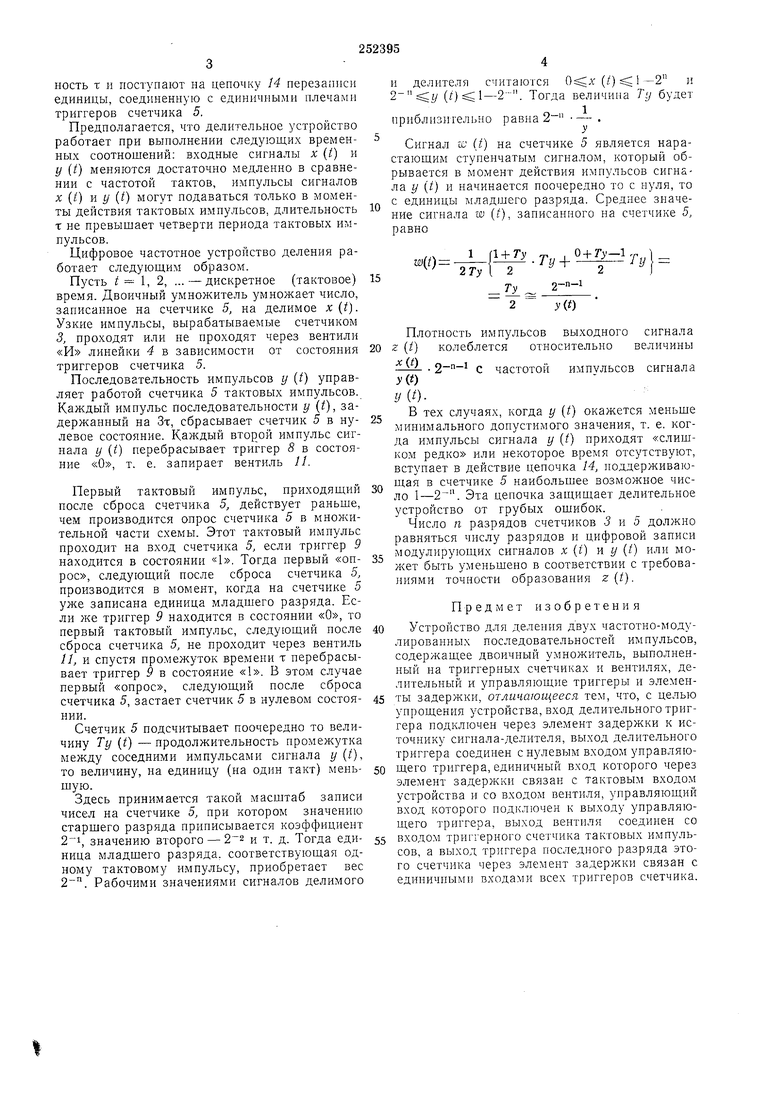

На чертеже представлена блок-схема описываемого устройства.

На вход .4 устройства подаются импульсы сигнала х (/) делимого, которые через элемент 1 задержки иа длительность 2т поступают на вход 2 триггерного счетчика 3. Триггеры счетчика 3 имеют импульсные выходы, где вырабатываются узкие импульсы при переходе триггеров из состояния «О в состояние «1.

Импульсные выходы триггеров соединены с

импульсными входами вентилей «И линейки

4. Р1мцульсные выходы вентилей «И л тейк1

4 собраны на выходе делительного устройства.

Вентили «И линейки 4 управляются но иотенциальиым входам триггерами счетчика 5 таким образом, что каждый вентиль открыт для прохождения через него узких импульсов только тогда, когда соответствующий триггер находится в состоянии «Ь.

Импульсы у (/) делителя поступают со входа Б устройства через элемент 6 задержки на длительность 3т на счетный вход одноразрядного делнтеля 7 частоты, состоящего из триггера, и на цепочку 8 сброса счетчика 5 в нулевое состояние. Выход делителя 7 соединен с нулевым плечом управляющего триггера 9. Тактовые имиульсы со входа В устройства проходят через элемент 10 задержки на длительность т на единичный вход триггера 9 и на импульсный вход вентиля 11. Вентиль // управляется НС потенциальному входу триггером 9 таким образом, что вентиль открыт только тогда, когда триггер 9 находигся в состоянии «1. Импульсный выход вентиля // соединен со счетным входом 12 счетчика 5.

ность т и поступают на цепочку 14 перезаписи единицы, соединенную с единичными плечами триггеров счетчика 5.

Предполагается, что делительное устройство работает при выполнении следующих временных соотношений; входные сигналы х (/) и у (t) меняются достаточно медленно в сравнении с частотой тактов, импульсы сигналов X i VI. у (t) могут подаваться только в моменты действия тактовых импульсов, длительность т не превышает четверти периода тактовых импульсов.

Цифровое частотное устройство деления работает следуюшим образом.

Пусть if 1, 2, ... - дискретное (тактовое) время. Двоичный умножитель умножает число, записанное на счетчике 5, на делимое x(t). Узкце импульсы, вырабатываемые счетчиком 3, проходят или не проходят через вентили «И линейки 4 в зависимости от состояния триггеров счетчика 5.

Последовательность импульсов у (t) управляет работой счетчика 5 тактовых импульсов. Каждый импульс последовательности у (t), задержанный на 3т, сбрасывает счетчик 5 в нулевое состояние. Каждый второй импульс сигнала у (t) перебрасывает триггер 8 в состояние «О, т. е. запирает вентиль 11.

Первый тактовый импульс, приходяший после сброса счетчика 5, действует раньше, чем производится опрос счетчика 5 в множительной части схемы. Этот тактовый импульс проходит на вход счетчика 5, если триггер 9 находится в состоянии «1. Тогда первый «опрос, следующий после сброса счетчика 5, производится в момент, когда на счетчике 5 уже записана единица младшего разряда. Если же триггер 9 находится в состоянии «О, то первый тактовый импульс, следующий после сброса счетчика 5, не проходит через вентиль 11, и спустя промежуток времени т перебрасывает триггер 9 в состояние «1. В этом случае первый «опрос, следующий после сброса счетчика 5, застает счетчик 5 в нулевом состоянии.

Счетчик 5 подсчитывает поочередно то величину Ту (t} - продолжительность промежутка между соседними импульсами сигнала y(t), то величину, на единицу (на один такт) меньшую.

Здесь принимается такой масштаб записи чисел на счетчике 5, при котором значению старшего разряда приписывается коэффициент , значению второго - 2 и т. д. Тогда единица младшего разряда, соответствуюшая одному тактовому импульсу, приобретает вес 2. Рабочими значениями сигналов делимого

и делителя считаются (/) 1 -2 и (. Тогда величина Ту будет

приблизшельно равна 2

Сигнал ш (/) на счетчике 5 является нарастаюшим ступенчатым сигналом, который обрывается в момент действия импульсов сигнала у (/) и начинается поочередно то с нуля, то с единицы младшего разряда. Среднее значение сигнала ш (t), записанного на счетчике 5, равно

1 fl + Ty

Ту +

2 ГУ I 2

9-П-1

Т 2

y(t)

Плотность импульсов выходного сигнала Z (t) колеблется относительно величины

X f i

-i- . с частотой ИМПУЛЬСОВ сигнала y(i)

y(t}.

В тех случаях, когда у (t) окажется меньше минимального допустимого значения, т. е. когда импульсы сигнала у (t) приходят «слишком редко или некоторое время отсутствуют, вступает в действие цепочка 14, поддерживающая в счетчике 5 наибольшее возможное число 1-2. Эта цепочка защищает делительное устройство от грубых ошибок.

Число п разрядов счетчиков 5 и 5 должно равняться числу разрядов и цифровой записи

модулирующих сигналов х (t и у (t) или может быть уменьшено в соответствии с требованиями точности образования z (t).

Предмет изобретения

Устройство для деления двух частотно-модулированных последовательностей импульсов, содержащее двоичный умножитель, выполненный на триггерных счетчиках и вентилях, делительный и управляющие триггеры и элементы задержки, отличающееся тем, что, с целью упрощения устройства, вход делительного триггера подключен через элемент задержки к источнику сигнала-делителя, выход делительного триггера соединен с нулевым входом управляющего триггера, единичный вход которого через элемент задержки связан с тактовым входом устройства и со входом вентиля, управляющий вход которого подключен к выходу управляющего триггера, выход вентиля соединен со

входом триггерного счетчика тактовых импульсов, а выход триггера последного разряда этого счетчика через элемент задержки связан с единичными входами всех триггеров счетчика.

А(

t; --- j; J .K.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ | 1969 |

|

SU253138A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕМОДУЛЯТОР | 1970 |

|

SU264450A1 |

| УПРАВЛЯЕМЫЙ ВЕРОЯТНОСТНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU370717A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

.

Даты

1969-01-01—Публикация