Известны множительно-делительные устройства последовательно-параллельного типа с представлением чисел в позиционной системе счисления, содержащие регистр множимого (делителя), реверсивные счетчики множителя (частного) и произведения (делимого), матрицу с распределителем сдвига и преобразователи кода множимого в унитарный код.

Предложенное устройство отличается от известных тем, что оно содержит триггер, единичный вход которого подключен через вентили к выходам счетчиков множителя и делимого, единичный выход триггера подсоединен к первому входу вентиля, второй вход которого через ячейку задержки соединен с выходом тактирующего устройства, выход вентиля подсоединен к нулевому входу указанного триггера, входу распределителя и счетному входу второго триггера, единичный и нулевой выходы которого соединены соответственно с двумя шинами реверса счетчиков множителя и произведения. Это позволяет упростить устройство.

Способ вычисления произведения, заложенный в устройство, состоит в следующем. Перед старщим разрядом множителя помещается условный двоичный разряд, к которому в начале операции приписывается значение «Ьх Формирование произведения начинается с образования частичного произведения множимого на цифру в старшем разряде мнол :ителя.

что получается последовательным сложением множимого с накоплением результата. Количество сложений при этом вычитается из старшего разряда мнол ителя до перехода условного разряда от «1 к «О, вызываемого переносом из старшего разряда множителя при изменении его знака. Это приводит к сдвигу множителя и произведения, вычитанию мнолсимого из предыдущего частичного произведения и прибавлению количества вычитаний ко второму разряду множителя до перехода условного разряда от «О к «1, соответствующего повторному изменению знака множителя, и т. д., как это показано на примере.

20

25

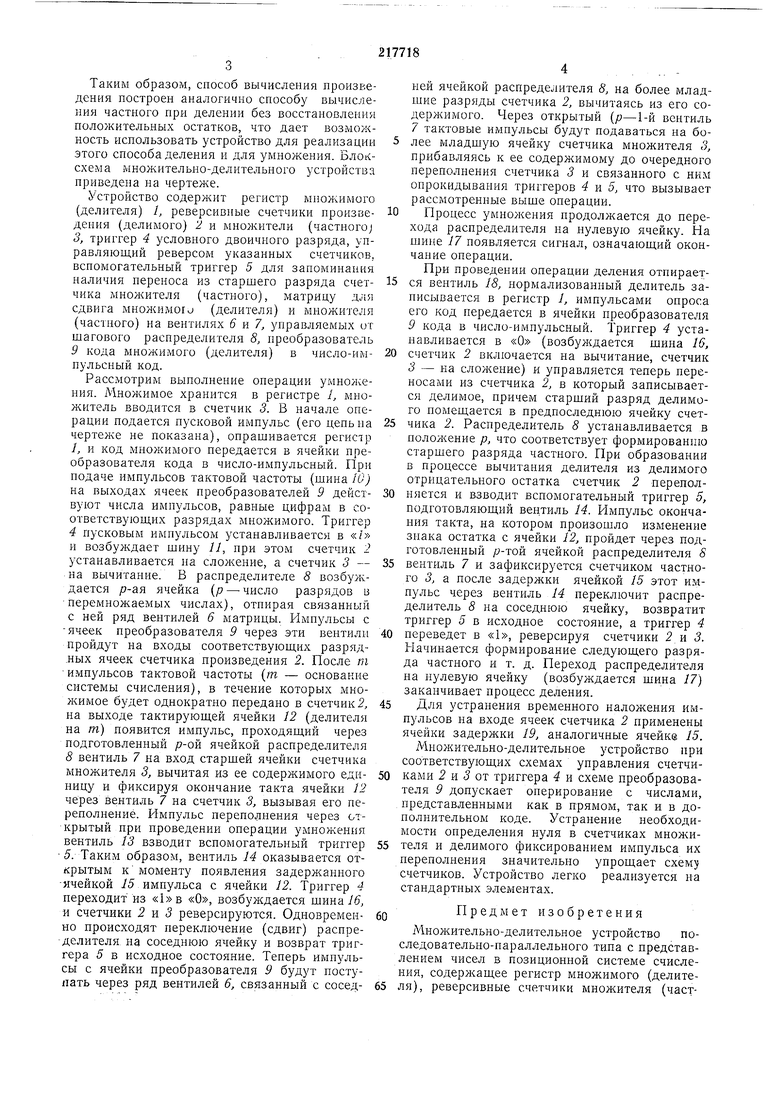

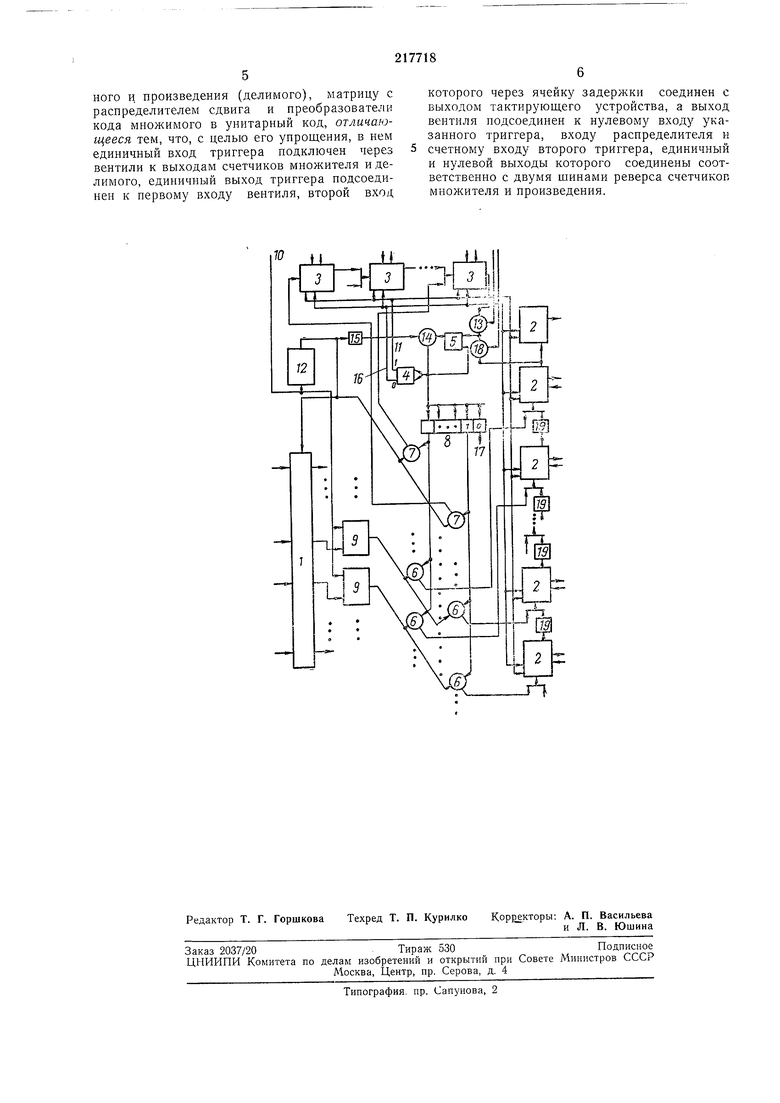

Таким образом, способ вычисления произведения построен аналогично способу вычисления частного при делении без восстановлении положительных остатков, что дает возможность использовать устройство для реализации этого способа деления и для умножения. Блоксхема множительно-делительного устройства приведена на чертеже.

Устройство содержит регистр множимого (делителя) I, реверсивные счетчики произведения (делимого) 2 и множители (4acTHoroj 3, триггер 4 условного двоичного разряда, управляющий реверсом указанных счетчиков, вспомогательный триггер 5 для запоминания наличия нереноса из старшего разряда счетчика множителя (частного), матрицу для сдвига множимого (делителя) и множителя (частного) на вентилях 6 к 7, управляемых от шагового распределителя 8, преобразователь 9 кода множимого (делителя) в число-импульсный код.

Рассмотрим выполнение онерации умножения. Множимое хранится в регистре 1, множитель вводится в счетчик 3. В начале операции подается пусковой импульс (его цепьиа чертеже не показана), опрашивается регистр 1, и код множимого передается в ячейки преобразователя кода в число-импульсный. При подаче импульсов тактовой частоты (шина 10) на выходах ячеек преобразователей 9 действуют числа импульсов, равные цифрам в соответствуюш,их разрядах множимого. Триггер 4 пусковым импульсом устанавливается в «/ и возбуждает шину 11, при этом счетчик 2 устанавливается на сложение, а счетчик 3 - на вычитание. В распределителе 8 возбуждается ячейка (р - число разрядов в перемножаемых числах), отпирая связанный с ней ряд вентилей 6 матрицы. Импульсы с

-ячеек преобразователя 9 через эти вентили цройдут на входы соответствующих разряд.ных ячеек счетчика произведения 2. После т

импульсов тактовой частоты (т - основание системы счисления), в течение которых множимое будет однократно передано в счетчик 2, на выходе тактирующей ячейки 12 (делителя на от) появится импульс, проходящий через подготовленный /з-ой ячейкой распределителя 8 вентиль 7 на вход старшей ячейки счетчика множителя 3, вычитая из ее содержимого единицу и фиксируя окончание такта ячейки 12 через вентиль 7 на счетчик 3, вызывая его переполнение. Импульс переполнения через открытый при проведении операции умножения вентиль 13 взводит вспомогательный триггер

5. Таким образом, вентиль 14 оказывается открытым к моменту появления задержанного

-ячейкой У5 импульса с ячейки 12. Триггер 4 переходитиз «О, возбуждается шина/б и счетчики 2 и 5 реверсируются. Одновременно происходят переключение (сдвиг) распреней ячейкой распределителя 8, на более младшие разряды счетчика 2, вычитаясь из его содержимого. Через открытый (р-1-й вентиль 7 тактовые импульсы будут подаваться на более младшую ячейку счетчика множителя 3, прибавляясь к ее содержимому до очередного переполнения счетчика 3 и связанного с ним опрокидывания триггеров и 5 что вызывает рассмотренные выше операции.

Процесс умножения продолжается до перехода распределителя на нулевую ячейку. На шине /7 появляется сигнал, означающий окончание операции.

При проведении операции деления отпирается вентиль 18, нормализованный делитель записывается в регистр 1, импульсами опроса его код передается в ячейки преобразователя 9 кода в число-импульсный. Триггер 4 устанавливается в «О (возбуждается шина 16,

счетчик 2 включается на вычитание, счетчик 3 - иа сложение) и управляется теперь нереносами из счетчика 2, в который записывается делимое, причем старший разряд делимого помещается в предпоследнюю ячейку счетчика 2. Распределитель 8 устанавливается в положение р, что соответствует формированию старшего разряда частного. При образовании в процессе вычитания делителя из делимого отрицательного остатка счетчик 2 цереполняется и взводит вспомогательный триггер 5, подготовляющий вентиль 14. Импульс окончания такта, на котором произошло изменение знака остатка с ячейки 12, пройдет через подготовленный /у-той ячейкой распределителя 8

вентиль 7 и зафиксируется счетчиком частного 3, а после задержки ячейкой 15 этот импульс через вентиль 14 переключит распределитель 5 на соседнюю ячейку, возвратит триггер 5 в исходное состояние, а триггер 4

переведет в «1, реверсируя счетчики 2 и 3. Начинается формирование следующего разряда частного и т. д. Переход распределителя на пзлевую ячейку (возбуждается шина 17) заканчивает процесс деления.

Для устранения временного наложения импульсов на входе ячеек счетчика 2 применены ячейки задержки 19, аналогичные ячейке 15. Множительно-делительное устройство при соответствующих схемах управления счетчиками 2 и 5 от триггера 4 и схеме преобразователя 9 допускает оперирование с числами, представленными как в прямом, так и в дополнительном коде. Устранение необходимости определения нуля в счетчиках мнол ителя и делимого фиксированием импульса их переполнения значительно упрощает схем счетчиков. Устройство легко реализуется на стандартных элементах.

П р е д м е т и 3 о б р е т е н и я

Множительно-делительное устройство последовательно-параллельного типа с представлением чисел Б позиционной системе счисления, содержащее регистр множимого (делителя), реверсивные счетчики мнолштеля (частного и произведения (делимого), матрицу с распределителем сдвига и преобразователи кода множимого в унитарный код, отличающееся тем, что, с целью его упрощения, в нем единичный вход триггера подключен через вентили к выходам счетчиков множителя и делимого, единичный выход триггера подсоединен к первому входу вентиля, второй вход

которого через ячейку задержки соединен с выходом тактирующего устройства, а выход вентиля нодсоединен к нулевому входу указанного триггера, входу распределителя и счетному входу второго триггера, единичный и нулевой выходы которого соединены соответственно с двумя шинами реверса счетчикоп множителя и произведения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| ЦИФРОВОЕ УСТРОЙСТВО для УСКОРЕННОГО ДЕЛЕНИЯ | 1973 |

|

SU367421A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Делительное устройство | 1973 |

|

SU470805A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

0 11

Даты

1968-01-01—Публикация