Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления производственными процессами.

Известно множительно-делительное устройство, содержащее счетчики импульсов, реверсивный счетчик, регистр памяти, шесть триггеров, тринадцать элементов И, дешифратор, элементы ИЛИ, группы элементов И, элементы задержки [1] .

Недостатками этого устройства являются ограниченный диапазон и низкая точность вычислений.

Наиболее близким по технической сущности и достигаемому эффекту к изобретению является частотно-импульсное множительно-делительное устройство, содержащее первый и второй счетчики, регистр, блок определения величины управляющих сигналов, блок регулировки задержки, первый, второй, третий, четвертый, пятый и шестой триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, первую и вторую группы элементов И, элемент ИЛИ, первый, второй, третий, четвертый, пятый и шестой элементы задержки [2] .

Недостатками известного устройства являются относительно низкая точность реализации множительно-делительной операции и ограниченный диапазон изменения входных сигналов. Это обусловлено тем, что в зависимости от соотношения значений ΔТн и Δ Тк ( Δ Тн - интервал времени между поступлением импульсов частоты F2 и моментом поступления импульсов частоты F1 в начале интервала Т1, Δ Тк - интервал времени между моментом поступления импульса частоты F2 и моментом поступления импульса частоты F1 в конце интервала Т1) величина поправки периода выходной частоты может изменяться в пределах от 0 до 2Т3 (Т3 - период частоты F3).

В соответствии с принципом действия известного устройства после каждого очередного пересчета информации в счетчике сигналами с выхода блока сдвига фазы на выходе элемента И появляется сигнал, который далее задерживается на величину ΔТ, определяемую выражением

ΔT=  T2+(ΔTк-ΔTн)

T2+(ΔTк-ΔTн)

Но в известном устройстве правильная реализация коррекции периода выходного сигнала осуществима лишь для случая, если поправка периода лежит в пределах от 0 до Т3. В интервале Т3 < ΔT < 2T3 в известном устройстве появляется погрешность за счет того, что за время задержки сигнала с выхода элемента И на величину, большую Т3, на вход счетчика может поступить сигнал с выхода блока сдвига фазы, что нежелательно и приводит к погрешности устройства. Правильная работа осуществляется лишь только в том случае, когда определенным образом синфазированные сигналы с выхода блока сдвига фазы начинают поступать на вход счетчика только после появления сигнала с выхода блока регулировки задержки.

В частотно-импульсное множительно-делительное устройство, содержащее первый и второй счетчики, регистр, блок определения величины управляющих сигналов, блок регулировки задержки, блок сдвига фазы, первый, второй, третий, четвертый, пятый и шестой триггеры, дешифратор единицы, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первую и вторую группы элементов И, элемент ИЛИ, первый, второй, третий, четвертый, пятый и шестой элементы задержки, причем разрядные выходы первого счетчика подключены к соответствующим информационным входам регистра через первую группу элементов И, вторые входы элементов И первой группы через первый элемент задержки подключены к управляющему входу регистра, который через второй элемент задержки подключен к первому входу первого счетчика, и непосредственно к входу установки в единицу первого триггера, к выходу первого элемента И и через третий элемент задержки к синхровходу второго триггера, выход второго триггера подключен к первому входу второго элемента И, выход которого соединен с входом установки в единицу третьего триггера, инверсный выход которого связан с первым входом третьего элемента И, второй вход которого подключен к первому информационному входу устройства и к первому входу первого элемента И, второй вход первого элемента И подключен к управляющему входу устройства и к первому входу четвертого элемента И, второй вход которого подсоединен к выходу третьего триггера, третий вход четвертого элемента И связан с вторым информационным входом устройства и с первым входом пятого элемента И, второй вход которого подключен к выходу четвертого триггера и к первому входу шестого элемента И, второй вход шестого элемента И подключен к третьему информационному входу устройства и к первым входам седьмого и восьмого элементов И, выход седьмого элемента И через четвертый элемент задержки подключен к синхровходу четвертого триггера, второй вход седьмого элемента И соединен с выходом первого триггера и с вторым входом восьмого элемента И, выход которого связан с вторым входом первого счетчика, разрядные выходы регистра подключены к первым входам элементов И второй группы, выходы которых соединены с соответствующими установочными входами второго счетчика, вторые входы элементов И второй группы связаны с выходом пятого элемента задержки, выход шестого элемента И подключен к входу установки в единицу пятого триггера, выход которого соединен с третьим входом седьмого элемента И, выход пятого элемента И связан с первым входом элемента ИЛИ, выход шестого элемента задержки подключен к третьему информационному входу устройства, а выход подсоединен к входу установки в единицу шестого триггера, выход которого связан с третьим входом восьмого элемента И, вход установки в ноль шестого триггера через второй элемент задержки подключен к входу установки в единицу первого триггера, второй вход элемента ИЛИ подсоединен к выходу блока регулировки задержки, к управляющему входу блока сдвига фазы, информационный вход которого связан с выходом четвертого элемента И, выход блока сдвига фазы подключен к счетному входу второго счетчика и управляющему входу дешифратора единицы, информационные входы которого подсоединены к разрядным выходам второго счетчика, а выход дешифратора единицы связан с первым входом блока регулировки задержки и с входом пятого элемента задержки, второй вход блока регулировки задержки подключен к выходу блока определения величины управляющих сигналов, первый вход которого подсоединен к третьему информационному входу устройства, второй вход блока определения величины управляющих сигналов связан с выходом первого элемента И, а третий вход - с вторым информационным входом устройства, выход элемента ИЛИ является выходом устройства, введена связь выхода дешифратора единицы с входом установки в ноль блока сдвига фазы.

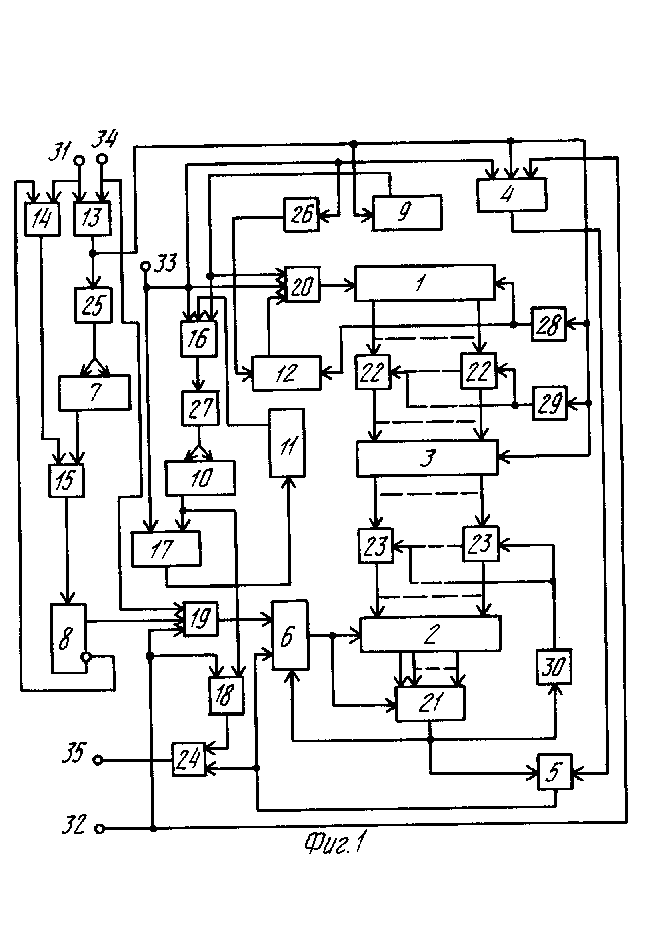

На фиг. 1 приведена структурная схема предложенного частотно-импульсного множительно-делительного устройства; на фиг. 2 - структурная схема блока сдвига фазы.

Частотно-импульсное множительно-делительное устройство содержит счетчики 1,2, регистр 3 памяти, блок 4 определения величины управляющих сигналов, блок 5 регулировки задержки, блок 6 сдвига фазы, триггеры 7-12, элементы И 13-20, дешифратор 21 единицы, группы элементов И 22,23, элемент ИЛИ 24, элементы 25-30 задержки, информационные входы 31,32,33, управляющие входы 34,35, соединенные между собой функционально.

Блок 6 сдвига фазы состоит из триггерного регистра 36, первой группы 37 элементов И, второй группы 38 элементов И, элемента ИЛИ 39, группы 40 элементов задержки и имеет вход 41 подачи управляющего сигнала, вход 42 подачи информационного сигнала частоты F3, выход 43 и вход 44 подачи сигнала установки в ноль, соединенные между собой функционально.

Частотно-импульсная множительно-делительное устройство работает следующим образом.

Входные сигналы первой последовательности с частотой следования F1, характеризующие один из сомножителей, подаются на вход 31. Сигналы с частотой следования F3, характеризующие другой сомножитель, подаются на вход 32. Сигналы с частотой следования F2, характеризующие делитель, подаются на вход 33. Далее сигналы последовательно с частотой F1 подаются на входы элементов И 13 и 14, сигнал с частотой F2 - на входы элементов И 16, 17, 20 и на вход элемента 26 задержки, сигналы с частотой F3 - на входы элементов И 18 и 19. Наряду с этим все три последовательности подаются на входы блока 4.

В исходном состоянии счетчики 1,2, регистр 3 и триггеры обнулены.

На вход 34 подается сигнал разрешения. При этом первый импульс, подаваемый на вход 31, проходит через элемент И 13 и переводит триггер 9 в единичное состояние. В результате открывается элемент И 20 и на вход счетчика 1 начинают проходить сигналы, характеризующие делитель с частотой F2, которые накапливаются в счетчике 1 до момента поступления следующего входного сигнала на вход 31.

Следует отметить, что подача одного из импульсов частоты F2 на вход счетчика 1 запрещается. Это осуществляется с помощью триггера 12, элемента 26 задержки и элемента И 20.

Сигнал из последовательности F1 каждый раз устанавливает триггер 12 в нулевое состояние, запирая элемент И 20. При этом первый после подачи сигнала из последовательности F1 сигнал частоты F2 не проходит через элемент И 20, а, проходя через элемент 26 задержки, устанавливает триггер 12 в единичное состояние. Все последующие сигналы частоты F2 проходят на вход счетчика 1. Одновременно с подачей сигнала на вход 31 блок 4 начинает определение управляющего сигнала поправки периода выходного сигнала.

С поступлением следующего (второго после подачи сигнала разрешения) импульса информация, накопленная в счетчике 10 передается через элементы И 22 в регистр 3, где запоминается, а счетчик 1 обнуляется.

Необходимый временной сдвиг между моментами подачи информации и обнулением счетчика 1 осуществляется с помощью элементов 28, 29 задержки. Далее процесс повторяется.

С приходом каждого последующего импульса из последовательности с частотой следования F1 он осуществляет обнуление регистра 3 и подачу накопленной в счетчике 1 информации в регистр 3, а также обнуление счетчика 1.

Необходимая задержка в подаче сигналов из последовательности F3 на вход счетчика 2 в данном случае осуществляется с помощью триггеров 7,8, элементов И 14,15 и элемента 25 задержки.

После подачи сигнала разрешения на вход 34 первый сигнал из последовательности с частотой F1 проходит на выходы элементов И 13, 14. При этом с выхода элемента И 13 он поступает через элемент 25 задержки на счетный вход триггера 7, переводя его из нулевого в единичное состояние. Очевидно, что при этом сигнал с выхода элемента И 14 не проходит на вход элемента И 15, так как отпирающий сигнал с триггера 7 выдается на его вход с задержкой элементом 25 задержки.

При поступлении следующего сигнала на вход 31 сигнал с выхода элемента И 14 проходит на выход элемента И 15, переводя триггер 8 в единичное состояние. В результате открывается элемент И 19 и на вход счетчика 2 через блок 6 сдвига фазы начинают подаваться импульсы с частотой следования F3. С переводом триггера 8 в единичное состояние элемент И 14 запирается для сигналов, подаваемых на вход 31.

Для получения информации о результате в течение первого периода частоты F1 служат элементы И 16, 17, 18, триггеры 10, 11 и элемент 27 задержки.

После подачи сигнала разрешения на вход 34, прохождения импульса с входа 31 через элемент И 13 и перевода триггера 9 в единичное состояние на выход элемента И 16 проходит сигнал последовательности F2 с входа 33. Одновременно импульс с входа 33 подается на вход элемента И 17.

С выхода элемента И 16 сигнал через элемент 27 задержки проходит на счетный вход триггера 10, переводя его в единичное состояние. При этом открывается элемент И 18 и на его выход проходят сигналы с входа 32 и далее через элемент ИЛИ 24 на выходную клемму 35, образуя первые сигналы результатов.

При поступлении следующего сигнала с входа 33 он проходит через элемент И 17, в результате чего триггер 11 переводится в единичное состояние, а при подаче сигнала на счетный вход триггера 10 последний переводится в нулевое состояние. При этом запираются элементы И 16, 17 и 18. В результате выдача импульсов с входа 32 прекращается, что необходимо для нормального функционирования устройства.

Выходные сигналы пересчета со счетчика 2 формируются на выходе многовходового дешифратора 21, подключенного к разрядным выходам счетчика 2 так, что он открывается для входных сигналов с частотой F3 лишь в момент достижения в счетчике 2 единичной информации. В этом момент появляется на его выходе сигнал пересчета.

Указанные сигналы подаются на вход блока 5 регулировки задержки, на третий вход блока 6 сдвига фазы и через элемент 30 задержки на управляющие входы элементов группы И 23. В результате этого информация, запомненная в регистре 3, периодически передается через элементы И 22 группы в счетчик 2, образуя его исходную уставку, а также осуществляются задержка сигнала, вырабатываемого в блоке 4, и запрет в подаче сигналов с выхода блока 6 сдвига фазы на счетный вход счетчика 2 до момента появления сигнала на выходе блока 5. Задержанные сигналы с выхода блока 5 регулировки задержки подаются на второй вход блока 6 сдвига фазы, снимая запрет в подаче сигналов на вход счетчика 2, и через элемент ИЛИ 24 на выход 35 устройства.

На выходе блока 6 сдвига фазы вырабатываются при подаче сигналов с выхода блока регулировки задержки сдвинутые по фазе сигналы с частотой F3 таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока 5 регулировки задержки. В этом случае на выходе блока 5 имеют место сигналы, период которых изменен на величину, вырабатываемую на выходе блока 4.

В зависимости от величины исходной уставки на выходе дешифратора 21 устанавливается вполне определенная частота. При этом каждый последующий импульс частоты F1 осуществляет периодический сброс старой информации в регистре 2 и запись новой информации.

Блок 6 сдвига фазы работает следующим образом.

Входной сигнал с выхода блока задержки устройства подается с входа 41 на первые входы элементов И группы 37, на вторые входы которых поступают сигналы частоты F3 с входа 42, последовательно задерживаемые элементами задержки из группы 40 элементов задержки. При этом на вход первого элемента И группы 37 поступает сигнал частоты F3, задержанный одним элементом задержки на величину Δ t, на вход второго элемента И группы 37 - сигнал эталонной частоты F3, задержанный двумя элементами задержки на величину 2 Δt и т. д.

При поступлении сигнала на вход 41 происходит его совпадение с одним из задержанных сигналов последовательности F3 и на выход соответствующего элемента И из группы 37 проходит сигнал, который переводит в единицу связанный с элементом И триггер 36. В результате открывается соответствующий элемент И из группы 38 для задержанных сигналов. При этом на выход открытого элемента И проходят задержанные на соответствующую величину сигналы эталонной частоты F3, которые далее через элемент ИЛИ 39 проходят на выход 43.

При подаче на вход 44 сигнала с выхода дешифратора 21 устройства на все триггеры регистра 36 подается сигнал установки в ноль и триггер, находящийся ранее в единичном состоянии, переводится в нулевое состояние. Прохождение задержанных сигналов эталонной частоты F3 на выход 43 при этом прекращается.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2042219C1 |

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА О СОСТОЯНИИ ОБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010261C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 1991 |

|

RU2010422C1 |

| СПОСОБ МОДУЛЯЦИИ ИМПУЛЬСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2022461C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2042150C1 |

| Частотно-импульсное множительноделительное устройство | 1975 |

|

SU595731A1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления производственными процессами. Частотно-импульсное множительно-делительное устройство содержит два счетчика 1, 2, регистр 3 памяти, блок 4 определения величины управляющих сигналов, блок 5 регулировки задержки, блок 6 сдвига фазы, шесть триггеров 7 - 12, восемь элементов И 13 - 20, дешифратор 21 единицы, две группы элементов И 22, 23, элемент ИЛИ 24 и шесть элементов 25 - 30 задержки, соединенные между собой функционально. 1 з. п. ф-лы, 2 ил.

Авторы

Даты

1994-04-30—Публикация

1992-07-27—Подача