Данное изобретение относится к области радиоэлектроники и предназначено для использования в вычислительной технике, системах связи, нейрокибернетике, где необходимо измерять фазовое рассогласование между двумя последовательностями импульсов.

Известны временные дискриминаторы для преобразования временных сдвигов между импульсами в напряжение, недостатком которых является малый диапазон измерения сдвига между импульсами, следующими с постоянной частотой.

Цель изобретения - создание устройства, которое могло бы преобразовать фазовое рассогласование любой величины между двумя последовательностями импульсов с частотами повторения, изменяющимися произвольно в широких пределах.

Это достигается путем использования четырех триггеров, один из которых определяе-j знак, второй - величину рассогласования, а два других управляют схемами совпадений, на выходы которых подаются последовательности импульсов, поступающих на счетный вход триггера величины рассогласования.

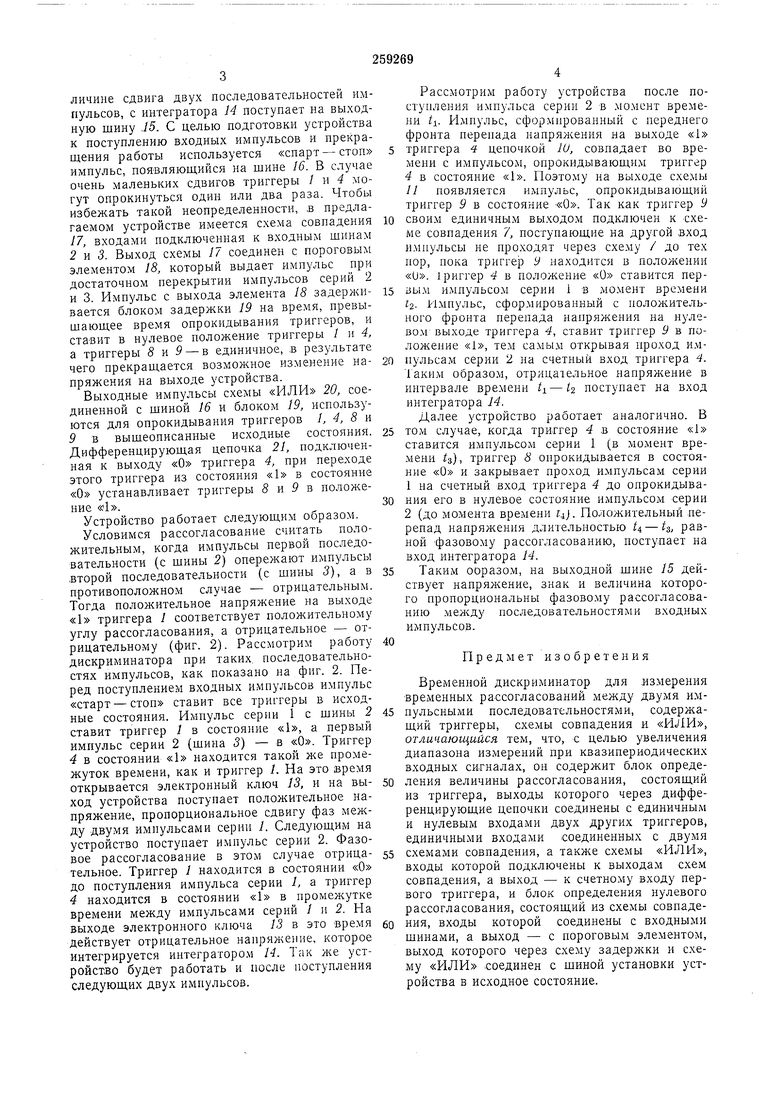

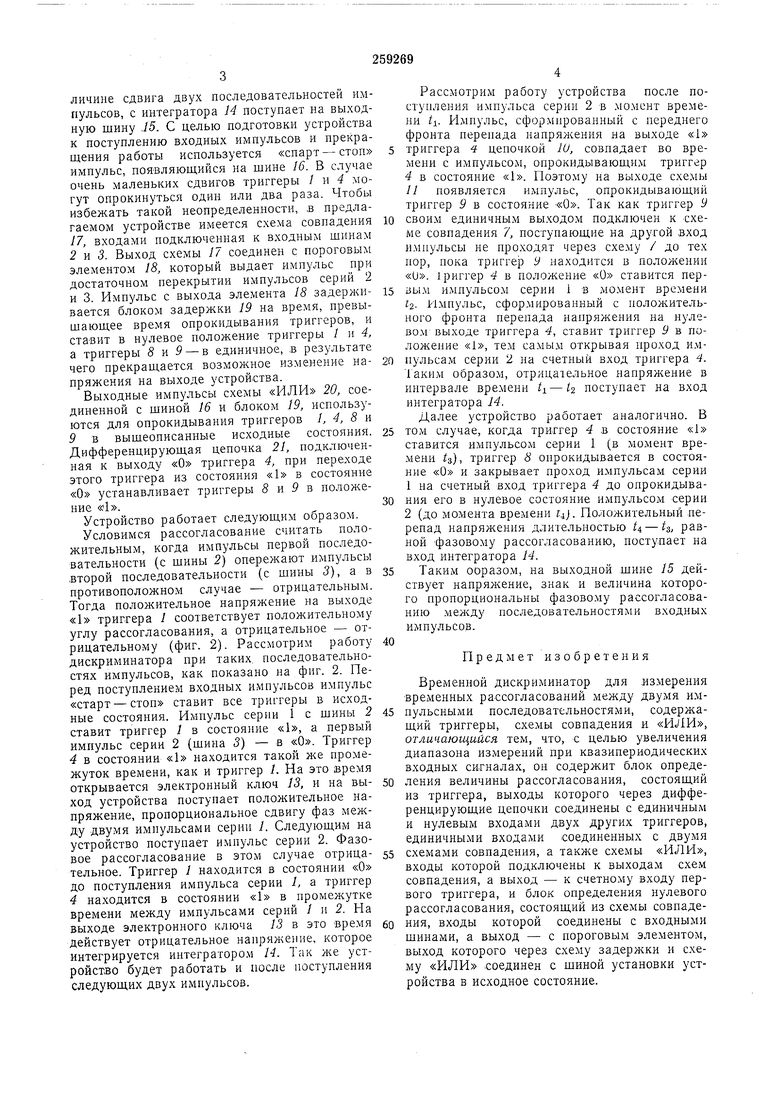

На фиг. 1 показана блок-схема устройства; на фиг. 2 - временные диаграммы работы дискриминатора.

ный и нулевой входы которого соединены соответственно с шинами 2 и 5 в.ходных импульсов. Величине рассогласования соответствует длительность положительного перепада напряжения на единичном выходе триггера 4, на счетный вход которого поступают импульсы с выхода схемы «ИЛИ 5. В устройство включены триггеры, перепады выходов которых одинаковы по величине и разные по знаку. Входы схемы «ИЛИ 5 соединены с выходами схем совпадения 6 и 7. На один вход схемы 6 поступают импульсы со входной шины 3, а второй вход подключен к единичному выходу триггера 8. Входы схемы совпадения 7 соединены соответственно с шиной 2 и выходом «1 триггера 9. Триггеры 5 и 9 ставятся в состояние «О импульсами той серии (2 и 3), поступлением которых на счетный вход триггера 4 они управляют, в том случае, когда триггер 4 переходит из нулевого в единичное состояние. Для этой цели служит дифференцирующая цепочка 10 и схемы совпадения /7 и 12. Так как знак рассогласования определяет полярность напряжения на выходе «1 триггера /, а величину - длительность положительного перепада напряжения на выходе «1 триггера 4, то эти триггеры подключены к входам электронного ключа 13, выход которого соединен с интегратором 14. Напряжение рассогласования, соответствующее знаку и неличине сдвига двух последовательно стей импульсов, с интегратора М поступает на выходную шнну .15. С целью нодготовки устройства к ноступлению входных имнульсов н нрекращения работы используется «спарт - стоп имнульс, появляющийся на шине 16. В случае очень маленьких сдвигов триггеры / н 4 могут опрокинуться один или два раза. Чтобы избежать такой неопределенности, ,в предлагаемом устройстве имеется схема совпадения 17, входами подключенная к входным шинам 2 н 5. Выход схемы 17 соединен с пороговым элементом 18, который выдает импульс при достаточном перекрытии импульсов серий 2 и 3. Импульс с выхода элемента 18 задерживается блоком задержки 19 на время, нревышаюш.ее время опрокидывания триггеров, и ставит в нулевое ноложение триггеры / и 4, а триггеры 8 и 5 - в единичное, ,в результате чего прекраш.ается возможное изменение напряжения на выходе устройства.

Выходные импульсы схемы «ИЛИ 20, соединенной с шиной 16 н блоком 19, используются для опрокидывания триггеров I, 4, 8 н 9 в вышеописанные исходные состояния. Дифференцируюш,ая цепочка 21, подключенная к выходу «О триггера 4, при переходе этого триггера из состояния «1 в состояние «О устанавливает триггеры 8 и Р в положение «1.

Устройство работает следуюш,им образом.

Условимся рассогласование считать положительным, когда импульсы первой последовательности (с шины 2) опережают импульсы второй последовательности (с шины 5), а в противоположном случае - отрицательным. Тогда положительное напряжение на выходе «1 триггера 1 соответствует положительному углу рассогласования, а отрицательное - отрицательному (фиг. 2). Рассмотрим работу дискриминатора при таких, носледовательностях импульсов, как показано на фиг. 2. Иеред ностунлением входных импульсов импульс «старт - стоп ставит все триггеры в исходные состояния. Имнульс серии 1 с шины 2 ставит триггер в состояние «1, а нервый импульс серии 2 (шина .3) - в «О. Триггер 4 в состоянии «1 находится такой же промежуток времени, как и триггер /. На это время открывается электронный ключ 13, и на выход устройства поступает положительное напряжение, пропорциональное сдвигу фаз между двумя импульсами серин 1. Следующим на устройство поступает имнульс серии 2. Фазовое рассогласовапие в этом случае отрицательное. Триггер 1 находится в состоянии «О до поступления импульса серии 1, а триггер 4 находится в состоянии «1 в промежутке времени между импульсами серий У и 2. На выходе электронного ключа 13 в это время действует отрицательное нанряжение, которое интегрируется интегратором И. Так же устройство будет работать и после поступления следующих двух импульсов.

Рассмотрим работу устройства после поступления импульса серин 2 в момент времени /1. Импульс, сформированный с переднего фронта перепада напряжения на выходе «1 триггера 4 цепочкой Ш, совпадает во времени с импульсом, опрокидывающим триггер 4 в состояние «1. Иоэтому на выходе схемы 11 появляется импульс, опрокидывающий триггер 9 в состояние «О. Так как триггер 9

своим единичным выходом подключен к схеме совпадения 7, ностунающие на другой вход нмиульсы не нроходят через схему / до тех пор, пока триггер У находится в положении «и. 1риггер 4 в положение «О ставится первым импульсом серии 1 в момент времени 12. Импульс, сформированный с положительного фронта перепада напряжения на нулевом выходе триггера 4, ставит триггер 9 в положение «1, тем самым открывая нроход и.мпульсам серии 2 на счетный вход триггера 4.

1аким образом, отрицательное напряжение в

интервале времени /i-tz ностунает на вход

интегратора 14.

Далее устройство работает аналогично. В

том случае, когда триггер 4 в состояние «1 ставится импульсом серии 1 (в момент времени 3)1 триггер 8 онрокидывается в состояние «О и закрывает проход импульсам серии

1на счетный вход триггера 4 до опрокидывания его в нулевое состояние нмпзльсом серии

2(до момента времени r4J. Иоложительный перепад напряжения длительностью /4 - з, равной фазовому рассогласованию, поступает на вход интегратора 14.

Таким ооразом, на выходной шине 15 действует нанрял ение, знак и величина которого пропорциональны фазовому рассогласованию между последовательностями входных импульсов.

Нредмет изобретения

Временной дискриминатор для .измерения временных рассогласований между двумя импульсными последовательностями, содержащий триггеры, схемы совнадения и «ШШ, отличающийся тем, что, с целью увеличения диапазона измерений при квазипериодических входных сигналах, он содержит блок определения величины рассогласования, состоящий из триггера, выходы которого через дифференцирующие цепочки соединены с единичным и нулевым входами двух других триггеров, единичными входами соединенных с двумя

схемами совпадения, а также схемы «ИЛИ, входы которой подключены к выходам схем совпадения, а выход - к счетному входу первого триггера, и блок определения нулевого рассогласования, состоящий из схемы совпадения, входы которой соединены с входными шинами, а выход - с пороговым элементом, выход которого через схему задержки и схему «ИЛИ соединен с щиной установки устройства в исходное состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРИМИНАТОР | 1972 |

|

SU356769A1 |

| ВРЕМЕННОЙ ДИСКРИМИНАТОР | 1971 |

|

SU297002A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1971 |

|

SU320942A1 |

| ПАТЕНТНО-И.К;:-'- !^,БЧБЛИО ТКА | 1972 |

|

SU326573A1 |

| Преобразователь цифрового кода в синусоидальное напряжение для следящих систем | 1960 |

|

SU134305A1 |

| Устройство для воспроизведения с носителя магнитной записи фазо-модулированного сигнала | 1977 |

|

SU669384A1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФАЗЬ[ С ДИСКРЕТНЫМ | 1971 |

|

SU294264A1 |

| Двухотсчетный преобразователь кода в угол | 1975 |

|

SU549826A1 |

Даты

1970-01-01—Публикация