Јь к

Изобретение относится к цифровым системам автоматического управления и обработки информация и может быть использовано в радиолокационных и радионавигационных системах, в частности в цифровых генераторах опорных сигналов систем автосопровождения объектов по дальности.

Цель изобретения - повышение точ ности преобразования.

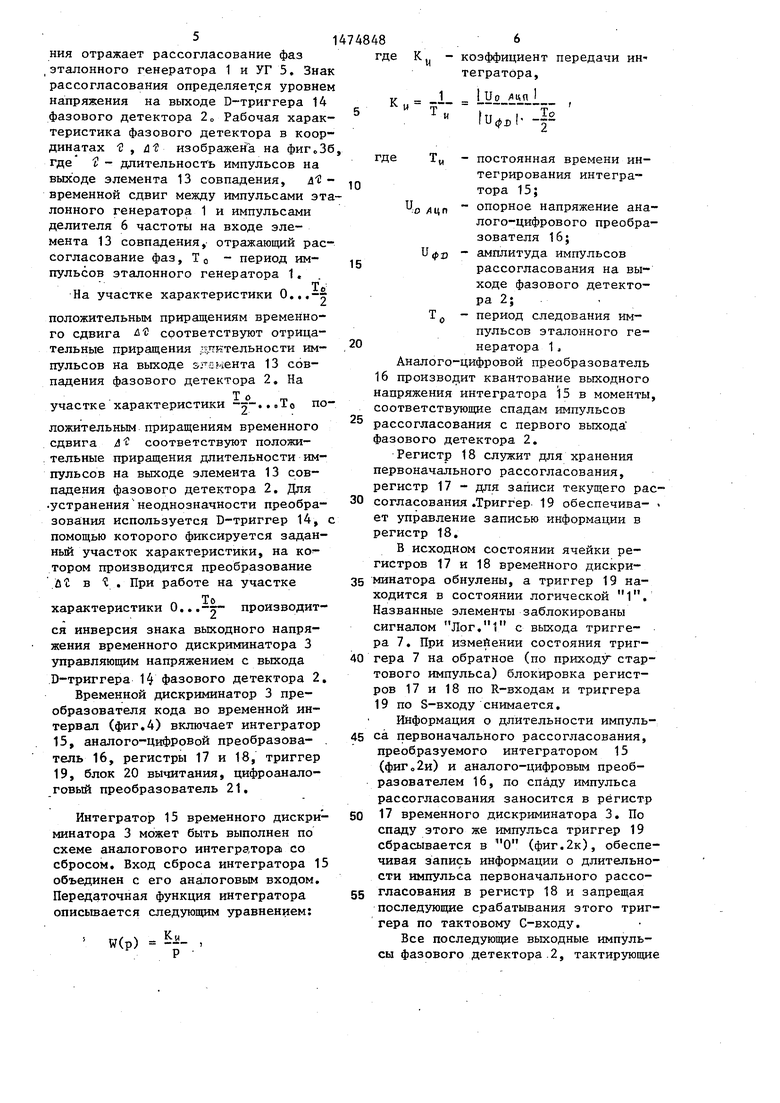

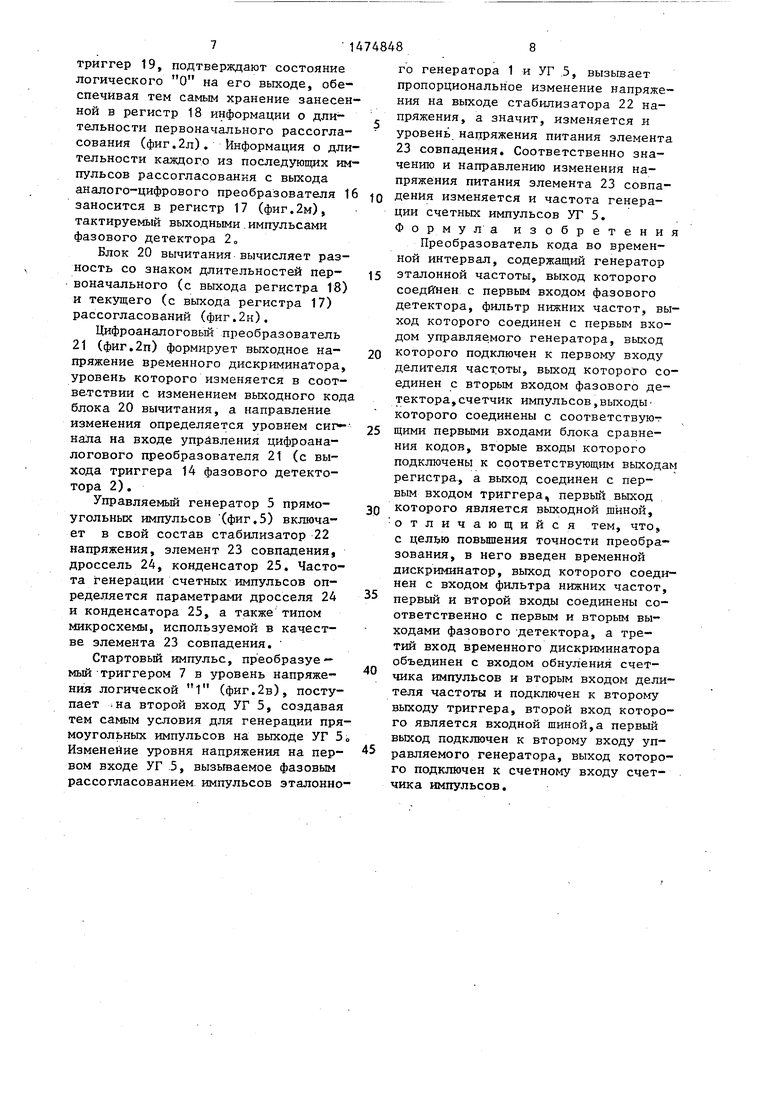

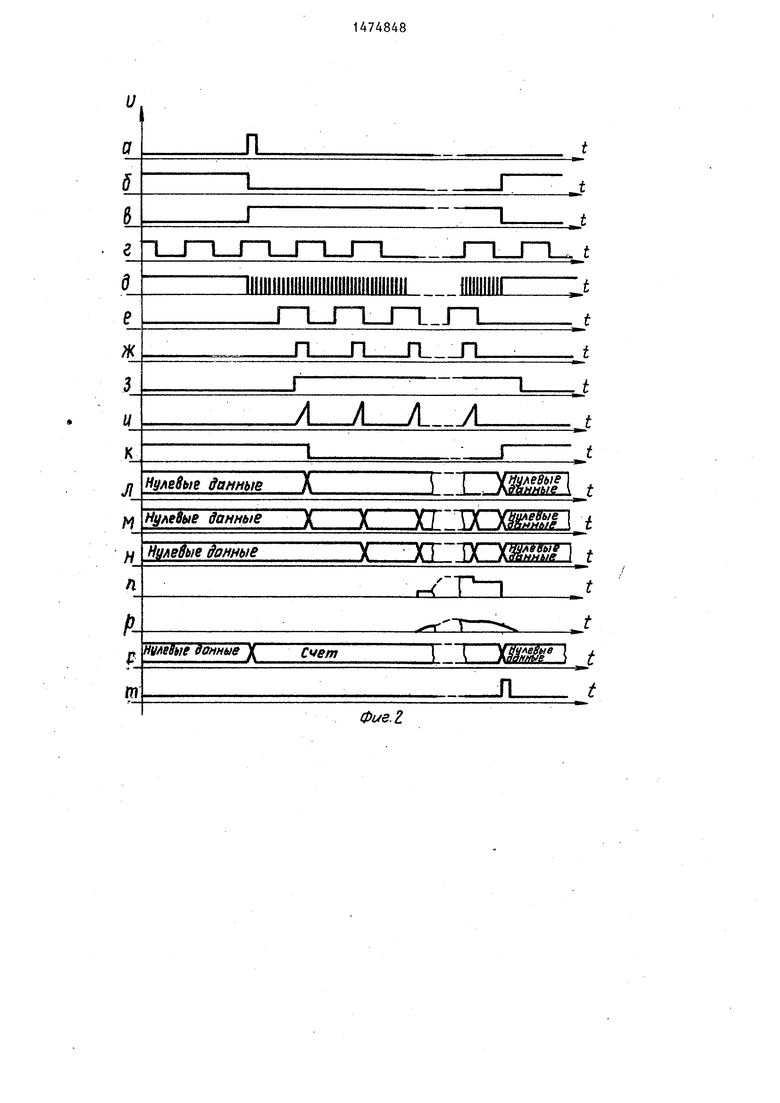

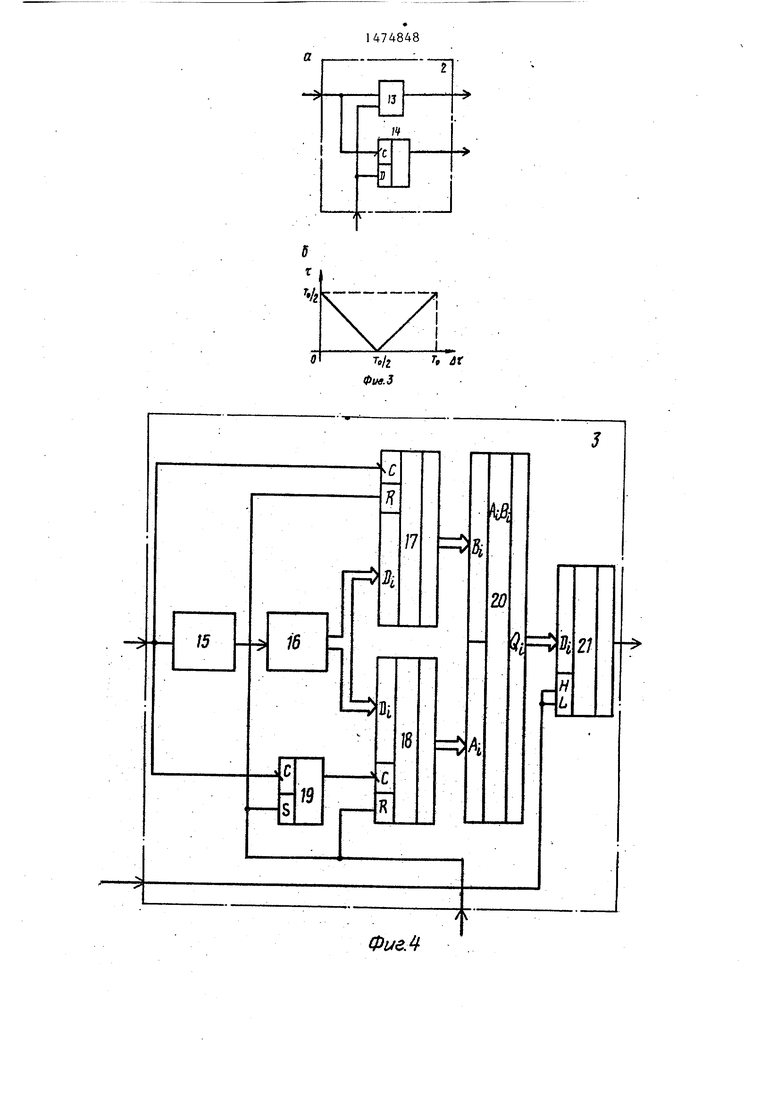

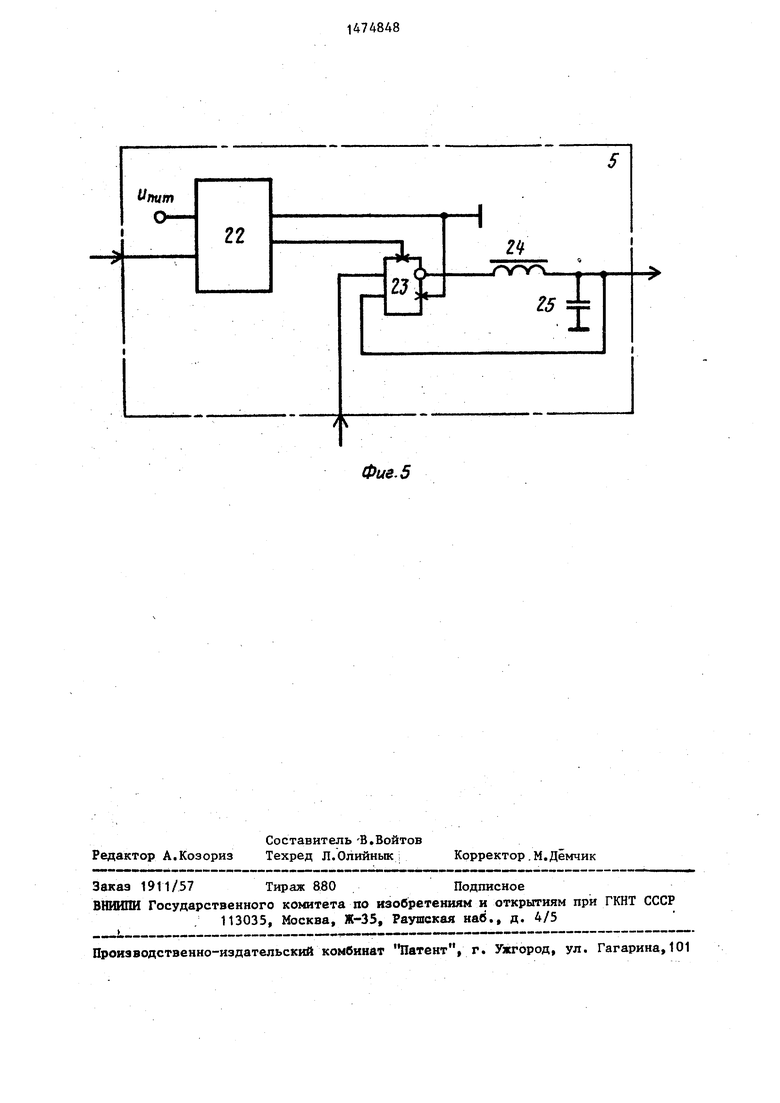

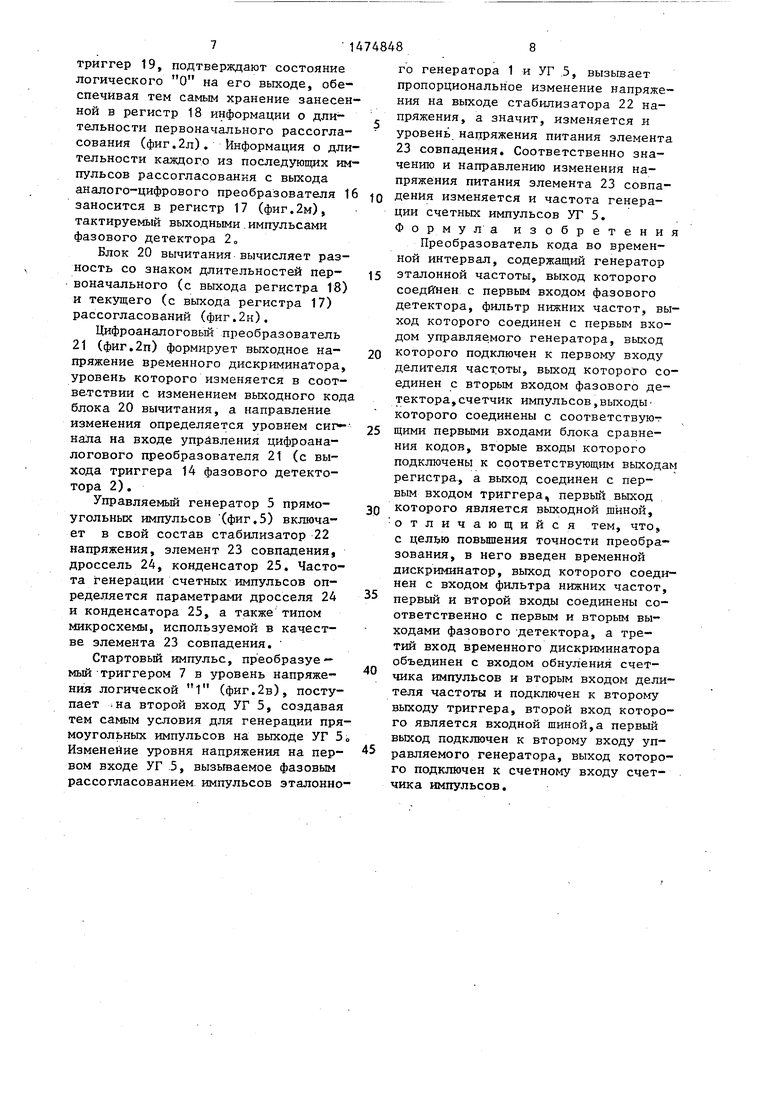

На фиг.1 изображена функциональная схема преобразователя кода во временной интервал; на фиг.2 - временные диаграммы его работы; на фиг.З - функциональная схема фазово- го детектора и график его рабочей характеристики; на фиг.4 - функциональная схема временного дискриминатора; на фиг.З - функциональная схема управляемого генератора.

Преобразователь шда во временной интервал содержит генератор 1 эталонной частоты, фазовый детектор 2, временной дискриминатор 3, фильтр 4 нижних частот, управляемый генера- тор (УГ) 5, делитель 6 частоты, триггер 7, счетчик 8 импульсов, блок 9 сравнения кодов, регистр I0f входную 11 и выходную 12 шины, ,

Преобразователь кода во времен- ной интервал работает следующим образом.

Исходное состояние преобразователя кода во временной интервал определяется выходным напряжением триггера 7, уровень логической 1 с инверсного выхода которого (фиг.26) поддерживает нулевые данные на выходе делителя 6 частоты (фиг.2е), временного дискриминатора 3 (фиг.2п), счетчика 8 импульсов (фиг.2с), блокируя работу перечисленных блоков, а уровень логического О с прямого выхода триггера 7 (фиг.2в) блокирует работу УГ 5 (фиг.2д). Момент начала преобразовав ния кода во временной интервал соответствует моменту прихода стартового импульса, поступающего на входную шину 11 (фиг.2а), а момент окон- чания преобразования (момент формирования выходного импульса схемы 9 сравнения) (фиг.2т) задается величиной кода, поступающего на входы блока 9 сравнения кодов из задатчика кода - регистра 10.

Стартовый импульс изменяет состояния выходов триггера 7 на про- тивоположные, снимая блокировку с

делителя 6 частоты, временного дискриминатора 3,счетчика 8 импульсов, и запускает УГ 5.

Импульсы УГ 5 (фиг.2д) заполняют счетчик 8 импульсов,поступая на его счетный вход (фиг.2с). В то же время система ФАПЧ, состоящая из делителя 6 частоты, фазового детектора 2, временного дискриминатора 3, фильтра 4 нижних частот, УГ 5, поддерживает постоянными величину и знак рассогласования фазы импульсов эталонного генератора 1 и фазы импульсов УГ 5.

Фаза импульсов УГ 5 отражается временным положением импульсов,снимаемых с выхода делителя 6 частоты, фаза импульсов эталонного генератора 1 - временным положением его выходных импульсов.

Фазовый детектор 2, сравнивая временное положение импульсов эталонного генератора 1 (фиг.2г) и временное положение импульсов с выхода делителя 6 частоты (фиг.2е), формирует на первом выходе импульсы, длительность которых пропорциональч на времени совпадения сравниваемых входных импульсов (фиг.2ж).

Возникающее под действием различных факторов (например, климатических) фазовое рассогласование импульсов эталонного генератора 1 и УГ 5 пропорционально изменяет длительности импульсов на первом выходе фазового детектора 2, т.е. отражает величину фазового рассогла- сования, отрабатываемого ФАПЧ. Поэтому формируемые на первом выходе фазового детектора 2 импульсы условно названы импульсами рассогласования. Знак рассогласования определяется уровнем напряжения на втором выходе фазового детектора 2 (фиг.2з). Случаю опережения импульсами делителя 6 частоты импульсов эталонного генератора 1 соответству . ет уровень логической 1, а случаю отставания импульсов делителя 6 частоты от импульсов эталонного генератора - уровень логического О на втором выходе фазового детектора 2. Термин опережение употребляется для случая, когда фронты импульсов эталонного генератора 1 совпадают с импульсами уровня логической 1 на выходе делителя 6 частоты, термин отставание - когда фронты импульсов эталонного генератора 1 совпадают с импульсами уровня логического О на выходе делителя 6 частоты.

Информация о длительности первого из выходных импульсов фазового детектора 2 (первоначальное рассогласование) хранится в памяти временного дискриминатора 3. Длительность каждого из последующих импуль- сов с первого выхода фазового детектора 2 сравнивается во временном дискриминаторе 3 с первоначальным рассогласованием.

Пропорционально разности длитель- ности первого и текущего импульсов и в соответствии со знаком рассогласования изменяется уровень напряжения на выходе временного дискриминатора 3 (фиг.2п):

ивь..вд к м -4-г.(-1)2,

АЪ „ - Of

де

„ 25

длительность импульсов первоначального рассогласования;

Јt - длительность импульса текущего рассогласования; ,п К Вд - коэфициент передачи временного дискриминатора; Z - показатель степени, соответствующий знаку рассогласования (принимает значение О или 1).

35

Соответственно изменению уровня напряжения на выходе временного дискриминатора 3 изменяется уровень напряжения на выходе фильтра 4 нижних частот (входное напряжение УГ 5) (фиг.2р)

45

50

иф(р)-ъ u6A (t)3J,

выходное напряжение

фильтра 4 нижних частот; передаточная функция фильтра 4 нижних частот;

изображение по Лапласу выходного напряжения временного дискриминатора;операция обратного 55

преобразования Лапласа, зменяются частоты ге- ьсов УГ 5, приближая

текущее временное рассогласование импульсов на первом и втором входах фазового детектора 2 к первоначальному:

fvr(t) f

О 1Г

+ КоГ lUCt),

Q

5 0

5

п

5

5

0

5

где К vr - коэффициент передачи

УГ 5;

U(t) - выходное напряжение фильтра 4 нижних частот; f о УГ частота генерации импульсов УГ 5, соответствующая нулевому напряжению на его входе. В момент равенства значений выходного кода счетчика 8 импульсов и входного преобразуемого кода, хранящегося в регистре 10, блок 9 сравнения кодов вырабатывает выходной импульс (фиг.2т), который устанавливает в исходное состояние триггер 7, блокируя тем самым работу преобразователя кода во временной интервал до прихода очередного стартового импульса и формируя на выходной шине 12 сигнал окончания временного интервала.

Таким образом, преобразователь кода во временной интервал обеспечивает повышение точности преобразования кода во временной интервал за счет ликвидации погрешностей преобразования, вызванных во-первых, нестабильностью частоты импульсов управляемого генератора, заполняющих преобразуемый временной интервал между импульсами запуска и окончания преобразователя, во-вторых, отсутствием синхронизации стартового импульса и момента запуска управляемого генератора Точность преобразования кода во временной интервал определяется стабильностью частоты эталонного генератора 1„

Один из вариантов технической реализации входящих блоков преобразователя кода во временной интервал показан на фиг.З. Фазовый детектор 2 (фиг.За) включает элемент 13 совпадения и D-триггер 14, при этом первый вход фазового детектора 2 является первым входом элемента 13 совпадения, а второй вход фазовогй детектора 2 - вторым входом элемента 13 совпадения. Длительность выходных импульсов элемента 13 совпадеия отражает рассогласование фаз талонного генератора 1 и УГ 5. Знак ассогласования определяемся уровнем апряжения на выходе D-триггера 14 азового детектора 2„ Рабочая харакеристика фазового детектора в кооринатах И , АИ изображена на фиг„3б, де 1 - длительность импульсов на ыходе элемента 13 совпадения, д - ременной сдвиг между импульсами этаонного генератора 1 и импульсами елителя 6 частоты на входе элеента 13 совпадения, отражающий расогласование фаз, Т о - период имульсов эталонного генератора 1«

Т На участке характеристики О...-r

оложительным приращениям временноо сдвига ДФ соответствуют отрицаельные приращения нтельности импульсов на выходе з кента 13 совпадения фазового детектора 2. На

гр

участке характеристики ..вТ0 поожительным приращениям временного сдвига иЪ соответствуют положительные приращения длительности импульсов на выходе элемента 13 совпадения фазового детектора 2. Для устранения неоднозначности преобразования используется D-триггер 14, с помощью которого фиксируется заданный участок характеристики, на котором производится преобразование дЈ в . При работе на участке

Тл

характеристики О...-j- производится инверсия знака выходного напряжения временного дискриминатора 3 управляющим напряжением с выхода D-триггера 14 фазового детектора 2.

Временной дискриминатор 3 преобразователя кода во временной интервал (фиг.4) включает интегратор 15, аналого-цифровой преобразователь 16, регистры 17 и 18, триггер 19, блок 20 вычитания, цифроанало- говый преобразователь 21.

Интегратор 15 временного дискриминатора 3 может быть выполнен по схеме аналогового интегратора со сбросом. Вход сброса интегратора 15 объединен с его аналоговым входом. Передаточная функция интегратора описьюается следующим уравнением:

1474848 где

10

15

20

25

30

40

50

K

где

16 п напр соот расс фазо

перв реги согл ет у реги

гист 35 мина ходи Назв сигн ра 7 гера тово ров 19 п

са п пре (фи раз рас 17 спа сбр чив сти гла пос гер

45

55

W(p)

Ј« Р

коэффициент передачи интегратора,

I Ti I То lUtf-Dt

5

0

5

0

0

0

где

U

О АЦП

U

срО

тл постоянная времени интегрирования интегратора 15;

опорное напряжение аналого-цифрового преобразователя 16; амплитуда импульсов рассогласования на выходе фазового детектора 2;

период следования импульсов эталонного генератора 1,

Аналого-цифровой преобразователь 16 производит квантование выходного напряжения интегратора 15 в моменты, соответствующие спадам импульсов рассогласования с первого выхода фазового детектора 2.

Регистр 18 служит для хранения первоначального рассогласования, регистр 17 - для записи текущего рассогласования .Триггер 19 обеспечива- . ет управление записью информации в регистр 18.

В исходном состоянии ячейки регистров 17 и 18 временного дискри- 5 минатора обнулены, а триггер 19 находится в состоянии логической 1. Названные элементы заблокированы сигналом Лог.1 с выхода триггера 7. При измейении состояния триггера 7 на обратное (по приходу стартового импульса) блокировка регистров 17 и 18 по R-входам и триггера 19 по S-входу снимается.

Информация о длительности импульса первоначального рассогласования, преобразуемого интегратором 15 (фиг02и) и аналого-цифровым преобразователем 16, по спаду импульса рассогласования заносится в регистр 17 временного дискриминатора 3. По спаду этого же импульса триггер 19 сбрасывается в О (фиг.2к), обеспечивая запись информации о длительности импульса первоначального рассогласования в регистр 18 и запрещая последующие срабатывания этого триггера по тактовому С-входу.

Все последующие выходные импульсы фазового детектора 2, тактирующие

5

5

71

триггер 19, подтверждают состояние логического О на его выходе, обеспечивая тем самым хранение занесенной в регистр 18 информации о длительности первоначального рассогласования (фиг.2л). Информация о длительности каждого из последующих импульсов рассогласования с выхода аналого-цифрового преобразователя 1 заносится в регистр 17 (фиг.2м), тактируемый выходными импульсами фазового детектора 2„

Блок 20 вычитания вычисляет разность со знаком длительностей первоначального (с выхода регистра 18) и текущего (с выхода регистра 17) рассогласований (фиг.2н).

Цифроаналоговый преобразователь 21 (фиг.2п) формирует выходное напряжение временного дискриминатора, уровень которого изменяется в соответствии с изменением выходного код блока 20 вычитания, а направление изменения определяется уровнем нала на входе управления цифроана- логового преобразователя 21 (с выхода триггера 14 фазового детекто- тора 2).

Управляемый генератор 5 прямоугольных импульсов (фиг.5) включает в свой состав стабилизатор 22 напряжения, элемент 23 совпадения, дроссель 24, конденсатор 25. Частота генерации счетных импульсов определяется параметрами дросселя 24 и конденсатора 25, а также типом микросхемы, используемой в качестве элемента 23 совпадения.

Стартовый импульс, преобразуемый триггером 7 в уровень напряже

ния логической 1 (фиг.2в), поступает на второй вход УГ 5, создавая тем самым условия для генерации прямоугольных импульсов на выходе УГ 50 Изменение уровня напряжения на первом входе УГ 5, вызываемое фазовым рассогласованием импульсов эталонно8

0

0

5

0

5

0

5

го генератора 1 и УГ 5, вызывает пропорциональное изменение напряжения на выходе стабилизатора 22 напряжения, а значит, изменяется и уровень напряжения питания элемента 23 совпадения. Соответственно значению и направлению изменения напряжения питания элемента 23 совпадения изменяется и частота генерации счетных импульсов УГ 5. Формула изобретения

Преобразователь кода во временной интервал, содержащий генератор эталонной частоты, выход которого соединен с первым входом фазового детектора, фильтр нижних частот, выход которого соединен с первым входом управляемого генератора, выход которого подключен к первому входу делителя частоты, выход которого соединен с вторым входом фазового детектора, счетчик импульсов,выходы которого соединены с соответствующими первыми входами блока сравнения кодов, вторые входы которого подключены к соответствующим выходам регистра, а выход соединен с первым входом триггера, первый выход которого является выходной шиной, отличающийся тем, что, с целью повышения точности преобразования, в него введен временной дискриминатор, выход которого соединен с входом фильтра нижних частот, первый и второй входы соединены соответственно с первым и вторым выходами фазового детектора, а третий вход временного дискриминатора объединен с входом обнуления счетчика импульсов и вторым входом делителя частоты и подключен к второму выходу триггера, второй вход которого является входной шиной,а первый выход подключен к второму входу управляемого генератора, выход которого подключен к счетному входу счетчика импульсов.

Bi

s а

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Преобразователь кода во временной интервал | 1984 |

|

SU1229961A1 |

| Цифровой магнитовариационный преобразователь | 1978 |

|

SU802893A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU767965A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Преобразователь кода во временной интервал | 1986 |

|

SU1410279A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Устройство для фазового управления тиристорным преобразователем | 1982 |

|

SU1086545A1 |

Изобретение относится к цифровым системам автоматического управления и обработки информации. Цель изобретения - повышение точности преобразования за счет устранения временной задержки начала преобразования относительно момента поступления тактового импульса. Преобразователь содержит генератор эталонной частоты 1,фазовый детектор 2, временной дискриминатор 3, фильтр нижних частот 4, управляемый генератор 5, делитель частоты 6, триггер 7, счетчик импульсов 8, блок сравнения кодов 9, регистр 10. Поставленная цель достигается применением управляемого генератора, запускаемого стартовым импульсом, со стабилизацией частоты генерации. Преобразователь формирует прецизионный временной интервал, пропорциональный входному коду и начинающийся в момент прихода стартового импульса. 5 ил.

7 н

ч

ог

ДГ «

Г

л

/

h i

s

Фиг. 5

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М.: Энергия, 1975, с.268, рис.6-9 | |||

| Преобразователь кода во временной интервал | 1984 |

|

SU1229961A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача