,1

Изобретение относится к области цифровой вычислительной техники и может быть применено в цифровой вычислительной машине.

Известны устройства для суммирования нескольких чисел, представленных двоично-десятичным кодом, содержащие цифро-аналоговые преобразователи, операционные усилители и аналого-цифровые преобразователи.

Предлагаемое устройство отличается тем, что в нем разряды построены из трех групповых блоков, два из которых идентичны. Выход цифро-аналогового преобразователя первого группового блока соединен со входом операционного усилителя этого же блока, к которому присоединен выход устройства передачи переполнения этого же блока, выход устройства передачи переполнения аналогичного блока соседнего младшего разряда. Выход операционного усилителя соединен с первым входом операционного усилителя третьего группового блока данного разряда и со входом логической схемы первого группового блока, первый выход которой соединен со входом устройства передачи переполнения данного группового разряда, второй выход соединен с соответствующим входом общей логической схемы устройства, а третий выход логической схемы группового блока соединен со входом аналогичной схемы соседнего старшего разряда. Выход операционного усилителя третьего

группового блока соединен со входом аналогоцифрового преобразователя и со входом логической схемы третьего группового блока, первый выход которой соединен со входом идентичной логической схемы соседнего старшего разряда, а второй выход соединен с первым входом устройства передачи переполнения третьего группового блока, второй вход которого соединен с соответствующим выходом

общей логической схемы устройства. Выход

устройства передачи переполнения соединен

со входом операционного усилителя третьего

.группового блока.

Другим отличием предложенного устройства является то, что в нем логическая схема каждого k-TO группового блока снабжена двумя нуль-органами, подключенными к выходу операционного усилителя, выход первого нульоргана соединен с первыми входами схем совпадения логической схемы соседнего младшего разряда, вторыми входами п-1 схем совпадения логической схемы данного разряда и соединен с третьим входом первой схемы совпадения соседнего старшего разряда. Выход

второго нуль-органа соединен с первым входом первой собирательной схемы данного разряда и со вторыми входами k-ых схем совпадения всех старших разрядов. Выходы схем совпадения k-ro разряда соединены со входасхемы k-ro разряда, выход которой соединен со вторым входом первой собирательной схемы логической схемы соседнего старшего разряда. Выход первой собирательной схемы логической схемы k-ro разряда соединен со входом узла передачи переполнения k-ro разряда.

Это позволяет увеличить число одновременно складываемых чисел и повысить быстродействие.

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема цифро-аналогового преобразователя (ЦАП); на фиг. 3 - схема одного из преобразователей ЦАП; на фиг. 4 - логические схемы для передачи переполнения и их взаимосвязи; на фиг. 5 - схема логического блока; на фиг. 6- схема блока управления; на фиг. 7 и 8 - схемы узлов передачи переполнения; на фиг. 9- блок-схема аналого-цифрового преобразователя.

Устройство работает следующим образом.

Для суммирования требуемого количества т слагаемых, представляющих собой многоразрядные двоичные числа, цифры этих чисел представляют в двоично-десятичном счислении тетрадами.

Предварительно на шину У„с «Установка начального состояния подают сигнал, который производит установку всех триггеров в начальное состояние. После этого подают сигнал пуска на клемму пуска Я блока управления БУ.

Пусковой импульс перебрасывают триггер пуска Тп, который дает разрешение на прохождение импульсов через вентили В в узлы передачи переполнения УП и УПг.

Все тетрады в отдельности разбивают поразрядно на несколько равных групп (в нащем примере на две) и задают для суммирования на вход операционного усилителя У соответствующих групповых блоков fpi и Гр2 ЦАП соответствующего блока разряда Бр, Бр J, Брс,. . ; Бр„, .

Слагаемые можно выбирать, например, с запоминающего устройства как последовательно, так и параллельно. Записанное число каждой тетрады преобразуется с помощью ЦАП в аналоговое напряжение.

Для разбора условно примем, что код «1 соответствует отрицательному напряжению с выхода левого плеча триггера, а код «О - напряжению близкого к нулю того же плеча триггера. Так как все ключи разрядов ведут себя одинаково, то рассматривается работа одного из них (например, первого разряда).

Пусть на триггере этого разряда записан «О, т. е. на выходе левого плеча триггера - нулевой уровень. В этом случае от источника + - (см. фиг. 3) через резистор Rs и диод DI в точке а получается положительное смещение, запирающее диод Dz и обеспечивающее запрет напряжению -Е через резистор Кз и диод Da на вход усилителя. Это условие создается путем выбора соотношений резисторов RI и Rs при заданной величине резистора Rs

и напряжения - Е, -}- Е и выходного напряжения триггера.

При записи на триггере «1 на выходе левого плеча образуется отрицательный уровень напряжения, в средней точке делителя преобладает отрицательное напряжение, которое закрывает диод DI, так как на катоде диода DS напряжение близко к нулю. Поэтому напряжение - Е поступает на вход усилителя

без погрешности через резистор Rs и диод Dz. Так как проводимости резисторов Ra, Ra, Rs, Rz разрядов представляют степени двойки, и сопротивление обратной связи резистора по величине равно сопротивлению резистора R первого разряда, то записанное двоичное число от 1 до 9 на тетраде будет пропорционально выходному напряжению операционного усилителя. Например, в случае применения усилителя с рабочим диапазоном ± 100

цифрам 1, 2, 3,..., 9 будут соответствовать аналоги напряжения 10, 20, 30,..., 90.

По группам разбитых тетрад через преобразователи подводятся отрицательные напряжения-аналоги записанных чисел ко входу

усилителя для их суммирования.

Первая часть после преобразования суммируется в групповом блоке Гр, другая часть- в групповом блоке Гр. Рассмотрим работу одного группового блока, например блока Гр

(блоки Гр,а, Гр1Ь, Гр1с,. .., Гр1п, fpln+l)

После преобразования и суммирования на выходе каждого усилителя У/а, У/б, У/, и У /л каждого разряда могут возникнуть следующие случаи

или , или 2t/ Ад, или 2t/ Л10,

где Ef/ - суммарное выходное напряжение

любого операционного усилителя; Ло - напряжение-аналог девяти; Лю - напряжение-аналог десяти.

Как указывалось выше, к выходу каждого усилителя подключены по два нуль-органа OQ и (1о. На первом разрешающий признак осуществления логических операций возникает при условии , на втором - при 26/ 4io.

При образовании на выходе усилителя любого разряда суммарного напряжения EU Лю соответствующий нуль-орган OK, через схему сравнения ИЛИ дает разрешение узлу переполнения УЯ задать на вход его операционного усилителя компенсирующее напряжение-аналог десяти, а на входе операционного усилителя следующего разряда - напряжение-аналог единицы того же знака, что и знак суммы.

Эта операция повторяется неоднократно до тех пор, пока на выходе усилителя не исчезнет признак переполнения, т. е. когда не установится условие Sf/ ; Ло. Узлы переполнения работают следующим

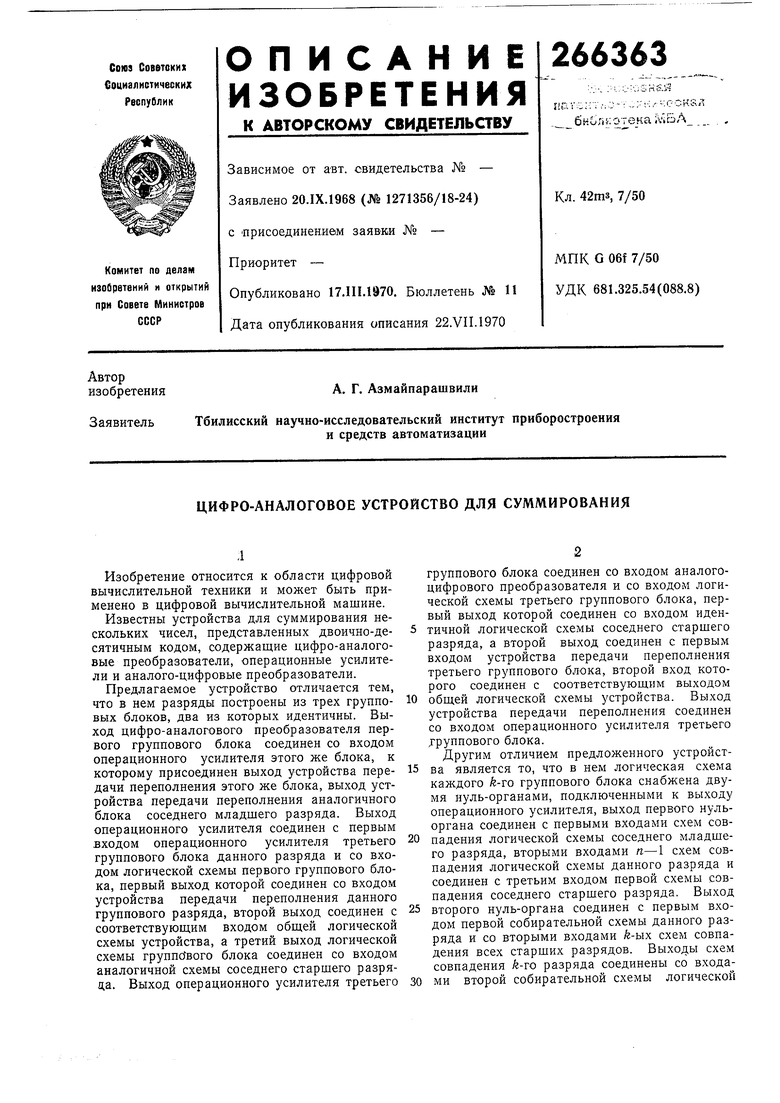

В начале работы (как это указывалось выше), после того как поданы (записаны) слагаемые, на шину УНС задают импульс установки начального состояния, и все триггеры устройства будут установлены в начальное состояние.

На фиг. 7 триггеры изображены в начальном состоянии. В этом случае ключи получают запрет от всех триггеров. При выходном напряжении (см. фиг. 7) левого плеча любого триггера, например триггер Г/, близкого к нулю, от источника + Е через диод Dj в точке а создается положительное смещение, запирающее диод Dj: и обеспечивающее отрицательному напряжению-аналогу единицы ,. Это условие создается путем выбора соотношения сопротивлений резисторов Rt и Re при заданных величинах напряжения , -IJA и сопротивления резистора R.

С другой стороны, с выхода правого плеча того же триггера создается отрицательное смещение, запирающее диод D и обеспечивающее запрет положительному компенсирующему напряжению-аналогу десяти + LA:4io. Это условие создается путем выбора соотношения сопротивлений резисторов 7 и при заданных величинах напряжения + ,-{- и сопротивления резистора R.

При подаче запускающего импульса на клемму пуска Я триггер пуска „ переключается, и через вентиль В„ дается разрешение на прохождение импульсов от генератора ///. Импульсы подаются на все вентили В;,..., S, узлов переполнения групповых блоков Гр и Гр2 и на вентиль Во группового блока (блоки Грза, Грзь, fpac, . . ., Грзп , Грзп+i).

После запуска устройства ключи /d и К. остаются в неизменном состоянии в тех узлах передачи переполнения, где на их входы не заданы разрешающие сигналы.

Если на вход узлов переполнения групповых блоков Г/З и Fpz задается разрешающий сигнал, то через вентиль БС импульсы поступают на все вентили В-, ,. .., Вр.

Первый импульс перебрасывает триггер Т, который, в свою очередь, переключает ключ К.1 и K.Z, а последние задают на вход операционного усилителя (усилители У/а, У/б ,У/с,. .., У In , у компенсирующее напряжение-аналог десяти , и на вход операционного усилителя следующего разряда напряжениеаналог единицы - ИА.

Происходит это следующим образом: отрицательное напряжение с выхода левого плеча триггера запирает диод DZ, так как на катоде открытого диода D напряжение близко к нулю. Поэтому отрицательное напряжение-аналог единицы -UA без погрешности через резистор 5 и диод D поступает на вход усилителя следующего разряда. Так как в этом случае с выхода правого плеча поступает напряжение, близкое к нулю, то напряжением от положительного источника -f Е аналогичным образом запирается диод и положительное напряжение-аналог десяти -f через

резистор RS, и диод D поступает на вход усилителя данного разряда.

Если после первой компенсации напряжение на выходе усилителя снова превышает напря5 жение-аналог десяти, т. е. SL; UA, то указанный процесс повторяется с помощью второго импульса, который перебрасывает триггер Г2, так как с выхода правого плеча триггера TI на потенциальный вход вентиля BZ (на 0 фигурах не показан) подается уже нулевой (разрешающий) потенциал.

Процесс повторяется до тех пор, пока напряжение на выходе усилителя не станет

2f/ С/Лд.

5 После каждого переброса триггеры остаются до конца цикла в неизменном состоянии.

Узел переполнения группового блока (блоки Грза, Грзь, Грзс,..., Грзп, Грзп+/)работает следующим образом.

0 На вход усилителя любого разряда этого группового блока поступают напряжения с групповых блоков Гр1 и Гр-2, максимальная величина которых при любом возможном числе слагаемых в первой и второй группах после передачи переполнения не превышает удвоенной величины напряжения-аналога девяти, т. е.

иАэ -f t/Л9 WA.

0 Следовательно, число слагаемых, суммируемых на входе усилителя группового блока

(блоки Грза, Грзь, Грзе,..., ГрЗаГрзп-l) ЛЮбого разряда, равно двум. В переходном периоде, когда на выходе любого нуль-органа первого или второго групповых блоков имеется признак переполнения, тогда во все узлы переполнения третьего группового блока задается запрет передачи переполнения. После исчезновения признака переполнения в групповых блоках JTpi и Гр поступает разрешение на передачу переполнения в третий групповой блок.

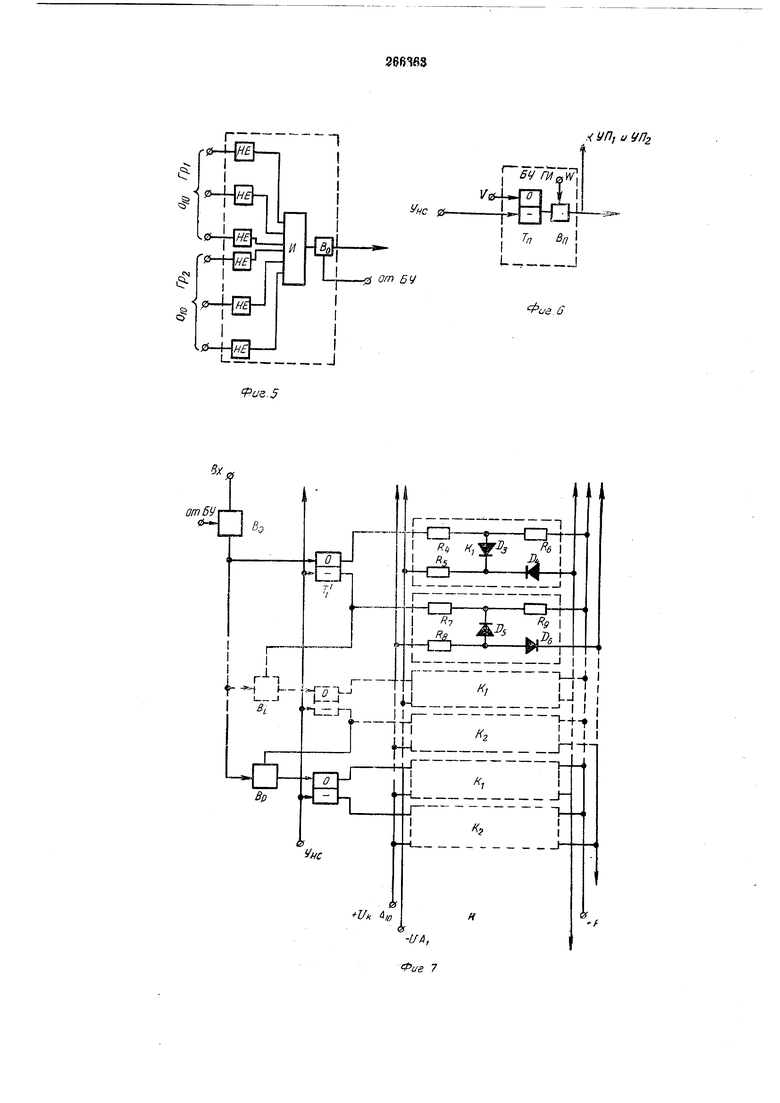

Для осуществления такой логической операции (см. фиг. 5) с выхода каждого нуль-ор5 гана (1о групповых блоков Гр и Гра всех блоков разрядов подаются напряжения на схемы НЕ, а с выходов последних подаются на выходы схемы Я, с выхода которой напряжение подается на потенциальный вход вентиля BQ,

0 служащего для управления переполнения третьего группового блока. Совпадение на схеме И происходит при исчезнове,нии признаков переполнения на нуль-органах Ою во всех блоках разрядов групповых блоков fpi и Грг5 При совпадении вентиль BO дает разрешение на прохождение импульсов к узлам переполнения всех разрядов третьего группового блока. Передача переполнения в каждом разряде происходит только в том случае, если на пос0 леднем будет признак переполнения. Несовпадение на схеме И происходит при наличии признака переполнения хотя бы на одном нуль-органе 0 группы блоков Гр1 или Гр. Все это происходит параллельно во всех

блоке разряда, начиная со второго блока наступает и после передачи напряжения-аналога единицы (т. е. переполнения) с предыдущего блока разряда, если па выходе данного операционного усилителя суммарное напряжение равно напряжению-аналогу девяти, т. е. Ef/ UAt. То же самое может произойти с третьим блоком разряда и т. д.

Схемы логики учитывают вышеуказанные и другие всевозможные комбинации выходных напряжений операционных усилителей путем .преждевременного определения состояния признаков с помощью нуль-органов Од и (9io во всех блоках разрядов. Указанные нуль-органы воздействуют на схему логики Л, чем обеспечивается параллельная передача переполнения в любых случаях выходных напряжений усилителей во всех блоках разрядов.

С целью преждевременной передачи переполнения в последующие блоки разрядов, где переполнение пока еще не наступило, но может наступить после передачи напряженияаналога единицы с операционного усилителя предыдущего разряда, т. е. когда на выходе данного разряда накоплено напряжение-аналог девяти (Ef/ и Ад) каждый блок разряда снабжен, как упоминалось выще, соответствующим количеством логических элементов, которые действуют следующим образом.

Схема совпадения Я/а реагирует на совпадение двух признаков выходного напряжения усилителей: на напряжение большего и равного аналогу десяти и на напряжение больщего или равного аналогу девяти ( и на ), когда на выходах нуль-органов и Од имеется код «1.

При совпадении на схеме Mia дается разрешение через схему ИЛИгь (следующего разряда) произвести передачу переполнения. Одновременно нуль-орган Сю логической схемы Л1а дает разрешение произвести передачу переполнения с помощью узла передачи перемещения УЯ/о.

Схема совпадения Я/г. логической схемы Лц, реагриет на совпадение следующих признаков:

от нуль-органа Ою логической схемы Л/о,

от нуль-органа 0 логической схемы /7/,

Ef/ Лд от нуль-органа 0 логической схемы Л 1с .

Схема совпадения реагирует на совпадение признаков:

EL(.5 Л10 от нуль-органа От логической схемы Л It,,

ли с Ад от нуль-органа Од логической схемы Л 1с .

При совпадении указанных признаков в одной схеме совпадения Я/б или в другой схеме совпадения И2ь через схему в схему ЯЛЯ/с подается разрешение узлу передачи переполнения УЯус произвести передачу переполнения. Одновременно нуль-орган Ощ логической схемы Л/й, если па нем имеется признак

, подает разрешение через другой вход схемы ЯЛЯ/i произвести передачу переполнения на узел передачи переполнения УЯ/б.

Схема совпадения Я/е логической схемы Л/с реагирует на совпадение следующих признаков:

Еба 22 Л10 от нуль-органа 0 логической схемы Л/а ,

Et/j Лв от нуль-органа 0 логической схемы Ли, ,

I,Uff Ад от нуль-органа 0 логической схемы Л/с ,

от нуль-органа 0 логической схемы Л/я .

Схема совпадения И2с реагирует на совпадение признаков:

от нуль-органа 0 логической схемы Ли,,

Ei/f 5 Л от нуль-органа 0 логической схемы Л 1с ,

от нуль-органа Од логической схемы Л/л.

Схема совпадения Hsc реагирует на совпадение признаков:

от нуль-органа логической схемы Л/, ,

Ef/я Лэ от нуль-органа 0 логической схемы Л/л .

При совпадении признаков в одной из трех схем совпадения через схемы и ЯЛЯ/л подается разрешение узлу переполнения УЯ1 произвести передачу переполнения.

Одновременно, если на нуль-органе (io логической схемы Л/ имеется признак Лю, то подается разрешение на передачу переполнения с узла переполнения УЯ/ .

Если число блоков разряда равно количеству разрядов п слагаемых чисел, то переполпение с этого блока разряда накапливается на блоке Бра+i,

Блок Бр„ не содержит схем совпадения Я. При появлении признака нуль-орган через схему ЯЛЯ/л дает разрещение на передачу переполнения УЯ/л данного разряда.

Таким образом, при любых всевозможных состояниях выходных напряжений операционных усилителей всех разрядов, а следовательно, и признаков нуль-органов Ощ и 0 всех разрядов, передача переполнения осуществляется во всех блоках разряда одновременно (параллельно). На выходе операционного усилителя каждого разряда третьего группового блока после окончания решения появляется результат суммы.

Аналого-цифровой преобразователь каждого разряда, состоящий из девяти ступеней сравнения, работает следующим образом. На вход Вх в преобразователь поступает напряжение-аналог цифры, обра:ювавшееся на выходе операционного усилителя Уза- Если на входе Вх напряжение U равно нулю, то со всех нуль-органов и со всех схем совпадения выдается код «О. В этом случае все диоды дешифратора заперты, ни одна шина не возбуждена и на двоичном выходе Вых 2 появляется тетрада 0000, т. е. цифра О, а на десятичном выходе Вых 10 ни одна шина не возбуждена, что также будет соответствовать цифре 0.

Если на выходе операционного усилителя (усилители Уаа,Узь,Узс,---, накоплено напряжение, например напряжение-аналог семи (Uf Лу), то с выходов нуль-органов (см. фиг. 9) будет выдан код «1, а с

остальных выходов нуль-органов 08 и Оо9 -

код «О. Код «1 со схем совпадения будет выдан только со схемы совпадения И-j, а на всех остальных схемах совпадения окажется несовпадение и будет выдан код «О. Вследствие этого через соответствующие диоды дешифратора Д и на двоичном выходе Вых 2 появляется тетрада 0111, т. е. число 7, а на десятичном выходе Вых 10 возбуждается соответствующая шина и будет выдана цифра 7.

Поразрядно выданные на выходах аналогоцифровых преобразователей цифры представляют в совокупности искомую сумму.

Вследствие того что разность между смежными напряжениями-аналогами цифр довольно значительная, то к элементам устройства не требуется предъявлять особые требования, так как погрешности в предлагаемом устройстве не проявляются.

Предмет изобретения

1. Цифро-аналоговое устройство для суммирования нескольких многоразрядных чисел, представленных двоично-десятичным кодом, содержащее разрядные цифро-аналоговые преобразователи, операционные усилители и аналого-цифровые преобразователи, отличающееся тем, что, с целью увеличения числа одновременно складываемых чисел и повышения быстродействия, в нем разряды построены из трех групповых блоков, два из которых идентичны, причем выход цифро-аналогового преобразователя первого группового блока соединен со входом операционного усилителя этого же блока, к которому присоединен выход устройства передачи переполнения этого же блока, выход устройства передачи переполнения

аналогичного блока соседнего младшего разряда, а выход операционного усилителя соединен с первым входом операционного усилителя третьего группового блока данного разряда и со входом логической схемы первого группового блока, первый выход которой соединен со входом устройства передачи переполнения данного группового разряда, второй выход соединен с соответствующим входом общей логической схемы устройства, а третий выход логической схемы группового блока соединен со входом аналогичной схемы соседнего старшего разряда, выход операционного усилителя третьего группового блока соединен

со входом аналого-цифрового преобразователя и со входом логической схемы третьего группового блока, первый выход которой соединен со входом идентичной логической схемы соседнего старшего разряда, а второй выход соединен с первым входом устройства передачи переполнения третьего группового блока, второй вход которого соединен с соответствующим выходом общей логической схемы устройства, выход устройства передачи переполнения соединен со входом операционного усилителя третьего группового блока.

2. Устройство по п. 1, отличающееся тем, что, с целью повышения быстродействия, в нем логическая схема каждого -го группового

блока снабжена двумя нуль-органами, подключенными к выходу операционного усилителя, выход первого нуль-органа соединен с первыми входами схем совпадения логической схемы соседнего младшего разряда, вторыми

входами п-1 схем совпадения логической схемы данного разряда и соединен с третьим уходом первой схемы совпадения соседнего старшего разряда, выход второго нуль-органа соединен с первым входом первой собирательной схемы данного разряда и со вторыми входами k-ых схем совпадения всех старших разрядов, выходы схем совпадения k-ro разряда соединены со входами второй собирательной схемы логической схемы k-ro разряда, выход которой соединен со вторым входом перрой собирательной схемы логической схемы соседнего старшего разряда, выход первой со.бирательной схемы логической схемы -го разряда соединен со входом узла передачи переполнения -го разряда. ЩЕрЩП -Г-&Н4CiM , L-J I LJi ; , r-fiiii I1 p--, I I J i 0-1-I Pj.-,I Sf nffI

. jip: -Hrfj;:

.

бу

нс i

Тп Bfj

I

(,„

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для измерения импульсных напряжений | 1975 |

|

SU676933A1 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифровой измерительный преобразователь электрической проводимости жидкости | 1987 |

|

SU1531027A1 |

| Счетчик ампер-часов | 1971 |

|

SU506808A1 |

| Устройство для измерения неэлектрических величин | 1987 |

|

SU1490448A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Измеритель времени установления выходного напряжения цифроаналоговых преобразователей | 1984 |

|

SU1236612A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Цифровой измеритель коэффициента передачи четырехполюсника | 1986 |

|

SU1323985A1 |

Даты

1970-01-01—Публикация