г

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1239867A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕГРИРУЮЩЕГО ТИПА ДЛЯ ИЗМЕРЕНИЯ МАЛЫХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2018 |

|

RU2693647C1 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Устройство для управления виброиспытаниями | 1985 |

|

SU1267377A1 |

Изобретение относится к автоматике и измерительной технике и может быть использовано в системах ввода информации в ЭВМ. Изобретение позвс ляет повысить быстродействие. Это достигается тем, что в устройство, содержащее блок 4 управления, цифро- аналоговый преобразователь 20, эле

т Т

Сл

мент ИЛИ 15, а в каждом канале преобразования операционный усилитель 10, компаратор 13 и D-триггер 14, введены параллельный аналого-цифровой преобразователь 17, компаратор 18, счетчик 19 импульсов, элемент 16 задержки, токоограничивающий элемент

1

; Изобретение относится к автоматике in .измерительной технике и может быть использовано в подсистемах ввода информации в ЭВМ о ходе технологическо - го процесса, например процесса испы-, таний изделий на механические вибра- 1щонные воздействия.

Цель изобретения - повышение быстродействия. . ,

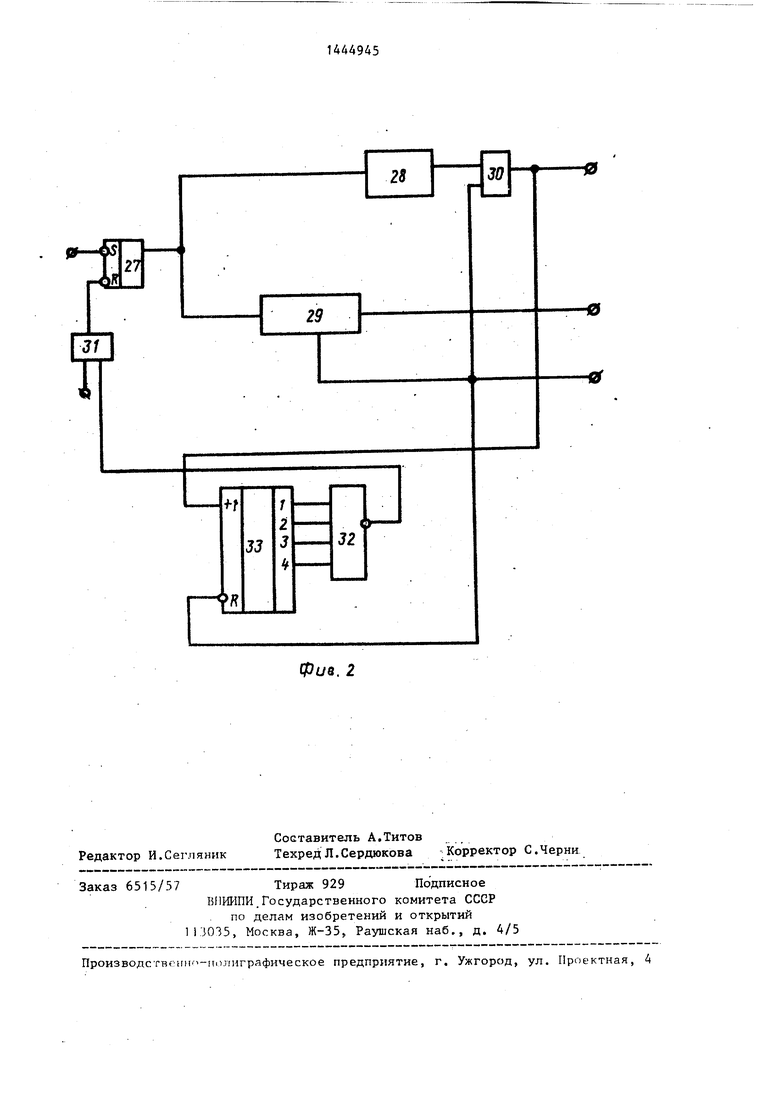

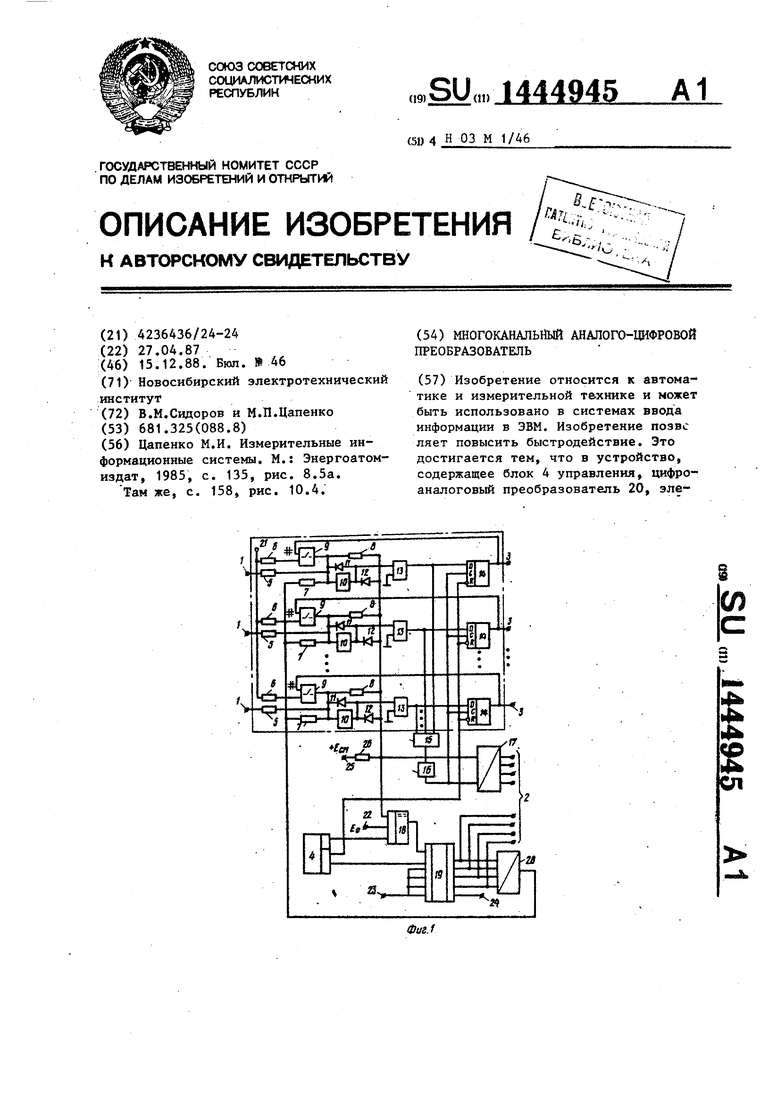

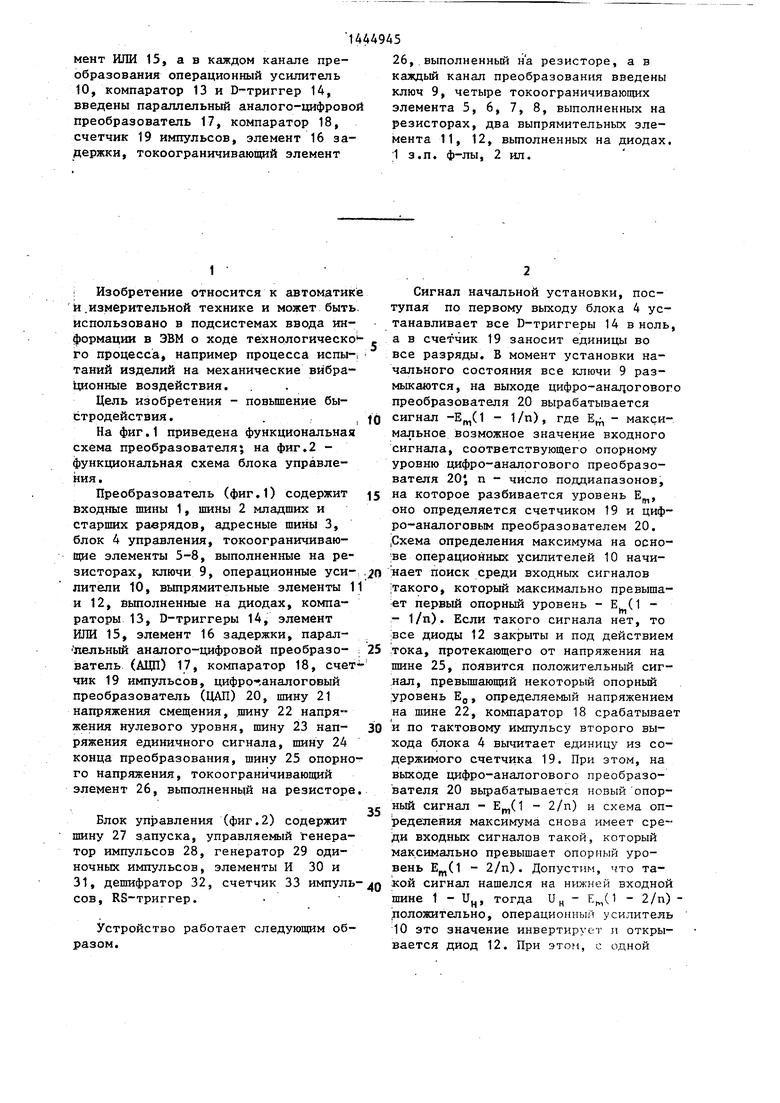

На фиг.1 приведена функциональная схема преобразователя; на фиг.2 - функциональная схема блока управления .

Преобразователь (фиг.1) содержит входные шины 1, шины 2 младших и старших раврядов, адресные шины 3, блок 4 управления, токоограничиваю- цие элементы 5-8, выполненные на резисторах, ключи 9, операционные уси-; лители 10, выпрямительные элементы 11 и 12, вьшолненные на диодах, компараторы 13, D-триггеры 14, элемент ШШ 15, элемент 16 задержки, парал- пельный аналого-цифровой преобразо- : :ватель (АЦП) 17, компаратор 18, счеТ чик 19 импульсов, цифррганалоговый преобразователь (ЦДЛ) 20, шину 21 напряжения смещения, .шину 22 напря™ жения нулевого уровня, шину 23 нап- ряжения единичного сигнала, шину 24 конца преобразования, шину 25 опорного напряжения, токоограничивающий элемент 26, вьтолненный на резисторе.

Блок управления (фиг.2) содержит шину 27 запуска, управляемый Генератор импульсов 28, генератор 29 оди- ночньгх импульсов, элементы И 30 и 31, дешифратор 32, счетчик 33 импульсов, RS-триггер.

Устройство работает следующим образом.

ой U4A9A5

26, выполненный на резисторе, а в каждый канал преобразования введены ключ 9, четыре токоограничивающих элемента 5, 6, 7, 8, выполненных на резисторах, два выпрямительных элемента 11, 12, вьтолненньгх на диодах 1 з.п. ф-лы, 2 ил.

Сигнал начальной установки, поступая по первому выходу блока 4 устанавливает все D-триггеры 14 в ноль, а в счетчик 19 заносит единицы во все разряды. В момент установки начального состояния все ключи 9 раз- мьжаются, на выходе цифро-анацоговог преобразователя 20 вырабатывается сигнал -Е(1 - 1/п), где Е - максимальное возможное значение входного сигнала, соответствующего опорному уровню цифро-аналогового преобразователя 20, п число поддиапазонов, на которое разбивается уровень Е,,, оно определяется счетчиком 19 и цифро-аналоговым преобразователем 20. ,Схема определения максимума на основе операционных усилителей 10 начи- нает поиск среди входных сигналов такого, который максимально превыша- ет первый опорный уровень - Е (1 - - 1/п). Если такого сигнала нет, то :все диоды 12 закрыты и под действием :тока, протекающего от напряжения на шине 25, появится положительный сиг- .нал, превьшгающий некоторый опорный уровень ЕО, определяемый напряжением на шине 22, компаратор 18 срабатывае и по тактовому импульсу второго выхода блока 4 вычитает единицу из содержимого счетчика 19. При этом, на выходе цифро-аналогового преобразователя 20 вырабатывается новый опорный сигнал - Е(1 - 2/п) и схема определения максимума снова имеет среди входных сигналов такой, который максимально превышает опорный уровень Е(1 - 2/п). Допустим, что такой сигнал нашелся на нижней входной шине 1 - и, тогда U - Е(1 - 2/п) положительно, операционный усилитель 10 это значение инвертирует и открывается диод 12. При этом, с одной

стороны вход параллельного аналого- цифрового преобразователя 17 поступает значение

-К(и, - 2Ejn),

где К

51 55 R, R7

и определяется соотношением резисторов 8 и 5. Подразумевается, что резисторы 5 и 7 равны между собой, С другой стороны, отрицательный сигнал на входе компаратора 13 нижнего канала вызывает его срабатывание, благодаря чему через элементы 15 и 16 проходит сигнал, который строби- рует управляющий вход параллельного аналого-цифрового преобразователя 17 и D-триггеры 14, вследствие чего на

фронт на адресной шине 3 является динамическим признаком адреса, работающего канала, а соответственно и адреса цифровой информации, которая появляется на шине 2 устройства, одновременно сигнал на выходе D-триггера 14 вызьшает замыкание ключа 9 в соответствующем ему канале (в данном

0 случае - в нижнем). При этом, на вход соответствующего операционного усилителя 10 подается ток смещения по щи- не 21 (Еб через резистор 6 и эквивалентный входной сигнал уже никогда

5 не будет положительным в данном канале fe течение текущего цикла работы, поскольку I ЕЙ/КЙ Теперь схема вьщеления максимума снова ищет входной сигнал, превышак)щий опорный

выходе параллельного аналого-цифрово- 20 уровень Е(1 - 2/п), допустим, что го преобразователя 17 появляется циф- такой нащелся во втором канале сверровой эквивалент величины - - Е(1 2/п), D-триггер 14 нижнего канала срабатывает и положительный

ху и Естественно, что U Цц и в предыдущем такте на входе операционного усилителя суммарный ток;

т, /р У,,,, R, к„R

поскольку R.

отрицательный и

диод 12 закрыт. Теперь же, когда нижний канал выключен из работы, срабатывает второй канал, так как Uj, - - Е(1 - 2/п) положительно и других сигналов больше данного V по величи- не на работающих входах кет. Соответ ственно открывается диод 12 второго канала, операционный усилитель отсле- чрвает на входе параллельного ана- дого-цифрового преобразователя 17 сигнал -к1 - Е(1 - 2/n)J, срабатывает компаратор 13 второго канала И через элементы 15 и 16 стробирует параллельный аналого-цифровой преобразователь 17 и D-триггеры 14. При этом, положительный.фронт на шине 3 второго канала указывает адрес цифровой информации, появляющейся на шине 2 и одновременно вызывает срабатывание ключа 9 второго канала, вслед ствие чего второй канал отключается. Поскольку теперь на входных клеммах нет входных сигналов, превышающих опорный уровень, то диоды Т2 все закрыты, диоды 11 все открыты и через резистор 26 от напряжения на шине 25 на входе компаратора 18 устанавливается положительный сигнал, превышающий пороговый уровень Е. Компара

449А54

фронт на адресной шине 3 является динамическим признаком адреса, работающего канала, а соответственно и адреса цифровой информации, которая появляется на шине 2 устройства, одновременно сигнал на выходе D-триггера 14 вызьшает замыкание ключа 9 в соответствующем ему канале (в данном

0 случае - в нижнем). При этом, на вход соответствующего операционного усилителя 10 подается ток смещения по щи- не 21 (Еб через резистор 6 и эквивалентный входной сигнал уже никогда

5 не будет положительным в данном канале fe течение текущего цикла работы, поскольку I ЕЙ/КЙ Теперь схема вьщеления максимума снова ищет входной сигнал, превышак)щий опорный

ху и Естественно, что U Цц и в предыдущем такте на входе операционного усилителя суммарный ток;

тор 18 срабатывает по очередному тактовому импульсу, единичка вычитается из содержимого счетчика 19 и уменьшается абсолютная величина напряжения на выходе параллельного аналого-цифрового преобразователя 20. После опроса всех возможных значений входных сигналов, а соответственно и всех входных клемм, компаратор J8 сработает последний раз в течение цикла коммутации, когда в счетчике 19 установлен нуль, на выходе цифро-аналогового преобразователя 20 - нуль, а сигналов, его превышающих, не осталось среди работающих каналов. Сигнал на шине 24 в данном случае ука- зьтает, что цикл опроса входных клемм устройства завершен. Другой возможный признак завершения цикла опроса - установка всех D-триггеров 14 в единицу, при этом сигнал завершения цикла вырабатывается на выходе элемента 15, входы которого соедннейы с выходами D-триггеров 14.

Блок 4 (фиг.2) р аботает следующим образом.

Перед началом цикла преобразования RS-триггер в нулевом состоянии. Управляемый генератор 28 поддержива ет на своем выходе высокий потенци ср

51444945

ал, поскольку на инверсном выходе ге- где п нератора 29 также высокий потенциал, t, на втором входе, блока 4 также высокий потенциал. Импульс запуска, поступая на S-вход RS-триггера, переводит его в единичное состояние, включая управляемый генератор 28, одно- эременно генератор 29 запускается и по прямому выходу производит в рчет- ю чике 19 начальную установку, а по инверсному выходу сбрасывает в нулевое состояние D-триггеры 14 и устанавливает счетчик 33 в ноль. Одновременно нулевой сигнал на инверсном выходе 15 запрещает прохождение через элемент 30 первого импульса управляемого генератора 28. По окончании одиночного импульса второй импульс управляемого

J

число поддиапазонов} время просмотра поддиапазона;

К число каналов

время сравнения начала с

поддиапазоном.

Поскольку синхронизацию работы всего устройства выполняет генератор то период его работы Tc й§Л , т.е. максимальному из двух. Следовательно, время цикла можно оценить как:

(п + К) Т

сч

(2)

В то же время в известном устройстве время цикла t определяется также временем прохождения всего диапазона и временем, выделяемым на сравнение эталонов с входными величинами.

гейератора 28 проходив на второй вы- i 20 Если сравнить время прохождения всеХод и начинает опрос компаратора 18 При этом, счетчик 33 считает количество импульсов опроса и, когда оно совпадает с требуемым срабатывает

го диапазона для двух устройств, т они близки друг к другу при одинак вых усилителях. Различие появляется во временах сравнения. Соответстве

дешифратор 45 и нулевым сигналом че- 25 но, если для известного устройства

«J

рез элемент 31 сбрасывает RS-триггер в исходное состояние. Сброс RS-триг- гера может быть также выполнен при необходимости либо от любого из сигналов об окончании цикла преобразования, вырабатьшаемых в устройстве, либо от сигнала сброса. Для этого Служит второй вход в элементе 31. Нулевой сигнал на входе RS-триггера д)(ерзштся все время до появления нулевого потенциала на входе шины за- пуска. По S-входу нулевой потенциал переводит прямой выход RS-триггера в единичное состояние, вызывая все

названные установки по генератору 29, 4о образования, каждый из которых содерпри этом нулевой сигнал по коду счетчика 33 переходит в положительный и с RS-триггера снимается нулевой потенциал по R-входу.

Быстродействие устройства опреде ляется временем просмотра поддиапа- зонов и числом входных каналов, поскольку для каждого канала требуется определение его цифрового эквивалента с помощью компараторов параллельного АЦП. Предельное быстродействие ограничивается в первую очередь имен но этими временами. Поэтому можно записать время цикла разом:

ty следующим об- .55

nto + К t

ср

(1)

число поддиапазонов} время просмотра поддиапазона;

ср

где п t,

К число каналов

время сравнения начала с

поддиапазоном.

Поскольку синхронизацию работы всего устройства выполняет генератор то период его работы Tc й§Л , т.е. максимальному из двух. Следовательно, время цикла можно оценить как:

(п + К) Т

сч

(2)

в известном устройt определяется такждения всего диапавыделяемым на сраввходными величинами.

го диапазона для двух устройств, то они близки друг к другу при одинаковых усилителях. Различие появляется во временах сравнения. Соответствен25 но, если для известного устройства

30

«J

потребуется 2 - актов сравнения, где N - разрядность двоичного числа, то для данного устройства всего К сравнений и, если даже t

J5

-op

то всегда найдется N, при котором устройство имеет преимущество в быстродействии.

Формула и-з обретения

0

5

жит последовательно соедийенные операционный усилитель, компаратор и D-триггер, R-входы D-триггеров всех каналов преобразователя объединены и соединены с первым выходом блока управления, D-вход каждого D-триг- гера соединен с выходом соответствующего компаратора канала преобразования, отл-и чающийся тем, что, с целью повьпиёния быстродействия, в него введены параллельный аналого-цифровой преобразователь, токо- ограничивающий элемент, выполненный на резисторе, элемент задержки, компаратор, счетчик импульсов, а в каждый канал преобразования введены ключ, четыре токоограничивающих элемента, выполненных на резисторах, два выпрямительных элемента, выполненных на диодах, аноды первых диодо объединены с первыми выводами первых резисторов всех каналов преобразования, первым выводом резистора, информационными входами параллельного аналого-цифрового преобразователя и компаратора в каждом канапе преобразования, катод первого диода объединен с анодом второго диода, первым входом компаратора, вход операционного усилителя объединен с катодом второго диода, вторым выводом первог резистора, первыми выводами второго и третьего резисторов и соединен с выходом ключа, аналоговый вход которого соединен с первым выводом четвертого резистора, управляющий вход соединен с выходом D-триггера и является соответствующей адресной ши- ной, вторые выводы четвертых резисторов всех каналов преобразования объединены и являются шиной напряжения смещения, второй вывод третьего резистора каждого канала преобразо- вания является соответствующей входной шиной, второй вход компаратора каждого канала преобразования является шиной нулевого потенциала, С- входы D-триггеров всех каналов пре- образования объединены с управляющим входом параллельного аналого-цифрового преобразователя и через элемент задержки соединены с выходом, элемента ИЛИ, каждый i-й вход которого со- единен с выходом компаратора i-ro канала преобразойания, причем второй вывод рез истора является шиной опорного напряжения, второй выход блока управления соединен со стробирующим входом компаратора, вход смещения которого является шиной напряжения нулевого уровня, а выход соединен с вычитающим входом.счетчика импульсов счетный вход которого соединен с третьим выходом блока управления, установочные входы объединены и являются шиной логической единицы, информационные выходы соединены поразрядно с соответствующими входами цифроанало- гового преобразователя и являются соответствующими шинами старших разрядов, выход переполнения является шиной Конец преобразования, шинами младших разрядов являются соответствующие выходы параллельного аналого- цифрового преобразователя, а выход цифроаналогового преобразователя со- eдинe с вторыми выводами вторых резисторов всех каналов преобразования

Фиш. 2

| Цапёнко М.И | |||

| Измерительные информационные системы | |||

| М.: Энергоатом- издат, 1985, с | |||

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Там же, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-27—Подача