Изобретение относится к области обучающих устройств и может быть использовано для получения практических навыков работы с цифровыми и аналоговыми электрическими схемами, преобразователями аналоговых сигналов в цифровой код и обратно (АЦП и ЦАП), а также исследования динамики их работы.

Наиболее близким техническим решением, выбранным в качестве прототипа, является стенд для изучения электронных средств автоматизации (RU, 2279718 C1, G09B 23/18). Стенд содержит счетчик, шесть коммутаторов, дешифратор двоичного кода в позиционный, регистр, блок переключателей, аналоговый сумматор, блок триггеров, блок индикации, блок ввода-вывода, блок логических элементов, набор диодов, набор резисторов, набор конденсаторов, блок аналоговых компараторов, блок управления, регулятор напряжения, генератор, вольтметр и наборное поле с комплектом перемычек - соединителей.

Недостатком данного прототипа являются низкие дидактические возможности устройства. Так, наличие многоразрядных коммутаторов для автоматического выполнения групповых соединений снижает степень усвоения материала. Отсутствие возможности практического изучения работы готового АЦП затрудняет процесс сборки и исследования АЦП и разнообразных гибридных электронных схем из элементов стенда. При изучении работы схем в динамике в блоке ввода-вывода фиксируются только изменения логических сигналов в контрольных точках. Возможность параллельной записи и последующего синхронного воспроизведения на мониторе компьютера временных диаграмм цифровых и аналоговых сигналов не предусмотрена. это ограничивает дидактические возможности устройства.

Задача, решаемая изобретением - повышение дидактических возможностей устройства.

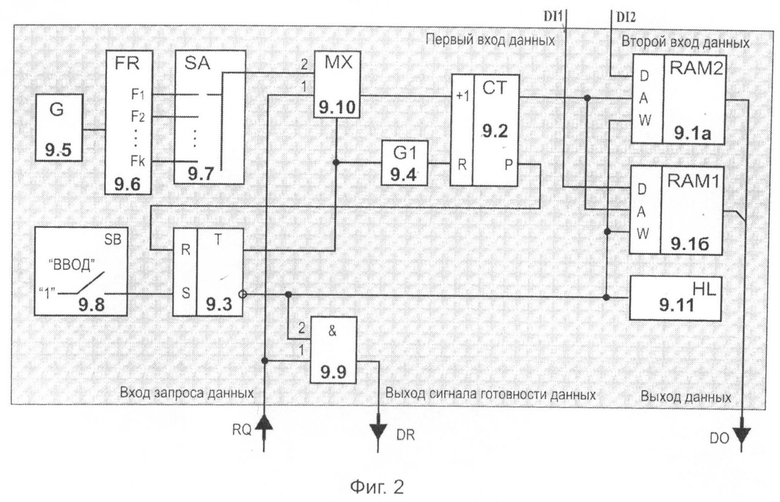

Указанная задача выполняется за счет того, что в стенд, содержащий дешифратор двоичного кода в позиционный, комплект перемычек-соединителей и наборное поле, к гнездам которого подключены блок триггеров, блок логических элементов, набор диодов, первый блок индикации, блок управления, счетчик, регистр, генератор, блок переключателей, аналоговый сумматор, блок компараторов, регулятор напряжения, набор резисторов, набор конденсаторов и блок ввода-вывода, вход запроса данных, выход данных и выход подтверждения готовности данных которого являются соответствующими выходами стенда, а первый вход данных подключен к входу первого блока индикации; блок ввода-вывода содержит первый модуль оперативной памяти, счетчик адреса, триггер, генератор одиночных импульсов, генератор импульсов записи, делитель частоты, переключатель, кнопку «ВВОД», элемент «И», индикатор и мультиплексор, первый вход которого является входом запроса данных блока ввода-вывода и соединен с первым входом элемента «И», выход которого является выходом готовности данных блока ввода-вывода, выход мультиплексора подключен к инкрементному входу счетчика адреса, выход которого подключен к адресному входу первого модуля оперативной памяти, вход данных которого является первым входом данных блока ввода-вывода, а вход разрешения записи подключен к входу индикатора, к второму входу элемента «И» и инверсному выходу триггера, прямой выход которого подключен к управляющему входу мультиплексора и входу запуска генератора одиночных импульсов, выход которого подключен к входу сброса счетчика адреса, выход переполнения которого подключен к входу сброса триггера, установочный вход которого подключен к выходу кнопки «ВВОД», вход которой подключен к уровню логической единицы, второй вход мультиплексора подключен к выходу переключателя, входы которого подключены к соответствующим выходам делителя частоты, вход которого подключен к выходу генератора импульсов записи; аналоговый сумматор содержит N+1 резистор и операционный усилитель, выход которого соединен с выходом первого резистора и является выходом аналогового сумматора, входы которого с 1 до N являются входами резисторов со 2-го до N+1-го, выходы которых объединены и подключены ко входу первого резистора и к первому входу операционного усилителя, второй вход которого подключен к уровню логического ноля, а номиналы резисторов с 1-го по N+1 относятся, как 1:21:22:…2N; блок переключателей содержит N переключателей, нормально-замкнутые входы которых являются первым входом блока, вторым входом которого являются нормально-разомкнутые входы переключателей, управляющие входы которых образуют многоканальный управляющий вход блока, а выходы - многоканальный выход блока; блок управления содержит набор переключателей и кнопок, входы которых объединены и подключены к уровню логического ноля, а нормально-замкнутые и нормально-разомкнутые выходы каждого переключателя и каждой кнопки подключены соответственно к инверсным входам R и S соответствующих триггеров, прямые и инверсные выходы которых подключены к соответствующим гнездам наборного поля; генератор содержит генератор прямоугольных импульсов, переключатель и делитель частоты, вход которого подключен к выходу генератора прямоугольных импульсов, а каждый выход - к соответствующему входу переключателя, выход которого и является выходом генератора, дополнительно введены второй блок индикации, содержащий линейный многоразрядный светодиодный индикатор, и аналого-цифровой преобразователь, вход которого подключен к соответствующим гнездам наборного поля, а выход соединен с входом второго блока индикации и вторым входом данных блока ввода-вывода; блок ввода-вывода дополнительно содержит второй модуль оперативной памяти, вход данных которого подключен к второму входу данных блока ввода-вывода, выход данных которого образуют объединенные в многоразрядную шину данных выходы первого и второго модулей оперативной памяти; первый блок индикации дополнительно содержит знакосинтезирующий индикатор, входы которого подключены к соответствующему разряду входа блока индикации.

Предложенное техническое решение имеет следующие отличительные от прототипа признаки:

- наличие второго блока индикации с многоразрядным светодиодным индикатором;

- наличие АЦП, вход которого подключен к гнездам наборного поля, а выход соединен с входом второго блока индикации и вторым входом данных блока ввода-вывода;

- наличие второго модуля оперативной памяти в блоке ввода-вывода, второй вход данных которого подключен к входу данных модуля оперативной памяти;

- наличие знакосинтезирующего индикатора в первом блоке индикации.

Второй блок индикации, отображает изменение выходного кода АЦП при изменении величины аналогового сигнала на его входе. Это не только позволяет использовать его для оценки величины входного напряжения, но и демонстрирует принцип работы АЦП, что повышает дидактические возможности устройства.

Второй модуль оперативной памяти в блоке ввода-вывода служит для записи кодов напряжения исследуемого аналогового сигнала с выхода АЦП одновременно с текущими значениями логических сигналов в контрольных точках схемы, которые фиксируются в первом модуле оперативной памяти. Записанные коды считываются в компьютер, который под управлением соответствующего программного обеспечения одновременно выполняет функции логического анализатора и электронного осциллографа. Возможность параллельного воспроизведения временных диаграмм цифровых и аналоговых сигналов обеспечивает максимальную наглядность при исследовании схем гибридных электронных устройств, что также повышает дидактические возможности стенда.

Знакосинтезирующий индикатор первого блока индикации используется для отображения буквенно-цифровой информации. Это повышает дидактические возможности стенда при изучении принципов работы гибридных электронных устройств с цифровым представлением выходной информации (например, цифровых измерительных приборов).

Приведенная совокупность признаков, характеризующих заявленный объект, обуславливает достижение технического результата, обеспечивающего решение задачи изобретения.

Анализ уровня техники показывает, что авторам не известен стенд, которому присуща вся совокупность признаков, идентичная всей совокупности существенных признаков данного изобретения. Это говорит о новизне предложенного технического решения.

Предложенное техническое решение применимо, работоспособно, осуществимо и воспроизводимо, так как может быть изготовлено в условиях единичного и серийного производства с применением выпускаемых серийно комплектующих, поэтому соответствует условию патентоспособности «промышленная применимость».

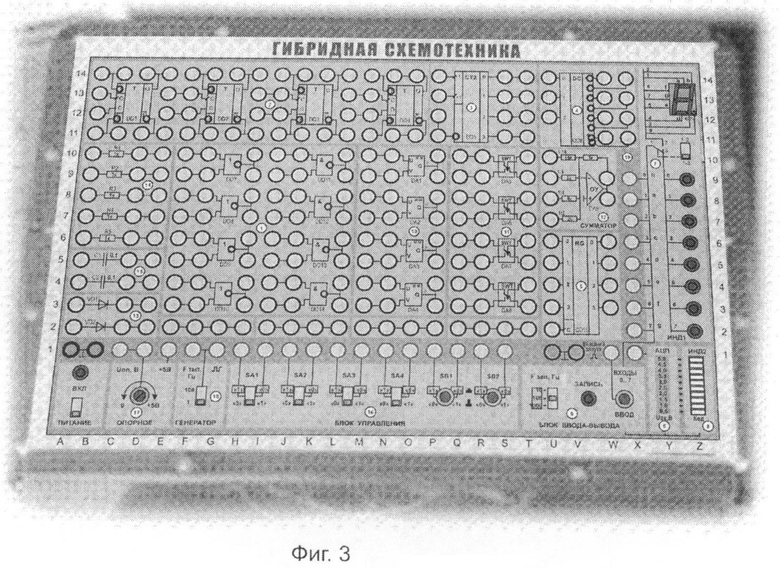

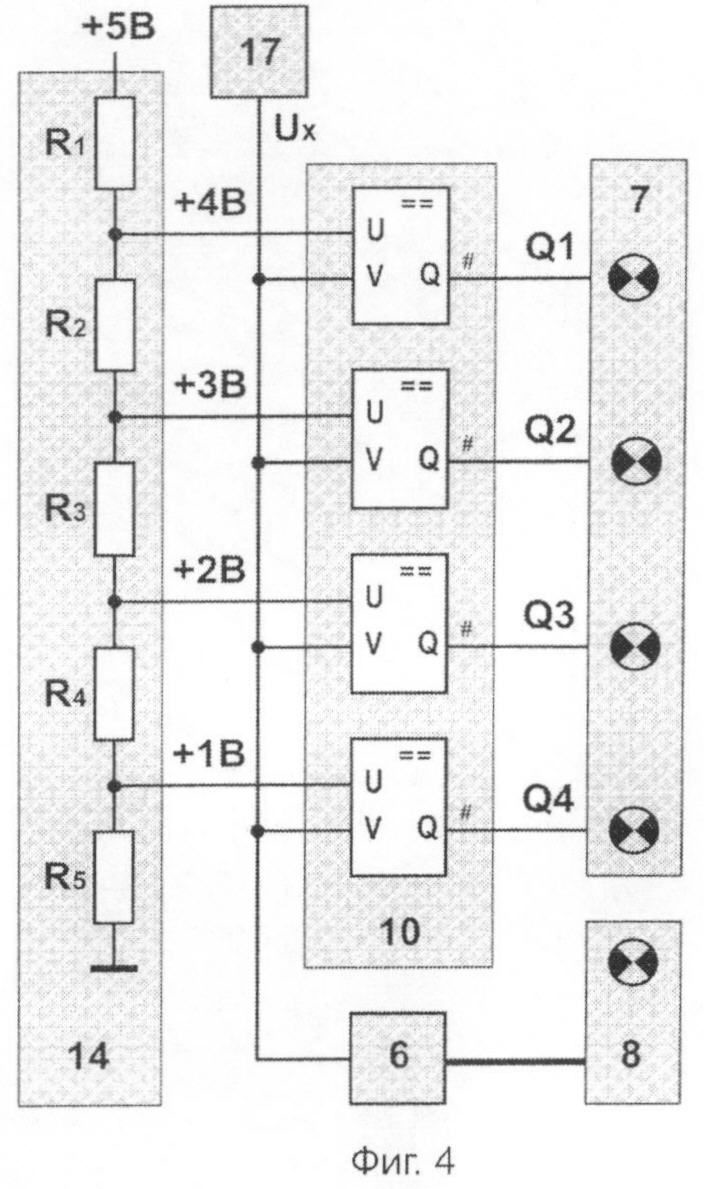

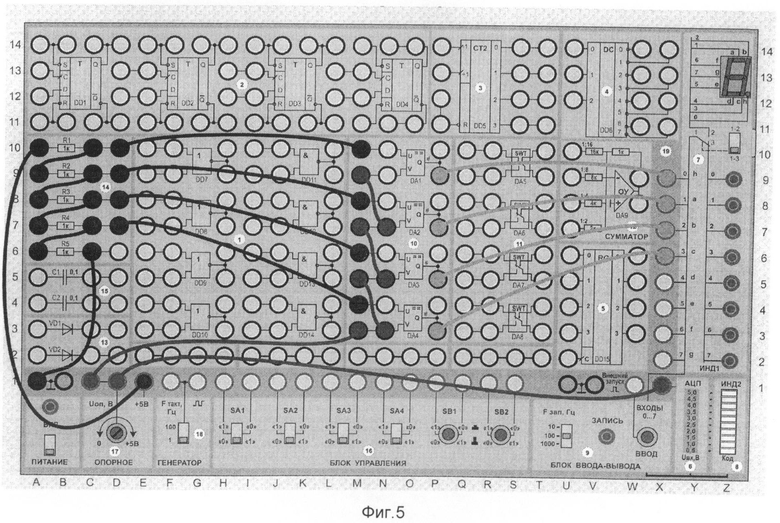

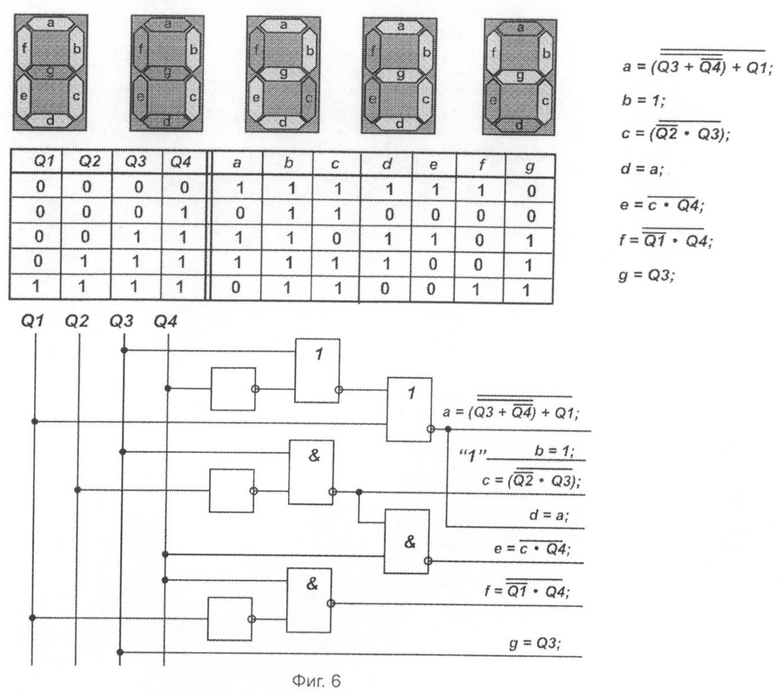

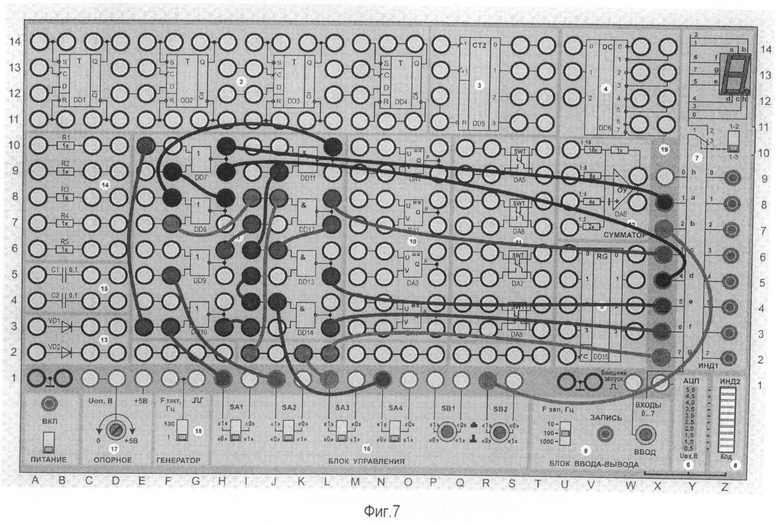

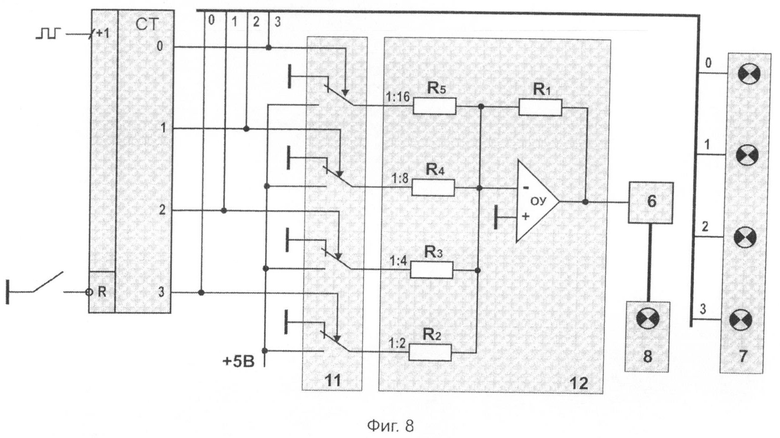

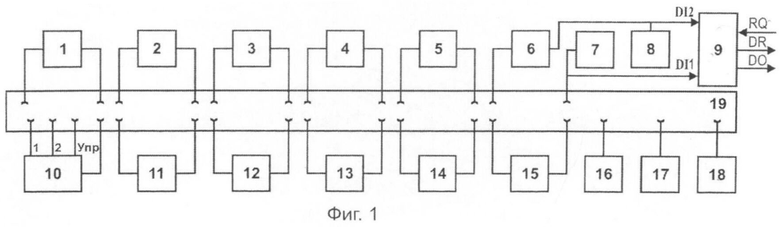

На фиг.1 изображена структурная схема учебного стенда; на фиг.2 - схема блока ввода-вывода; на фиг.3 - внешний вид макетного образца стенда (его наборное поле выполнено в виде мнемосхемы с изображенными на ней функциональными обозначениями элементов, выводы обозначений подведены к гнездам, к которым подключены реальные элементы, расположенные внутри корпуса стенда); на фиг.4 - вариант схемы параллельного двухразрядного АЦП; на фиг.5 - пример сборки схемы параллельного двухразрядного АЦП на наборном поле стенда; на фиг.6 - вариант схемы неполного дешифратора весового кода в семисегментный; на фиг.7 - пример сборки схемы неполного дешифратора весового кода в семисегментный из элементов наборного поля 2И-НЕ и 2ИЛИ-НЕ; на фиг.8 - вариант схемы цифро-аналогового преобразователя; на фиг.9 - пример сборки схемы цифро-аналогового преобразователя из элементов наборного поля стенда.

Стенд для изучения гибридных электронных устройств (фиг.1) содержит: блок логических элементов 1, блок триггеров 2, счетчик 3, дешифратор двоичного кода в позиционный 4, регистр 5, аналого-цифровой преобразователь 6, первый блок индикации 7, второй блок индикации 8, блок ввода-вывода 9, блок компараторов 10, блок переключателей 11, аналоговый сумматор 12, набор диодов 13, набор резисторов 14, набор конденсаторов 15, блок управления 16, регулятор напряжения 17, генератор 18, наборное поле 19 с комплектом перемычек-соединителей. Блок ввода-вывода 9 (фиг.2) содержит: два модуля оперативной памяти 9.1а и 9.1б, счетчик адреса 9.2, триггер 9.3, генератор одиночных импульсов 9.4, генератор импульсов записи 9.5, делитель частоты 9.6, переключатель 9.7, кнопку «Ввод» 9.8, элемент «И» 9.9, мультиплексор 9.10 и индикатор 9.11.

Устройство работает следующим образом.

При изучении работы комбинационных логических схем обучаемый с помощью кнопок и переключателей блока управления 16 задает входные воздействия («0», «1») на схему, собранную из логических элементов блока 1, контрольные точки которой подключаются к первому блоку индикации 8 для визуального контроля их состояния. Таким же образом изучается работа триггерных схем различной структуры, собранных из элементов блока 2. При изучении работы счетчиков и регистров обучаемый собирает на наборном поле 19 различные варианты приведенных в методическом задании схем, входные состояния которых задаются с помощью блока управления 16, а состояния входов и выходов собранной схемы отображаются индикаторами блока индикации 7.

При изучении работы комбинированных устройств, например, цифро-аналогового или аналого-цифрового преобразователей, используются блок компараторов 10, блок переключателей 11, аналоговый сумматор 12. Опорное напряжение задается с помощью регулятора напряжения 17. Тактовые сигналы задаются с помощью генератора 18.

Набор диодов 13 используется для построения формирователей, объединителей, разветвителей. Наборы резисторов 14 и конденсаторов 15 используются для формирования интегрирующих и дифференцирующих цепочек, линий задержки, резисторных делителей напряжения и др.

Для контроля напряжения в «шаговом» режиме соответствующий аналоговый сигнал подключают к входу АЦП и оценивают его уровень с помощью индикаторов блока индикации 7.

Чтобы исследовать работу схем в динамике, тактовые сигналы задаются с помощью генератора 18, а текущие состояния логических и аналоговых сигналов в контрольных точках заносятся в память блока ввода-вывода 9 с частотой импульсов записи, заданной положением переключателя 9.7. Они могут быть считаны в компьютер через стандартный интерфейс.

Блок ввода-вывода 9 работает следующим образом.

В исходном состоянии счетчик адреса 9.2 и триггер 9.3 сброшены. Сигнал с прямого выхода триггера подключает первый вход мультиплексора 9.10, соединенный с входом запроса данных блока, к инкрементному входу счетчика 9.2. А сигнал с инверсного выхода триггера устанавливает модули оперативной памяти 9.1а и 9.1б в режим чтения и разрешает формирование сигнала готовности данных. Индикатор 9.11 светится, сигнализируя о готовности к обмену данными с компьютером.

При поступлении сигнала запроса данных, хранящихся в оперативной памяти блока ввода-вывода, на выходе элемента «И» 9.9 формируется сигнал готовности данных, по которому данные, хранящиеся в ячейке памяти с адресом 0, могут быть считаны с выхода данных блока. По снятию сигнала запроса данных состояние счетчика адреса увеличивается, и на выход поступают данные, хранящиеся в следующей ячейке памяти. Далее процесс чтения содержимого памяти повторяется.

Для занесения данных в память следует выбрать нужную частоту импульсов записи переключателем 9.7 и нажать кнопку 9.8 («ВВОД»). При этом триггер 9.3 взводится, сигнал с его прямого выхода поступает на вход генератора 9.4, который вырабатывает одиночный импульс сброса счетчика адреса 9.2, и на управляющий вход мультиплексора 9.10, который подключает к инкрементному входу счетчика адреса 9.2 выход переключателя 9.7. При этом сигнал с инверсного выхода триггера 9.3 запрещает формирование сигнала готовности данных и устанавливает модули оперативной памяти 9.1а и 9.1б в режим записи. Индикатор 9.11 гаснет, а данные с первого и второго входов данных блока ввода-вывода записываются с нужной частотой в ячейки модулей памяти 9.1а и 9.1б, пока сигнал переполнения счетчика адреса 9.2 не сбросит триггер 9.3, переводя блок ввода-вывода в исходное состояние.

Примеры работы со стендом.

Пример 1. Обучаемый выполняет задание: собрать и проверить работоспособность параллельного двухразрядного АЦП, схема которого приведена на фиг.4.

Обучаемый собирает схему на наборном поле стенда с помощью перемычек-соединителей (пример сборки - на фиг.5), устанавливает соответствие входного напряжения Ux (подается от регулятора напряжения 18), и выходного кода, который отображается светодиодами первого блока индикации 7. Для проверки правильности работы схемы выход регулятора напряжения 18 подключают к входу АЦП 6 и сравнивают показания индикаторов блоков индикации 7 и 8.

Пример 2. Обучаемый выполняет задание: разработать, собрать и наладить схему одноразрядного цифрового вольтметра для вывода кода из примера 1.

Обучаемый синтезирует схему неполного дешифратора весового кода в семисегментный, используя элементы 2И-НЕ и 2ИЛИ-НЕ блока логических элементов 1, таблицы истинности и законы булевой алгебры, как показано на фиг.6. Пример сборки разработанной схемы - на фиг.7. Выходы схемы подключаются к соответствующим входам знакосинтезирующего индикатора первого блока индикации 7. При отладке входной код задается переключателями блока управления 16. Входы отлаженной схемы соединяются с выходами АЦП из примера 1.

Пример 3. Обучаемый выполняет задание: собрать и проверить работоспособность цифро-аналогового преобразователя, схема которого приведена на фиг.8.

Обучаемый собирает схему на наборном поле стенда (пример сборки - на фиг.9) и визуально устанавливает соответствие входного кода, поступающего на ЦАП с выхода счетчика 3, и напряжения на его выходе. Для этого выход сумматора подключается к входу АЦП, а тактовые импульсы на инкрементный вход счетчика подаются либо вручную - кнопкой блока управления 16, либо от генератора 18, работающего на пониженной тактовой частоте.

Для записи состояний контрольных точек в память блока ввода-вывода, обучаемый выбирает частоту записи данных переключателем 9.7 и нажимает кнопку 9.8 «ВВОД».

Для автоматического построения временных диаграмм обучаемый с помощью компьютера и соответствующего программного обеспечения посылает запрос RQ на выдачу данных, записанных в модулях памяти блока ввода-вывода. Данные считываются в компьютер и отображаются на экране монитора в виде временных диаграмм, удобных для выполнения компьютерных измерений.

Источники информации

1. Патент RU №2279718 С1, МПК G09B 23/18, «Стенд для изучения электронных средств автоматизации», опубл. 10.07.2006 г., бюл. №19, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 2002 |

|

RU2237927C2 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1781692A1 |

| УЧЕБНЫЙ СТЕНД ПО ЭЛЕКТРОНИКЕ | 2016 |

|

RU2636020C1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1775728A1 |

| Устройство для обучения основам вычислительной техники | 1988 |

|

SU1564682A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1714660A1 |

| Устройство для обучения и контроля глубины знаний обучаемых | 1991 |

|

SU1789999A2 |

| БИНОКУЛЯРНОЕ УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ТРОМБОЗА ГЛУБОКИХ ВЕН ГОЛЕНИ | 2006 |

|

RU2305487C1 |

Изобретение относится к области электронных обучающих устройств. Стенд для изучения гибридных электронных устройств содержит: блок логических элементов, блок триггеров, счетчик, дешифратор двоичного кода в позиционный, регистр, аналого-цифровой преобразователь, первый блок индикации, второй блок индикации, блок ввода-вывода, блок компараторов, блок переключателей, аналоговый сумматор, набор диодов, набор резисторов, набор конденсаторов, блок управления, регулятор напряжения, генератор. Второй блок индикации содержит линейный многоразрядный светодиодный индикатор. Вход аналого-цифрового преобразователя подключен к соответствующим гнездам наборного поля, а выход соединен с входом второго блока индикации и вторым входом данных блока ввода-вывода. Блок ввода-вывода дополнительно содержит второй модуль оперативной памяти, вход данных которого подключен ко второму входу данных блока ввода-вывода, выход данных которого образуют объединенные в многоразрядную шину данных выходы первого и второго модулей оперативной памяти. Первый блок индикации дополнительно содержит знакосинтезирующий индикатор, входы которого подключены к соответствующему разряду входа блока индикации. Техническим результатом изобретения является получение практических навыков работы с цифровыми и гибридными электронными устройствами, исследования динамики работы цифровых устройств и выполнения компьютерных измерений. 9 ил.

Стенд для изучения гибридных электронных устройств, содержащий дешифратор двоичного кода в позиционный, комплект перемычек-соединителей и наборное поле, к гнездам которого подключены блок триггеров, блок логических элементов, набор диодов, первый блок индикации, блок управления, счетчик, регистр, генератор, блок переключателей, аналоговый сумматор, блок компараторов, регулятор напряжения, набор резисторов, набор конденсаторов и блок ввода-вывода, вход запроса данных, выход данных и выход подтверждения готовности данных которого являются соответствующими выходами стенда, а первый вход данных подключен к входу первого блока индикации; блок ввода-вывода содержит первый модуль оперативной памяти, счетчик адреса, триггер, генератор одиночных импульсов, генератор импульсов записи, делитель частоты, переключатель, кнопку «ВВОД», элемент «И», индикатор и мультиплексор, первый вход которого является входом запроса данных блока ввода-вывода и соединен с первым входом элемента «И», выход которого является выходом готовности данных блока ввода-вывода, выход мультиплексора подключен к инкрементному входу счетчика адреса, выход которого подключен к адресному входу первого модуля оперативной памяти, вход данных которого является первым входом данных блока ввода-вывода, а вход разрешения записи подключен к входу индикатора, к второму входу элемента «И» и инверсному выходу триггера, прямой выход которого подключен к управляющему входу мультиплексора и входу запуска генератора одиночных импульсов, выход которого подключен к входу сброса счетчика адреса, выход переполнения которого подключен к входу сброса триггера, установочный вход которого подключен к выходу кнопки «ВВОД», вход которой подключен к уровню логической единицы, второй вход мультиплексора подключен к выходу переключателя, входы которого подключены к соответствующим выходам делителя частоты, вход которого подключен к выходу генератора импульсов записи; аналоговый сумматор содержит N+1 резистор и операционный усилитель, выход которого соединен с выходом первого резистора и является выходом аналогового сумматора, входы которого с 1 до N являются входами резисторов со 2-го до N+1-го, выходы которых объединены и подключены ко входу первого резистора и к первому входу операционного усилителя, второй вход которого подключен к уровню логического ноля, а номиналы резисторов с 1-го по N+1 относятся, как 1:21:22:…2N; блок переключателей содержит N переключателей, нормально-замкнутые входы которых являются первым входом блока, вторым входом которого являются нормально-разомкнутые входы переключателей, управляющие входы которых образуют многоканальный управляющий вход блока, а выходы - многоканальный выход блока; блок управления содержит набор переключателей и кнопок, входы которых объединены и подключены к уровню логического ноля, а нормально-замкнутые и нормально-разомкнутые выходы каждого переключателя и каждой кнопки подключены соответственно к инверсным входам R и S соответствующих триггеров, прямые и инверсные выходы которых подключены к соответствующим гнездам наборного поля; генератор содержит генератор прямоугольных импульсов, переключатель и делитель частоты, вход которого подключен к выходу генератора прямоугольных импульсов, а каждый выход - к соответствующему входу переключателя, выход которого и является выходом генератора, отличающийся тем, что в состав стенда дополнительно введены второй блок индикации, содержащий линейный многоразрядный светодиодный индикатор, и аналого-цифровой преобразователь, вход которого подключен к соответствующим гнездам наборного поля, а выход соединен с входом второго блока индикации и вторым входом данных блока ввода-вывода; блок ввода-вывода дополнительно содержит второй модуль оперативной памяти, вход данных которого подключен к второму входу данных блока ввода-вывода, выход данных которого образуют объединенные в многоразрядную шину данных выходы первого и второго модулей оперативной памяти; первый блок индикации дополнительно содержит знакосинтезирующий индикатор, входы которого подключены к соответствующему разряду входа блока индикации.

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Диагностический молоток | 1956 |

|

SU108854A1 |

| DE 102007029037 A1, 24.12.2008 | |||

| Устройство для гибки материала | 1974 |

|

SU534274A1 |

Авторы

Даты

2013-09-20—Публикация

2012-03-29—Подача