Изобретение относится к области автоматического регулирования и управления средствами вычислительной техники.

Известны устройства для сравнения двух последовательностей импульсов различных частот, в которых величина, пропорциональная разности двух частот, получается в реверсивном счетчике в виде цифрового кода.

Предложенное устройство отличается тем, Что в нем сравнение двух последовательностей импульсов различных частот осуществляется с помощью схем взаимной блокировки.

Это позволяет упростить схему и повысить точность работы.

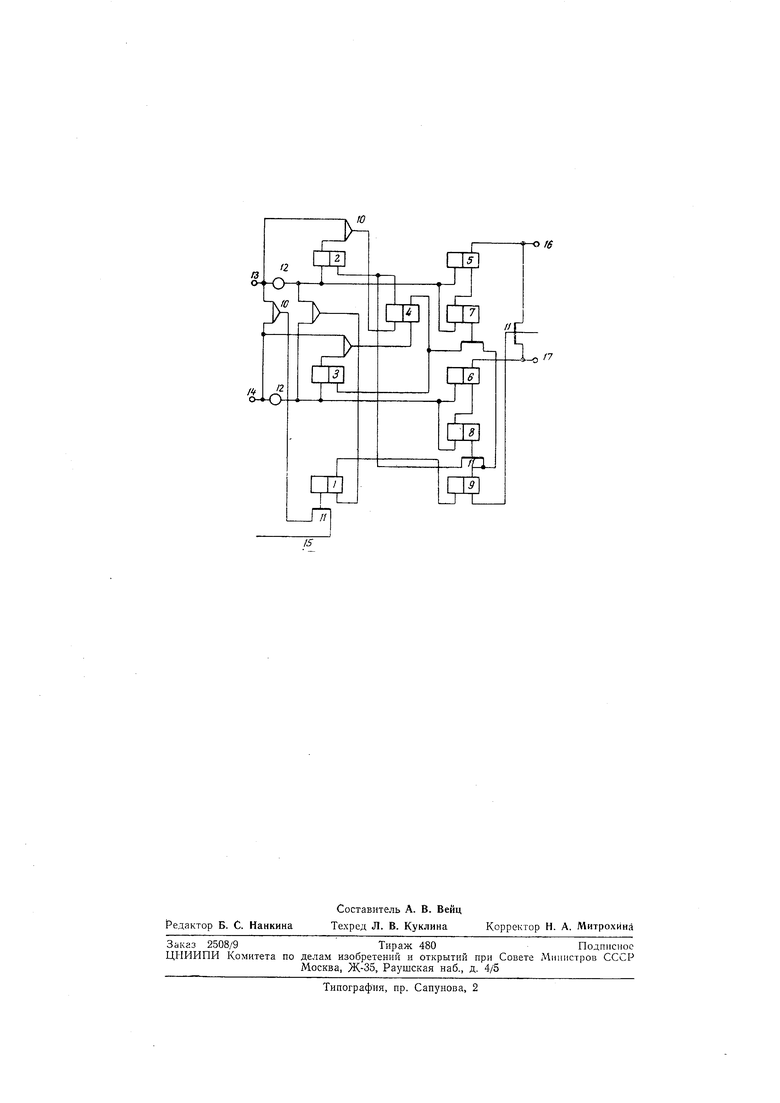

Схема устройства изображена на чертеже.

Устройство содержит динамический триггер 1 деблок-ировки, входные триггеры 2 vi 3, триг.гер-коммутато,р 4, выходные триггеры 5 к 6, управляющие триггеры 7 и 5, триггер 9 блокировки выхода, схемы «И 10, «ИЛИ //, инверторы 12, входы 13 и М сравниваемых сигйалов, вход «сброса 15 и выходы 16 и 17.

Входной триггер 2 и схема «И, связанная с выходом этого триггера, образуют формирователь импульса, охваченный обратной связью через триггер 4. Если в момент времени, предшествующий появлению импульса на входе 13, триггер 4 находится в положении 1, то триггер 2 - в положение О, так как на его единичном входе, связанном с нулевым выходом

триггера 4, сигнал отсутствует. В момент появления импульса на входе 13 -сигнал с нулевого входа триггера 2 -снимается, но триггер продолжает находиться в положении 0. Срабатывает с.хема «PI, с выхода которой сигнал поступает на нулевой вход триггера 4. Триггер 4 перебрасывается в нолол :ение О, срабатывает триггер 2, который устанавливается в положение 1 и закрывает схему

«И 10.

Если на вход 13 приходит еще один импульс, то снимается потенциал на выходе инвертора 12 и, следовательно, на нулевых входах триггеров 7 и 5. Но поскольку сигнал блокйровки выхода отсутствует, т. е. потенциал на единичном входе триггера 7, на нулевом выходе триггера 7 потенциал сохраняется. При этом появится потенциал на единичном выходе триггера 5. Таким образом, начнется

формирование выходного импульса, который окончится с исчезновением импульса «а входе 13.

Если в промел утке между двумя Импульсами, приходящими на вход 13, появится импульс на входе 14, то триггером 3 и связанной С его выходом схемой 10 формируется импульс, возвращающий триггер 4 в то состояние, в котором он находился до прихода первого импульса на вход 13. Поэтому следуюза импульсом, постуяившим на вход 14, не формирует выходного сигнала, а перебрасывает триггер 4 в то состояние, в котором он находился после прихода первого импульса на вход 13.

Для исключения .воЗНикновен.ия на выходе устройства группы импульсов из-за временных задерлсек в элементах устройства и неидеальной формы имлульсов предусмотрена блокиро;в,ка выхода, -отключающая его и деблокирующая по признаку измеления фазы одного входного импульса .относительно другого. При -появлении любого выходного имлульса триггер 9 блокировки иеребра-сывается по единичному входу через ячейку «ИЛИ 11. С единичного выхода этого триггера потенциал подается на единичные входы триггеров 7 и 8, управления, которые удерживаются в состоянии, .препятствующем формирова.нию выходных импульсов триггерами 5 и 6.

Деблокировка триггера 9 происходит в случае, когда входные импульсы на входах 13 и 14 не совпадают во времени. При этом выходные импульсы ячейки «И 10 совпадения пауз, входы которой Связаны со вхолаии 13 и 14, являются запускающими и тактовыми для динамического триггера / деблокировки выхода. Триггер / взводится первым им.пульсом совпадения пауз и воспроизводит на выходе все последующие импульсы. Однако, если последует имлульс от ячейки «И 10 совпадения импульсов, входы которой связаны с выходами -инверторов 12, то триггер / возвратится в исходное положение.

Для предотвращения прохода первого входного имлульса на выход устройства .предусмотрены входы 15 для ко.манды «Сброс, которая через триггер 9 бло кирует триггеры 5 и 6 и сбрасыва.ет тр итгер 1 в состо-я-ние, препятствующее появлению на его выходе первого импульса «совпадение пауз.

Предмет изобретения

У|от ройат во для сравя1ен ия двух пюследовательностей импульсов различных частот, содержащее статические триггеры, динамический триггер и ячейки типа «И, «ИЛИ, «НЕ, отличающееся тем, что, с целью упрощения .схемы и .повышения точности работы, щины сравниваемых частот связаны со входами .соответствующих инверторов входного сигнала, входных ячеек «И и ячейки «И совпадения импульсов, выход каждого -инвертора связан С нулевыми входами соответствующих ему

входных, выходных и управляющих триггеров и с одним из входов ячейки «И совпадения пауз, единичный вход одного из входных триггеров соединен с выходом триггера-коммутатора, связанным также -с одним

из входов ячейки «ИЛИ блокировки одного из выходов, а единичный вход второго входного триггера - с единичным выходо-м триггера-коммутатора, также связанным с одним из входов ячейки «ИЛИ б.локиров.ки второго

выхода, нулевой выход каждого вх-одного триггера связан со вторым входом соответствующей ему ВХОДНОЙ ячейки «И, выход входной ячейки «И, -соответствующий .первому входному триггеру, связан с нулевым входом

триггера-коммутатора, а выход второй вход-ной ячейки «И - с единичным входом того же триггера, выход ячейки «И совпадения импульсов связан со входом ячейки «ИЛИ деблокировк-и выхода, выход которой соединей с нулевым входом триггера деблокировки

выхода, единичный вход которого связа.н с

выходам ячейки «К совпадения пауз, а едиНИчный выход - .с -нулевым входом триггера

-блокировки выхода, единичный вход которого

соединен с выходом ячейки «ИЛИ блокировки обоих выходов, а единичный выход - со вторыми входами я-чеек «ИЛИ блокировки первого и второго выхода, выход каждой из которых -связа-н с единичным входом соответ1ствую:щего ей управляющего триггера, а нулевой выход каждого из этих триггеро.в соединен с единичным входом соответствующего ему выходного триггера, единичный выход каждого -из кото.рых -связа-н с одним из входов

ячейки «ИЛИ блокировки обоих выходов и явля-ется выходной шиной устройства.

о 16

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИКЛИЧЕСКИЙ ИНДИКАТОР ОТКАЗОВ | 1969 |

|

SU243683A1 |

| КВАРЦЕВЫЕ ЧАСЫ ДЛЯ ВРЕМЕННОЙ РЕГИСТРАЦИИ | 1973 |

|

SU367408A1 |

| УСТРОЙСТВО для ИССЛЕДОВАНИЯ потоков ПЕРЕСЕЧЕНИЙ | 1972 |

|

SU358705A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU383085A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ГРУППОЙ ШАГОВЫХ ЭЛЕКТРОДВИГАТЕЛЕЙ | 1971 |

|

SU424288A1 |

| Формирователь импульсов | 1981 |

|

SU1045371A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1972 |

|

SU355723A1 |

| Формирователь синхронизированных импульсов по фронту и спаду | 1982 |

|

SU1115211A1 |

| Распределитель импульсов | 1978 |

|

SU771873A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ЗАКОНА УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ | 1969 |

|

SU255659A1 |

Авторы

Даты

1970-01-01—Публикация