Изобретение относится к области автоматики и вычислительной техники и может быть использовано в качестве формирователя сигналов управления и синхронизации в системах обработки информации. Известны распределители, содержащие триггеры, логические элементы и управляющее устройство l. Их недостаток - невозможность бло кирования кода настройки в процессе работы. Кроме того, .известны распределители импульсов, .содержащие триггеры по числу разрядов, элементы И ввода и опроса, дешифратор, причем первые входы элементов И ввода подключены к клеммам кода настройки, вторые входы объединены и подключены к шине записи, а выходы соединены со входами со ответствующих триггеров, первые вход элементов И опроса объединены и подключены к шине тактовых импульсов 2 Их недостаток состоит в том, что эти устройства не позволяют осуществлять прерывания заданной кодом настройки программы и проводить ее кор рекцию в процессе распределения. Цель изобретения - расширение фун-. кциональных возможностей распределителя импульсов. Цель достигается тем, что в распределитель импульсов, содержащий входные элементы И, первые входы которых соединены с входными шинами, а выходы - с первыми входами соответствующих разрядных треггеров, выходные элементы И и дешифратор, введены дополнительные триггеры, элементы И, ИЛИ, 2И-2ИЛИ, инверторы и комг гутатор,причем единичные выходы каждого разрядного триггера соединены с первыми входами соответствующих выходных элементов И, вторые входы которых подключены к выходу первого элемента И, а выходы - к выходным шинам, ко входам коммутатора и к вторым входам соответствующих разрядньох триггеров, нулевые выходы которых соединены с третьими,четвертыми и пятыми входами выходных элементов И последующих разрядов и входами дешифратора, при этом выход последнего подключен к первому входу первого элемента ИЛИ, второй вход которого соединен со вторыми входами входных элементов И и выходом второго элемента И, первый

вход которого подключен к выходу первого элемента ИЛИ и через первый инвертор к первому входу первого элемента И, а второй - к первому входу третьего элемента И и выходу элемент 2И-2ИЛИг первый, второй, третий, подключенный через второй инвертор, и четвертый входы которого соединены с соответствующими шинами управления при этом четвертый вход элемента 2Й-2ИЛИ подключен к первому входу четвертого элемента И и второму входу первого элемента И, третий вход которого соединен с единичным выходом первого дополнительного триггера, его- нулевой выход подключен ко второму входу третьего элемента И, выход которого соединен с первым входом упомянутого триггера, а его второй вход соединен с выходом второ го элемента ИЛИ, первый вход которого подключен к первому входу третьег элемента ИЛИ, а второй вход - к выходу коммутатора и первому входу пятого элемента И, второй вход которого соединен с другой управляющей шиной, при этом выход пятого элемента И подключен к первому входу второго дополнительного триггера, второй его вход соединен с выходом третьего элемента ИЛИ и третьими входами разрядных триггеров, кроме того, нулевой выход второго дополнительного триггера соединен с управляющим входом дешифратора, а единичный выход - со вторым входом четвертого элемента И, выход которого подключен ко второму входу третьего элемента ИЛИ.

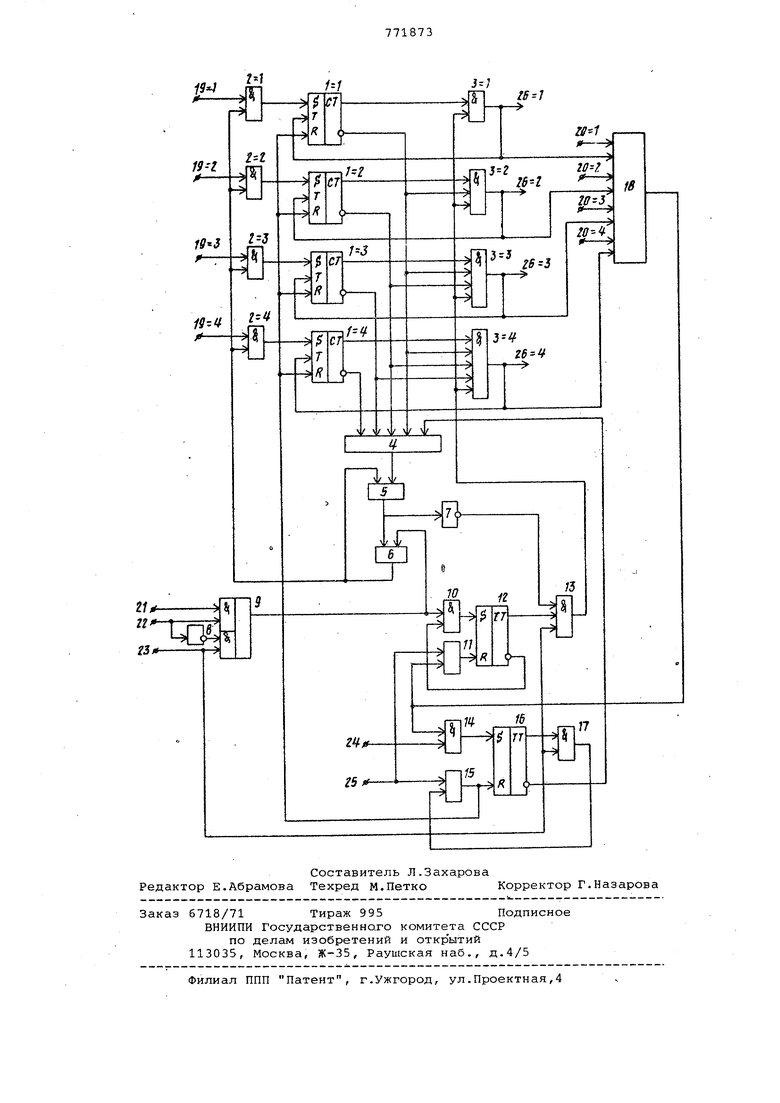

На чертеже представлена функциональная схема распределителя.

Распределитель содержит разрядные триггеры , элементы и , дешифратор 4, элемент ИЛИ 5, элемент И б, инверторы 7,8, элемент 2И-2ИЛИ 9, элемент И 10, элемент, ИЛИ 11, триггер 12, элемент И 13,14, элемент ИЛИ 15, триггер 16, элемент И 17, коммутатор 18, входные шины , шины управления коммутатором, шины 21-25 управления соответственно импульсом пуска режимом работы, тактовых импульсов, разрешением сброса прерывания и начального сброса, выходные шины 26 1-26 4.

Устройство работает следующим образом.

Перед началом работы подается импульс .начального сброса на шину 25. Импульс сброса через элементы ИЛИ 11 15 устанавливает в нулевое состояние триггеры распределителя по переднему фронту, а триггеры 12,16 - по заднему фронту импульса. При этом ка выходе дешифратора 4 формируется единичный потенциал, который через элементИЛИ 5 поступает на вход элемента И б, разрешая прохождение сигналов на входы элементов И . На вход элемента И 13 поступают нулевые потенциалы с выхода инвертора 7 и триггера 12, запрещающие (блокирующие) прохождение импульсов тактовой частоты на входы выходных элементов И , а нулевой потенциал с выхода триггера 16 блокирует прохождение импульсов через элементы И 17 и ИЛИ 15 на сброс триггеров распределителя. При установке на шине 22 единичного потенциала распределитель работает в ждущем режиме: в. этом случае через элемент 2И-2ИЛМ 9 проходит импульс пуска с шины 21, а при установке нулевого потенциала в циклическом режиме, в этом случае через элемент 2И-2ИЛИ 9 проходят импульсы тактовой частоты с шины 23.

Рассмотрим ждущий режим работы рапределителя импульсов.-Поданный на шину 21 импульс пуска, синхронный с импульсом тактовой частоты, поступает через элементы 2И-2ИЛИ 9 и И б на входы элементов И и осуществляет запись кода настройки (программы) с шин в триггеры распределителя по своему переднему фронту, а поступая с выхода элемента И б на вход элемента ИЛИ 5, поддерживает на ее выходе единичный потенциал на время существования импульса записи, тем самым обеспечивая наличие всего импульса на шине записи, осуществляя надежную запись кода настройки. Потенциал с выхода элемента ИЛИ 5 через инвертор 7 блокирует прохождение импульсов тактовой частоты на опрос распределителя при наличии программы в триггерах 1 , равной нулю, и на время записи кода настройки. Импульс с выхода элемента 2И-2ИЛИ 9 поступает также на вход элемента И 10 и при наличии разрешения на ее втором входе проходит на S-вход триггера 12, устанавливая его в единичное состояние по заднему фронту импульса.

По окончании импульса пуска наличии кода настройки, отличного от нуля, на входе элемента И б появляется нулевой потенциал, блокирующий изменение программы р.аспр.еделителя, а на входе элемента И 13 формируются единичные потенциалы, разрешающие прохождению импульсов тактовой частоты на опрос распределителя импульсов .

В этом случае импульс тактовой частоты с шины 23, поступая на входы элементов И через элемент И 13,формирует выходной импульс лишь на выходе элемента И , разряд триггера которого находится в единичном состоянии, так как элементы И 3 всех предьщущих каналов блокированы нулевыми потенци-элами с прямьтх выходов триггеров 1 соответствующих разрядов, а все элементы И 3

йоследующих каналов блокированы нулевым потенциалом с инверсного выхода триггера 1 данного разряда. Импульс с выхода элемента И 3 поступает на выходные шины и на счетный вход соответствующего триггера 1, переключая его задним фронтом в нулевое состояние.

При нулевом значении кода прерывания, поступающего на шину 20,блокировано прохождение импульсов с выхода элементов 3 на входы коммутатора 18,

Второй импульс тактовой частоты формирует выходной импульс на выходе элемента И следующего значащего канала, выходной импульс поступает на шину и .на счетный вход соответствующего триггера 1, переключая его задним фронтом в нулевое состояние и т.д.

Таким образом устройство распределяет импульсы тактовой частоты в соответствии с заданным кодом настройки .

Окончание выполнения программы, заданной кодом настройки, определяется по нулевому состоянию всех триггеров распределителя с помощью дешифратора 4 нуля. При-нулевом состоянии всех триггеров 1 распределителя и триггера 16 на выходе дешифратора 4 нуля формируется единичный потенциал, поступающий через элемент ИЛИ 5 на вход элемента И 6, деблокируя прохождение импульсов на запись, а через элемент ИЛИ 5 и инвертор 7 - на вход элемента И 13, блокируя прохождение импульсов на опрос. При этом следующий импульс пуска, поступаюодий на шину 21, установит в триггеры распределителя новый код настройки с шин , и процесс работы распределителя повторится.

Для установки циклического режима работы распределителя импульсов необходимо осуществить смену потенциала на шине 22 с единичного на нулевой, синхронно с задним фронтом импульсов тактовой частоты. При этом на выход элемента 9 2И-2ИЛИ будут поступать импульсы тактовой частоты, прохождение которых на шину записи ерез элемент И 6 блокировано при наличие ненулевой программы в триггерах распределителя. При выполнении программы (все триггеры 1 распределителя в нулевом состоянии) единичный потенциал с выхода дешифратора 4 нуля деблокирует прохождение сигналов на запись, а через инвертор 7 блокирует прохождение их на опрос. Следующий импульс проходит на запись нового кода настройки с шин в триггеры . По заднему фронту импульса записи на выходе дешифратора 4 нуля формируется нулевой потенциал, который через элементы ИЛИ 5 и инвертор 7 осуществит блокировку элемента И 6 и деблокировку элемента И 13 на прохождение импульсов тактовой частоты. Дальнейшая работа аналогична вьпиеописанной.

При ненулевом значении кода прерывания импульс с выхода элементов проходит через соответствующий канал коммутатора 18 на его выход, а с выхода через элемент ИЛИ 11 на R-вход триггера 12, устанавливая его

0 в нулевое состояние по згзднему $ронту импульса. При этом нулевой потенциал с прямого выхода триггера 12 блокирует прохождение импульсов тактовой частоты на опрос распределителя,

5 а единичный потенциал с инверсного выхода деблокирует элемент И 10. Таким образом происходит прерывание в выполнении программы.

При ждущем режиме работы продолжение выполнения программы осуществ0ляется после прихода очередного импульса пуска на шину 21. Импульс пуска, проходя через элементы 2И-2ИЛИ 9 и 10, поступает на S-вход триггера 12, устанавливая его в единичное со5стояние по заднему фронту. Происходит деблокировка элемента И 13, и импульсы тактовой, частоты проходят на опрос программы распределителя. При циклическом режиме работы триг0гер 12 установится в единичное состояние по заднему фронту следующего после выполнения команды прерывания импульса тактовой частоты.

Следовательно,при задании кода

5 прерывания, не равного нулю, осуществляется прерывание в выполнении заданной rtpoгpa 1мы распределения импульсов на время до следующего импульса пуска в ждущем режиме и на один период тактовой частоты в ци1с0лическом режиме работы.

При задании ненулевого кода прерывания на изины 20 и единичного потенциала на шину 24 импульс с выхода коммутатора 18 поступает через эле5мент И 14 на S-вход триггера 16, устанавливая его в единичное состояние по заднему фронту. В этом случае единичный потенциал с прямого выхода триггера 16 деблокирует элемент И 17

0 на прохождение импульсов тактовой частоты, а нулевой потенциал с инверсного выхода треггера 16 поступает на дополнительный вход дешифратора 4 нуля,- поддерживая на его выходе

5 нулевой потенциал на время своего существования. Импульс с выхода коммутатора 18, одновременно поступая на R-вход триггера 12 через элементы ИЛИ 11, обеспечивает прерывание в выполнении nporpaMNM (блокировка О1и0ны опроса).Следующий импульс тактовой частоты с шнны 23 проходит на выход элемента И 17, а с ее выхода через элемент ИЛИ 15 - на R-входы триггеров распределителя. устанавливая их в нулевое состояние по переднему фронту, и на R-вход триггера 16, устанавливая его в нулевое состояние по заднему фронту импульса. По окончании импульса сбро са деблокируется элемент И 17, и на дополнительный вход дешифратора 4 нуля поступает разрешающий (единичный) сигнал. Следовательно, при задании единичного потенциала на шину 24 происходит сброс программы при выполнении команды прерывания. Рабо та по выполнению команды прерывания аналогична вышеописанной. Таким образом, распределитель импульсов позволяет осуществлять по соответствующим командам прерыва ние в выполнении программы с последующим продолжением либо изменение циклического выполнения программ бе использования специального импульса пуска, что расширяет его функционал ные возможности в формировании и распределении импульсов. Формула изобретения Распределитель импульсов, содержащий входные элементы И, первые входы которых соединены с входными шинами,а выходы - с первЕлми входами соответствуюгдих разрядных триггеров выходные элементы И и дешифратор, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дополнительные триггеры, Элементы И, ИЛИ 2И-2ИЛИ, инверторы и коммутатор,, причем единичные выходы каждого раз рядного триггера соединены с первыми входами соответствующих выходных элементов И, вторые входы которых подключены к выходу первого элемента И , а выходы - к выходным шинам, ко входам коммутатора и к вторым входам соответствующих разря цных триггеров, нулевые выходы которых соединены с третьими, четвертыми и пятыми входами выходных элементов И последующих разрядов и входами дешифратора, при этом выход последнего подключен к первому входу первого элемента ИЛИ, второй вход которого соединен со вторыми входами входных элементов И и выходом второго элемента И, первый вход которого подключен к выходу первого элемента ИЛИ и через первый инвертор - к первому входу первого элемента И, а второй к первому входу третьего элемента И и выходу элемента 2И-2ИЛИ, первый, второй, третий, подключенный через второй инвертор, и четвертый входы которого соединены с соответствующими шинами управления, при этом четвертый вход элемента 2И-2ИЛИ подключен к первому входу четвертого элемента И и второму входу первого элемента И, третий вход которого соединен с единичным выходом первого дополнительного триггера, его нулевой выход подключен ко второму входу третьего элемента И, выход которого соединен с первым входом упомянутого триггера, а его второй вход соединен с выходом второго элемента ИЛИ, первый вход которого подключен к первому входу третьего элемента ИЛИ, а второй вход - к выходу ко1 1мутатора и первому входу пятого элемента И,второй вход которого соединен с другой управляющей шиной, при этом выход пятого элемента И подключен к первому входу второго дополнительного триггера, второй его вход соединен с вЕлходом третьего элемента ИЛИ и третьими входами разрядных триггеров, кроме того, нулевой выход второго дополнительного триггера соединен с управляющим входом дешифратора, а единичный выход - со вторым входом четвертого элемента И, выход которого подключен ко второму входу третьего элемевта ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 432480, кл. G 06 F 1/04, 1970. 2.Авторское свидетельство СССР № 581594, кл. Н 04 L 13/14,25.08.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для тренировки памяти обучаемого | 1988 |

|

SU1531125A1 |

| Распределитель импульсов | 1975 |

|

SU581594A2 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для контроля распределителя | 1983 |

|

SU1128260A2 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

Авторы

Даты

1980-10-15—Публикация

1978-07-21—Подача