Изобретение предназначено для обнаружения отказов в дискретных системах автоматического управления.

Известны индикаторы отказов, содержащие генератор импульсов, устройство считывания с переключателями и каскадами совпадений; устройство управления со счетчиками, подключенными к триггеру пуска электронного коммутатора, схемой формирования сигнала управления коммутатором и мультивибратором исключения ошибки; электронный коммутатор с многоканальной диодной матрицей, усилителями сигнализации с триггерами; устройство обработки информации со схемой выработки квазистробирующих имлульсов, схемой слежения за работой проверяемого элечмента, цепью формирования сигнала отказа и счетчиком числа сбоев с усилителями.

Недостатком известных индикаторов является невысокое быстродействие и возможность ложной регистрации отказов.

Предложенное устройство отличается от известных тем, что в нем генератор импульсов через переключатели и каскад совпадения соединен со счетчиком устройства управления, а выход счетчика соединен через триггер пуска с диодной матрицей и через переключатель параллельными связями - со схемой формирования сигнала управления коммутатором, который через каскад совпадения соединен с

триггером разрешения считывания информации и с мультивибратором исключения ошибки, через переключатель, связанным с каскадом совпадения устройства обработки информации. Схема формирования сигнала управления коммутатором подключена к двум последовательно соединенным триггерам, выход последнего из которых подсоединен к диодной матрице, нагруженной через переключатель

на каскад совпадения устройства считывания информации И усилители сигнализации. Схема выработки квазистробирующих импульсов соединена со схемой слежения за работой проверяемого триггера цепью формирования сигнала отказа триггеров разрешения (или запрета) съема информации и счетчиком числа сбоев.

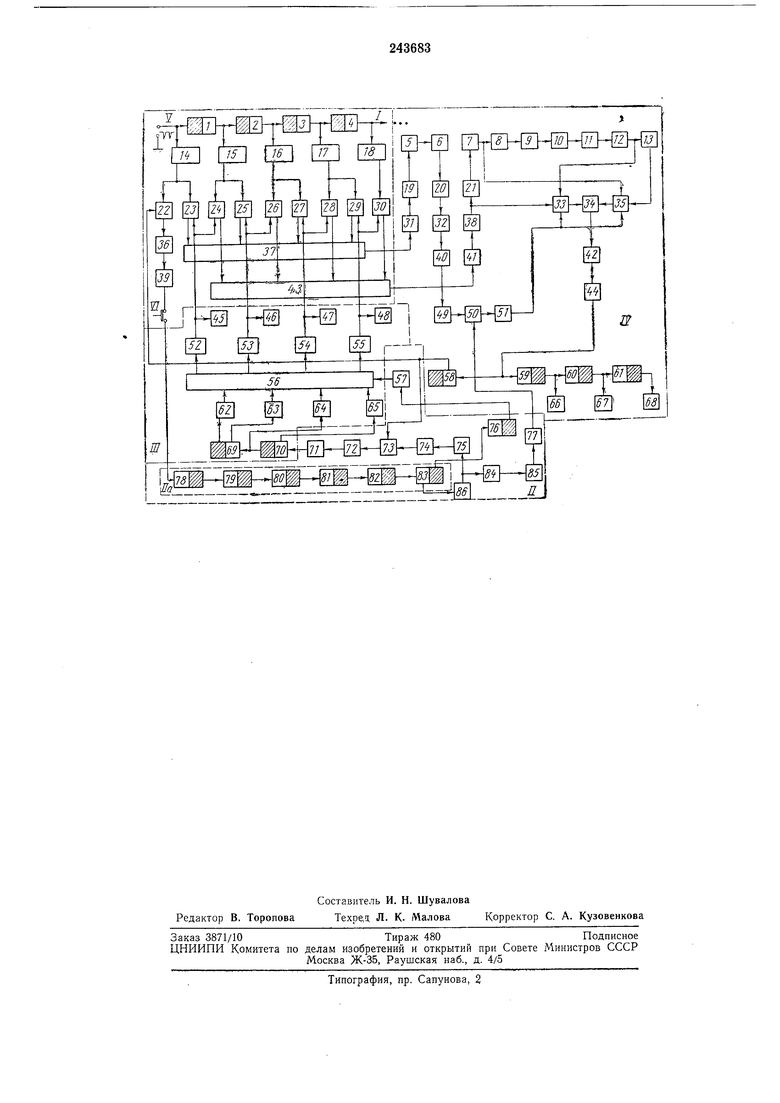

Это позволяет автоматизировать и ускорить процесс регистрации отказов и сбоев в многоэлементной дискретной системе, задать время проверки каждого элемента, исключить ложный отказ и упростить фиксацию отказавших элементов. На чертеже представлена блок-схема индикатора.

Циклический индикатор отказов состоит из четырех функционально различаемых устройств: устройства считывания информации /, устройства управления // со счетчиком Па,

обработки информации IV. Кроме того, имеется генератор импульсов V и ключ нуска VI Первое устройство считывает состояния проверяемых триггеров на их входах и выходах. Второе - задает временной интервал ироверки счетом входных импульсов и исключает ошибку индикатора при переходе с проверки одного триггера на проверку другого. Электронный коммутатор вырабатывает сигналы, определяющие очередность проверки триггеров и фиксирует отказавший триггер. Четвертое устройство воспринимает информацию с выхода первого и, обрабатывая ее, выдает сигнал отказа; при наличии такового, определяет число тактов, пропущенных отказавш-им триггером и останавливает индикатор на проверке отказавшего триггера.

Кроме того, на схеме приняты следующие обозначения; 1-4 - триггеры проверяемой схемы, 5 - переключатель, и 7 - инверторы, 8 - переключатель, 9 - линия задержки, W - переключатель, 11 - инвертор, 12 - переключатель, 13 - инвертор, 14-18 - переключатели, 19 - инвертор, 20, 21 - переключатели, 22-30 - каскады совпадения, 31 - переключатель, 32 - линия задержки, 33 - каскад совпадения, 34 - каскад логического сложения (сборка), 35 - каскад совпадения, 36-переключатель, 37- каскад логического сложения, 38 тл 39 - инверторы, 40, 41 -л 42 - переключатели, 43 - каскад логического сложения, 44 - инвертор, 45-48 - усилители сигнализации, 49 - блокинг-генератор, 50 - каскад совпадения, 51-55 - переключатели, 56 - диодная матрица, 57 - переключатель, 58-61 - триггеры, 62-65 - переключатели, 66-68 - усилители сигнализации, 69-70 - триггеры, 71 - инвертор, 72 - переключатель, 73 - каскад совпадения, 74 - переключатель, 75 - линии задержки, 76 - триггер, 77 - инвертор, 78-83 - триггеры, 84 - мультивибратор, 85-86 - переключатели.

Входные для проверяемой системы импульсы с выхода источника их (генератора импульсов У) поступают через переключатель 14 одновременно на каскады совпадения 22 и 23. Каскад 22 управляется отрицательяььм потенциалом, снимаемым с триггера остановки индикатора. При наличии этого управляющего потенциала входные импульсы одновременно с поступлением на вход триггера 1 проверяемой схемы подаются через блоки 22, 36, инвертор 39, замкнутый ключ VI (он стоит в положении «Пуск) в счетчик числа импульсов устройства управления. Эти импульсы имеют положительную полярность.

Блоки 23 и 24 управляются отрицательным потенциалом, снимаемым с соответствующего выхода диодной матрицы схемы электронного коммутатора через блок 52. Этот потенциал является сигналом, «разрешающим съем информации со входа триггера через каскад 23 на каскад логического сложения (сборку) 37, а с выхода триггера / через блоки 15 и 24 на сборку 43.

Разрешающий сигнал приходит на блоки 23 и 24 при ироверке триггера. При последующей проверке триггеров аналогичные сигналы последовательно после просчета входных импульсов счетчиком в схеме управления приходят соответственно на каскады совпадения 25; 26 и 27; 28 и 29; 30 и 23; 24, 25 я 26 и т. д. Сигналы со входа и выхода проверяемого триггера через каскады 37 и 43 подаются в

устройство обработки информации.

В устройство управления // входят следуюЩИе основные элементы: счетчик числа входных импульсов (триггеры 78-83), триггер 76 пуска электронного коммутатора, схема формирования импульсов управления электронным коммутатором (на элементах 86, линии задержки 75, блоках 74, 73, 72, 71) и мультивибратор 84 исключения ошибки. При включении ключа VI (положение

«Пуск) входные импульсы, инвертированные в устройстве считывания информации, поступают на первый триггер 78 счетчика числа импульсов. При заполнении счетчика положительный

импульс с его выхода возбуждает триггер пуска электронного коммутатора 76, который через блок 57 выдает управляющий потенциал на диодную матрицу электронного коммутатора. Одновременно отрицательным фронтом импульса со второго выхода триггера 83 через блок 86 запускается схема формирования сигналов управления электронным коммутатором при условии, что на каскад 73 подан с триггера 58 остановки индикатора (устройства обработки информации) отрицательный управляющий потенциал. С каскада 73 импульсы, задержанные в линии задержки 75, проходят через блок 72 и 71 н далее по линии на триггер 70 электронного коммутатора.

Мультивибратор 84 исключения ошибки предназначен для управления блоком 50 (устройства обработки информации), через который проходят квазистробирующие импульсы на блоки 55 и (35 с блокинг-генератора 49

(блоки 50, 33, 35, 49 - элементы устройства обработки информации).

При проверке данного триггера (время проверки определяется временем заполнения счетчика импульсов) мультивибратор 84 находится в нулевом невозбужденном состоянии и блок 50 оказывается открытым отрицательным напряжением. После того как проверка триггера заканчивается, мультивибратор 84 возбуждается через блок 86 и выдает отрицательный импульс. В результате этого блок 50 оказывается запертым положительным импульсом. Это делается для того, чтобы исключить появление ложного сигнала отказа при переходе с проверки одного триггера на проверку

другого.

Действительно, при проверке /С-го триггера ювазистробирующие импульсы блока 49 вырабатывались 1ПО отрицательным фронтам входных для него импульсов. Пусть в момент оконрялся /С-ый триггер, он оказался в состоянии «О на входе (левая половина открыта) и «1 на выходе (правая половина закрыта). Тогда при переходе на проверку триггера /C+l может запуститься блок 49 отрицательным фронтом импульса, возникающего при подаче сигнала разрешения съема информации триггера /С+1, так как теперь на входе цепи формирования Импульса запуска блока 49 возникает перепад напряжения, а триггер /С+1 будет находиться еще в исходном состоянии, т. е. не перебросится. При этом может возникнуть сигнал отказа. Чтобы этого не случилось, после окончания проверочного цикла импульсом запускается мультивибратор 84, запирающий через блоки 85 1И 77 каскад 50. Квазистробирующий импульс с блока 49 теперь через каскад 60 не проходит, и ложный сигнал отказа выработан не будет.

Электронный коммутатор /// содержит триггеры команд проверки 69 и 70, дешифратор - диодную матрицу 56 и устройство индикации отказа.

Командные трнггеры запускаются положительными фронтами импульсов, поступающих из устройства управления. На триггерах 69 и 70 собран двоичный счетчик. Предположим, что в исходном состоянии счетчик очищен, при этом потенциал с правой половины триггера 70 через блок 5 подается на первую и третью, а с правой половины триггера 69 через блок 63 на первую и вторую выходные шины дешифратора. Будем считать, что к этому исходному состоянию счетчик имлульсов (устройства управления) заполнен и последний имнульс предыдущего цикла перебросил триггер пуска 76 в состояние, в котором в дещифратор через блок 57 поступает отрицательный потенциал, подготавливающий дешифратор к работе.

Таким образом, при наличии разрещающего импульса с триггера пуска 76 в исходном состоянии командных триггеров 69 и 70 на первой шине дещифратора вырабатывается команда проверки первого триггера проверяемой схемы. Эта команда через блок 52 подается на блок 23 и 24 устройства считывания информации. Под проверкой окажется первый триггер. 64-м импульсом, очищающ-им счетчик входных импульсов, задержанным в линии задержки 75, триггер 70 переводится в состояние «1, в котором отрицательный потенциал будет уже сниматься с его левой половины и проходить через блок 64 на вторую и четвертую шипы дешифратора. Так как триггер 69 остается еще в исходном состоянии то теперь возникает команда проверки второго триггера проверяемой схемы на второй шине дешифратора, а команда на первой шипе исчезнет.

Команда со второй шины дешифратора 56 через блок 53 пройдет на блок 25 и 26, т. е. подключит для проверки второй триггер проверяемой схемы. Второй триггер будет находиться под проверкой время

где Г зап-время заполнения счетчика входных импульсов; Гл.э -время задержки. После заполнения счетчика входных импульсов в цикле проверки второго триггера через Гл.з в командных триггерах будет зафиксировано число 3. Это вызовет переход на проверку третьего триггера и т. д. Нетрудпо видеть, что работа ипдикатора может начаться с проверки любого триггера.

При обнаружении отказа устройством обработки информации индикатор останавливается в положении проверки отказавшего триггера, что фиксируется загоранием сигнальной лампы на выходе соответствующего усилителя сигнализации 45-48.

Устройство обработки информации IV включает в себя схему выработки квазистробирующих импульсов (блоки 31, 19, 5, 6, 20, 32, 40,

49), схему слежения за работой проверяемого триггера (блоки 41, 38, 21, 7, 8, 9, 10, 11, 12, 13, 33, 35, 34), цепь формирования сигнала отказа (блоки 42, 44, триггер 55 остановки индикатора, счетчик числа сбоев с усилителями

сигнализации (блоки 59, 60, 61, 66, 67, 88).

При поступлении с блока 37 устройства считывания информация входного для проверяемого триггера импульса схема формирования квазистробирующего импульса отрицательным

фронтом его запускает блок 49. Линия задержки 32 в этой схеме сдвигает квазистробирующие импульсы на величину задержки, при которой исключается влияние на ее работу фронтов импульсов. Наличие многоэлементной

цепи формирования квазистробирующих импульсов объясняется необходимостью исключить запуск блока 49 щумовыми сигналами на выходе блока 37. Так как в течение времени проверки триггера на блок 50 подается отрицательный потенциал с мультивибратора 84, отрицательный импульс блока 49 проходит через блоки 50 и 51 на каскады 33 и 55. С каскада 43 снимаются выходные импульсы проверяемого триггера. Эти импульсы через схему слежения подаются на каскады 33 и 35 соответственно.

Линия задержки 9 сдвигает выходные импульсы проверяемого триггера, исключая тем самым появление ложного сигнала отказа при

безотказной работе его. Действительно, пусть при безотказной работе проверяемого триггера на блок 4 приходит отрицательный фронт его выходного импульса. Тогда с блока 39 пойдет положительный фронт, с блока 7 отрицательный, после линии задержки 9 - отрицательный, но задержанный, после блока 11 - положительный. Таким образом, блок 55 для квазистробирующего импульса оказывается запертым нулевым потенциалом, имеющимся

на выходе блока 38. Одновременно отрицательным фронтом импульс с блока 7 оказывается приложенным к каскаду 55, а задержанный и дважды инвертированный блоками 11 и 13 импульс с выхода блока 13 запирает

лов33 и 35 при этом образоваться не может. Рассмотрим далее формирование сигнала отказа. Допустим, что на выходе проверяемого триггера в исходном состоянии имеется нулевой потенциал «О. При отказе или сбое триггера этот потенциал «О сохраняется на выходе триггера и после возбуждения его. Следствием отказа или сбоя проверяемого триггера будет появление на выходе блоков 38 и 12 широкого отрицательного импульса (данное состояние схемы является статическим, в нем исключается влияние на прохождение сигналом линии задержки 9). Импульсы с выходов блоков 38 и 12 поступают на два входа каскада 33, поэтому теперь импульсы блока 49 пройдут через блоки 55 и 34 в схему формирования импульса отказа. Если же исходное состояйие на выходе проверяемого триггера характеризуется наличием отрицательного потенциала «1, то это состояние сохраняется при отказе его. Сигнал отказа в этом случае аналогичным образом формируется блоками 7, 13, 35, 49.

.Сигнал отказа с каскада 34 через блоки 42 и 44 подается па триггер 58 остановки индикатора. Последний вырабатывает сигнал запрета прохождения входных импульсов в счетчик числа импульсов, поступающий в устройство считывания информации и в устройство управления на каскаде 75 для исключения ошибки при определении номера отказавшего триггера в том случае, когда его отказ был обнарул ен на последнем импульсе, очищающем счетчик и одновременно переводящем индикатор на проверку следующего триггера.

Время переключения индикатора с проверки одного триггера на проверку другого меньше времени формирования сигнала отказа. Поэтому импульс, переполняющий счетчик, задерживается на выходе счетчика посредством линии задержки, что задерживает переход индикатора па проверку следующего триггера на время, превышающее время выработки сигнала отказа. Для того чтобы 64-й импульс не перевел индикатор на проверку /С-го триггера при обнаружении отказа в К.- триггере, блок 75 запирается сигналом отказа.

Предмет изобретения

Циклический индикатор отказов, содержащий генератор импульсов, устройство считывания с переключателями и каскадами совпадений, устройство управления со счетчиками, подключенными к триггеру пуска электронного коммутатора, схемой формирования сигнала управления коммутатором и мультивибратором исключения ошибки, электронный коммутатор с многоканальной диодной матрицей, усилителями сигнализации с триггерами, устройство обработки информации со схемой выработки квазистробирующих импульсов, схемой слежения за работой проверяемого элемента, цепью формирования сигнала отказа и и счетчиком числа сбоев с усилителями сигнализации, отличающийся тем, что, с целью автоматизации и ускорения процесса регистрации отказов и сбоев в многоэлементной дискретной системе с триггерами задания времени проверки каждого элемента и исключения лолсного отказа при переходе на проверку следующего триггера, формирования сигналов

очередности проверок при упрощении фиксации отказавщих элементов, выработки сигнала отказа, определения числа тактов, пропущенных отказавшим элементом и остановки поисковых движений, в нем генератор импульсов через переключатели и каскад совпадения соединен со счетчиком устройства управления, а выход счетчика соединен через триггер пуска с диодной матрицей и через переключатель параллельными связями - со схемой

формирования сигнала управления коммутатором, который через каскад совпадения соединен с триггером разрешения считывания информации и с мультивибратором исключения ошибки, через переключатель связанным с каскадом совпадения устройства обработки информации, причем схема формирования сигнала управления коммутатором подключена к двум последовательно соединенным триггерам, выход последнего из которых подсоединен к

днодной матрице, нагруженной через переключатель на каскад совпадения устройства считывания информации и усилители сигнализации, а схема выработки квазистробирующих импульсов соединена со схемой слежения за

работой проверяемого триггера цепью формирования сигнала отказа триггеров разрешения (или запрета) съема информации и счетчиком числа сбоев.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Система для контроля монтажа | 1987 |

|

SU1425719A2 |

| РАДИОСТАНЦИЯ | 1995 |

|

RU2141723C1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ СУДОВ | 1991 |

|

RU2042212C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

Даты

1969-01-01—Публикация