Изобретение относится к области измерительной техники и может быть использовано для контроля работы управляющей части релейного коммутатора в информационных системах, предназначенных для измерения сигналов, (Поступающих с большого количества датчиков.

Известные устройства, содержащие логические ячейки типа «ИЛИ, дискриминаторы и исполнительные реле, обеспечивают контроль только постоянных напряжений на всех входах.

Цель изобретения - обеспечить контроль изменяющихся во времени потенциалов.

Достигается это тем, что в предложенном устройстве применены блоки контроля потенциалов как вертикальных, так и горизонтальных шин матрицы и транзисторная схема формирования сигнала неисправности.

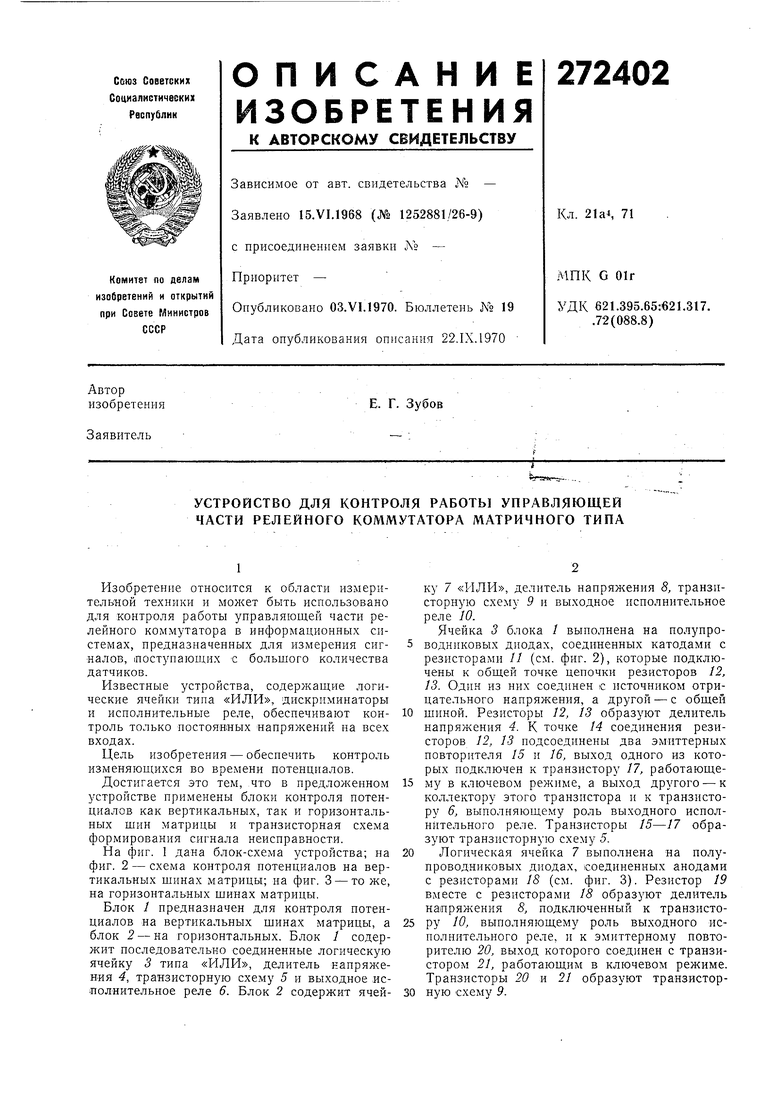

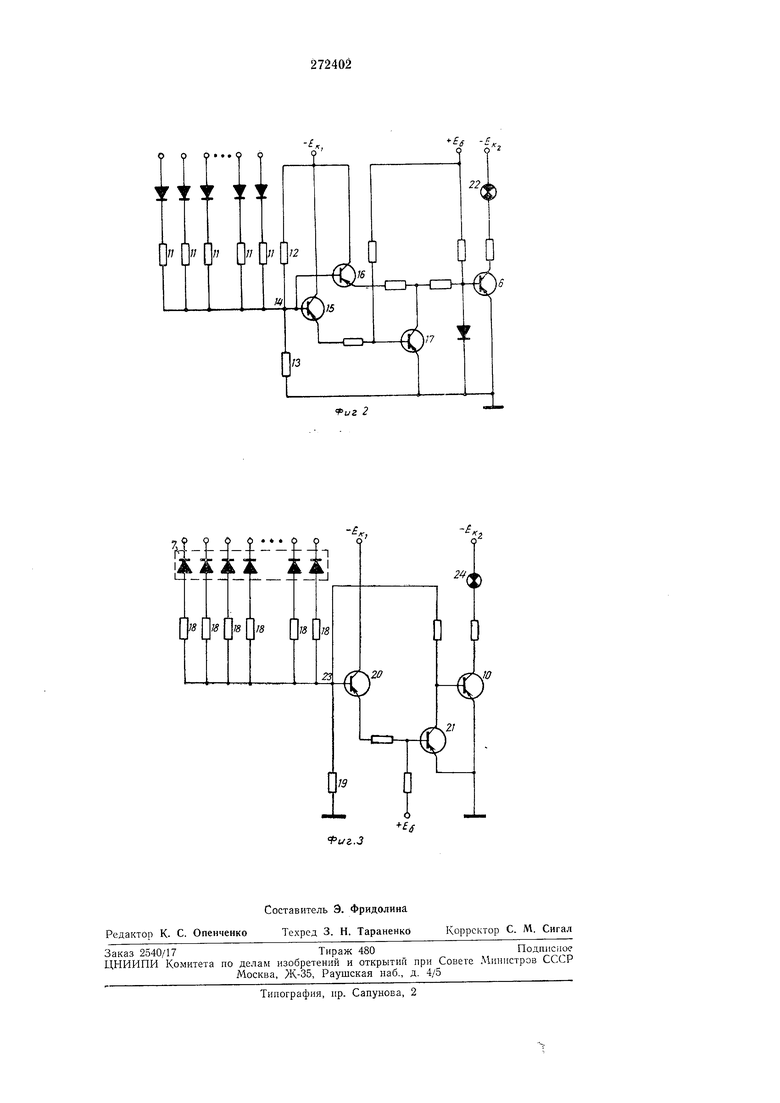

На фиг. 1 дана блок-схема устройства; на фиг. 2 - схема контроля иотенциалов на вертикальных шинах матрицы; на фиг. 3 - то же, на горизонтальных щинах матрицы.

Блок / предназначен для контроля потенциалов на вертикальных щинах матрицы, а блок 2 - на горизонтальных. Блок / содержит последовательно соединенные логическую ячейку 3 типа «ИЛИ, делитель наирял ен-ия 4, транзисторную схему 5 и выходное исполнительное реле 6. Блок 2 содержит ячейку 7 «ИЛИ, делитель напряжения 8, транзисторную схему 9 и выходное исполнительное реле 10.

Ячейка 3 блока / выполнена на полупроводниковых диодах, соединенных катодами с резисторами // (см. фиг. 2), которые подключены к общей точке цепочки резисторов 12, 13. Один из них соединен с источником отрицательного напряжения, а другой - с общей

шиной. Резисторы 12, 13 образуют делитель напряжения 4. К точке 14 соединения резисторов 12, 13 подсоединены два эмиттерных повторителя 15 и 16, выход одного из которых иодключен к транзистору 17, работающему в ключевом режиме, а выход другого - к коллектору этого транзистора и к транзистору 6, выполняющему роль вы.ходного исполнительного реле. Транзисторы 15-17 образуют транзисторную схему 5.

Логическая ячейка 7 выполнена на полупроводниковых диодах, соединенных анодами с резисторами 18 (см. фиг. 3). Резистор 19 вместе с резисторами 18 образуют делитель напряжения 8, подключенный к транзистору 10, выполняющему роль выходного исиолиительного реле, и к эмиттерному повторителю 20, выход которого соединен с транзистором 21, работающим в ключевом режиме. Транзисторы 20 и 21 образуют транзисторПри номинальном режиме, когда оДин из входов ячейки 3 -имеет нулевой потенциал, а остальные - более низкий потенциал, напряжение в средней точке делителя 4 отрицательное. Транзистор 6 при этом открыт, так как транзистор 17, работающий в ключевом режиме, закрыт. Сигнальная лампочка 22 горит.

Если на всех входах ячейки 3 будет низкий потенциал, то напряжение «а базе эмиттерного повторителя 15 станет более отрицательным, откроется транзистор 17 и зашунтирует вход эмиттерного повторителя 16. Транзистор 6 закроется, и лампочка 22 погаснет, сигнализируя о неисправной работе коммутатора.

Когда «а двух или большем числе входов ячейки 5 потенциал равен нулю, напряжение в точке 14 менее отрицательное, чем при номинальном режиме, транзистор 6 закрывается, и лампочка гаснет.

В случае контроля потенциалов на горизонтальных шинах матрицы коммутатора при .номинальном режиме, когда на одном из входов ячейки 7 (см. фиг. 3) имеется низкий оотенциал, а на других - нулевой, напряжение в точке 23 делителя 8 отрицательное. При этом транзистор 10 открыт, так как транзистор 21, работаюш;ий в ключевом режиме, закрыт. Сигаальная лампочка 24 горит.

Е,сли на двух и более выходах ячейки 7 потенциал низкий, то напряжение на базе эмиттерного повторителя 20 более отрицательное, открывается транзистор 21 и шунтирует резистор 19. Транзистор 10 закрывается, и лампочка 24 гаснет, сигнализируя о неисправной работе Коммутатора.

Когда на всех входах ячейки 7 потенциал нулевой, наиряжение в точке 23 равно нулю, и транзистор 10 закрывается, а сигнальная лампочка 24 гаснет.

Предмет изобретения

1.Устройство для контроля работы уиравляющей части релейного коммутатора матричного типа, содержащее логические ячейки «ИЛИ, выходные исполнительные реле, отличающееся тем, что, с целью контроля изменяющихся во времени потенциалов, оно содержит блоки контроля потенциалов на вертикальных и горизонтальных шинах, каждый из которых соответственно имеет последовательно включенные ячейку «ИЛИ, делитель напряжения, транзисторную схему формирования сигнала неисправности при напряжении на делителе выше или ниже номинального и выходное исполнительное реле.

2.Устройство по п. 1, отличающееся тем, что транзисторная схема каждого из указанных блоков контроля состоит из эмиттерного повторителя, соединенного с ключевым транзистором, а база эмиттерного повторителя соединена С коллектором этого транзистора и входом выходного исполнительного реле, причем блок контроля потенциалов на вертикальных шинах содержит подключенный к делителю напряжения эмиттерный повторитель, соединенный с коллектором ключевого транзи-, стора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автономная система энергоснабжения | 1989 |

|

SU1644357A1 |

| Устройство для индикации напряжения аккумулятора | 1979 |

|

SU864389A1 |

| Селектор уровня постоянного напряжения | 1980 |

|

SU943683A1 |

| Самоконтролирующаяся система электропитания постоянного напряжения | 1981 |

|

SU1001298A1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

| Стабилизированный источник электропитания постоянного напряжения | 1979 |

|

SU769514A1 |

| Реле времени | 1979 |

|

SU826447A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Устройство защиты источника постоянногоНАпРяжЕНия | 1979 |

|

SU845011A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

-i о

2

Даты

1970-01-01—Публикация