Известны аналоговые регистры сдвига, содержащие последовательно включенные ячейки конденсаторной памяти с коммутируемыми в противофазе ключами и буферными усилителями.

Предложенный регистр сдвига отличается тем, что он содержит многообмоточный трансформатор тактовой частоты, начало и конец каждой из вторичных обмоток которого через два последовательно включенных резистора соединены с базами двух усилительно-ключевых транзисторов противоположного типа проводимости, иричем эмиттеры транзисторов через конденсаторные ячейки иамяти соединены со средними точками следующих но номеру вторичных обмоток, а между точками соединения резисторов включено по диоду. Это позволяет упростить конструкцию устройства.

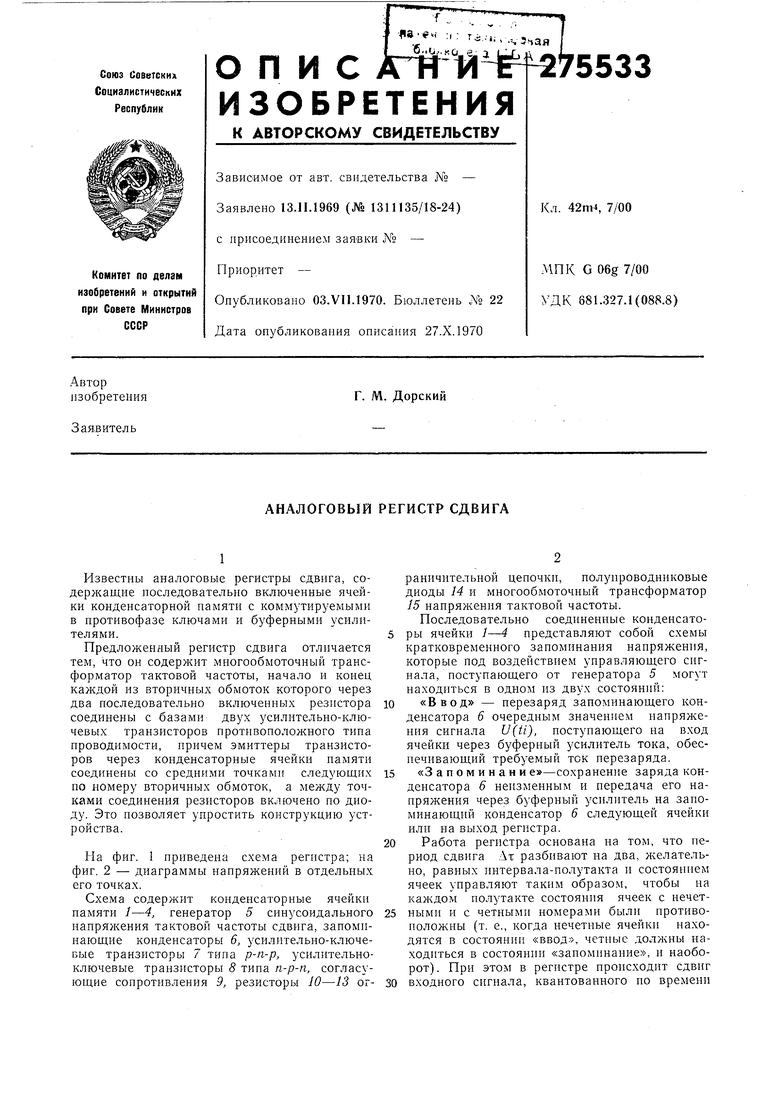

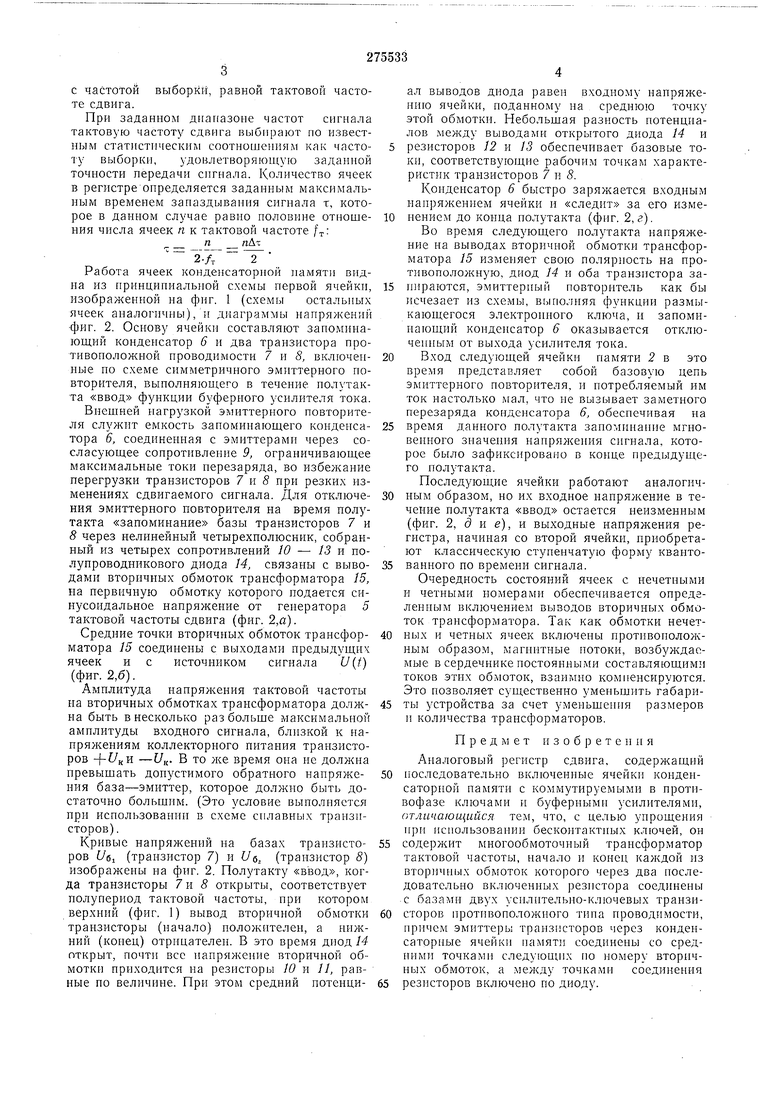

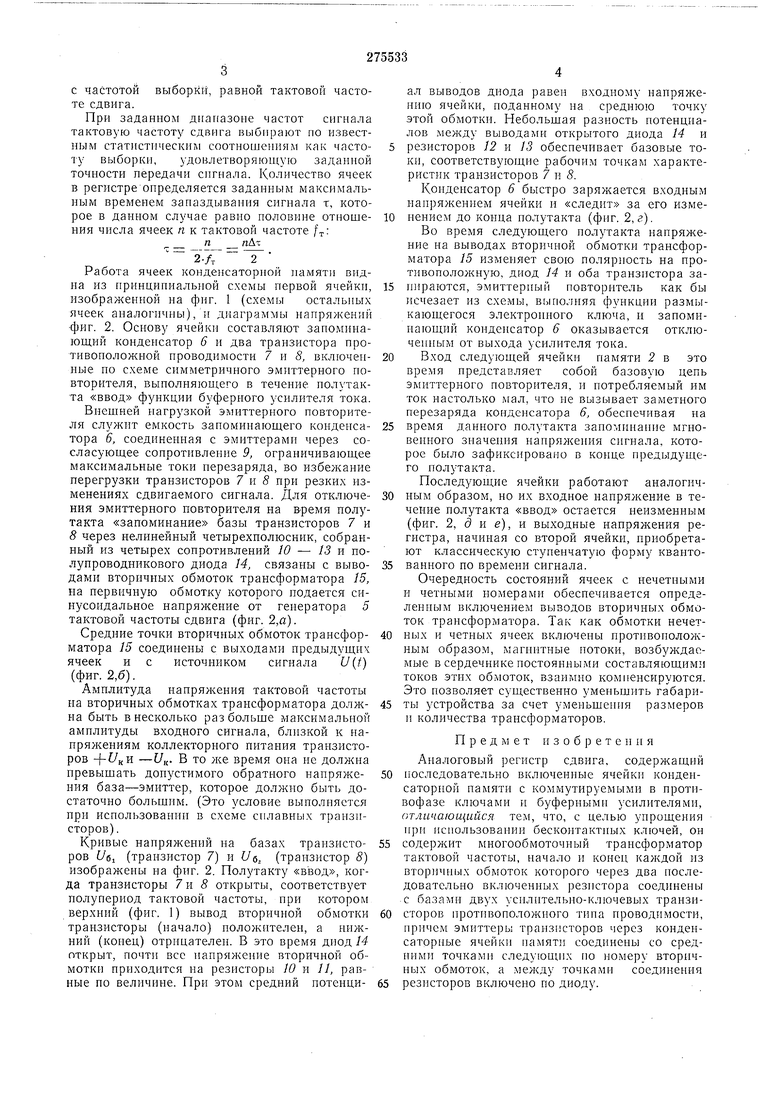

На фиг. 1 приведена схема регистра; на фиг. 2 - диаграммы напряжений в отдельных его точках.

Схема содержит конденсаторные ячейки памяти /-4, генератор 5 синусоидального напряжения тактовой частоты сдвига, запомииающие конденсаторы 6, усилительно-ключевые транзисторы 7 типа р-п-р, усилительноключевые транзисторы 8 типа п-р-п, согласующие сопротивления Э, резисторы 10-13 ограничительной цепочки, полупроводниковые диоды 14 и многообмоточный трансформатор 15 напряжения тактовой частоты. Последовательно соединенные кондепсаторы ячейки /-4 представляют собой схемы кратковременного запоминания напряжения, которые под воздействием управляющего сигнала, поступающего от генератора 5 могут находиться в одном из двух состояний:

«Ввод - перезаряд запоминающего конденсатора 6 очередным значением напряжения сигнала U(ti), ноступающего на в.ход ячейки через буферный усилитель тока, обеспечивающий требуемый ток перезаряда.

«Запоминание -сохранение заряда конденсатора 6 неизменным и передача его напряжения через буферный усилитель на заиоминающпй конденсатор 6 следующей ячейки илп на выход регистра.

Работа регистра основана на том, что период сдвига AT разбивают на два, л елательно, равных интервала-полутакта п состояннем ячеек управляют такпм образо.м, чтобы на каждом полутакте состоянпя ячеек с нечетными п с четнымп номерами были противоположны (т. е., когда нечетные ячейки находятся в состоянии «ввод, четные должны находиться в состоянии «запоминание, и наоборот). При этом в регистре происходит сдвиг

с частотой выборк, равной тактовой частоте сдвига.

При заданном диапазоне частот сигиала тактовую частоту сдвига выбирают ио известным статистическим соотиошеииям как частоту выборки, удовлетворяюи ую заданной точности иередачи сигиала. Количество ячеек в регистре онределяется заданным максимальным временем заиаздываиия сигнала т, которое в данном случае равно иоловине отношения числа ячеек п к тактовой частоте ff-. п пДт

7./7 1

Работа ячеек конденсаториой памяти видна из принциииальиой схемы иервой ячейки, изобрал енной на фиг. 1 (схемы остальных ячеек аналогичиы), и диаграммы напряжений фнг. 2. Основу ячейки составляют запоминающий кондеисатор 6 и два траизистора нротивоиоложной нроводнмости 7 н 8, включениые ио схеме симметричного эмиттерного иовторителя, выиолняющего в течение иолутакта «ввод функции буферного усилнтеля тока.

Внешней нагрузкой эмиттерного повторителя служит емкость заноминающего кондеисатора 6, соединенная с эмиттерами через сосласующее сопротивление 9, ограничивающее максимальные токи нерезаряда, во избежание перегрузки транзисторов 7 н 8 при резких изменениях сдвигаемого сигнала. Для отключения эмиттерного повторителя на в-ремя иолутакта «запоминание базы транзисторов 7 и 8 через нелинейный четырехполюсник, собранный из четырех сопротивлений 10 - 13 и полупроводникового диода 14, связаны с выводами вторичных обмоток трансформатора 15, на первичную обмотку которого подается синусоидальное напряжение от геиератора 5 тактовой частоты сдвига (фиг. 2,а).

Средние точки вторичных обмоток траисформатора 15 соединены с выходами предыдущих: ячеек и с источником сигнала U (t) (фиг. 2,6).

Амплитуда напряжения тактовой частоты на вторичных обмотках трансформатора должна быть в несколько разбольще максимальной амилитуды входного сигнала, близкой к напряжениям коллекторного питання транзисторов -j-f/gH -Uff. В то же время она не должна нревыщать допустимого обратного нанряжеиия база-эмиттер, которое должно быть достаточно большим. (Это условие выполняется при использоваиии в схеме сплавных транзисторов) .

Кривые наиряженнй на базах траизисторов f/6i (траизистор 7) и U (транзистор 8) изображеиы на фиг. 2. Полутакту «ввод, когда транзисторы 7и 5 открыты, соответствует иолунериод тактовой частоты, нрн котором верхний (фиг. 1) вывод вторичиой обмотки транзисторы (начало) положителен, а инжннй (конец) отрицателен. В это время диод 14 открыт, почти вес напряжение вторичной обмоткн приходится на резнсторы 10 и 11, равные по величине. При этом средний нотенциал выводов диода равен входному напряжению ячейки, иоданному на среднюю точку этой обмотки. Небольшая разность потенциалов между выводами открытого диода 14 и резисторов 12 и 13 обесиечивает базовые токи, соответствующие рабочим точкам характеристик транзисторов 7 и 8.

Коиденсатор 6 быстро заряжается входным напряжением ячейки и «следит за его изменением до конца нолутакта (фнг. 2, г).

Во время следующего иолутакта напряженне на выводах вторпчиой обмотки трансформатора 15 изменяет свою полярность на противоположную, диод 14 и оба транзистора запираются, эмиттерпый повторитель как бы исчезает из схемы, выиолияя функции размыкающегося электроииого ключа, и запоминающий коидеисатор 6 оказывается отключенным от выхода усилителя тока.

Вход следующей ячейки памяти 2 в это время представляет собой базовую цепь эмиттерного повторителя, и потребляемый им ток настолько мал, что ие вызывает заметного перезаряда кондеисатора 6, обеспечивая на время данпого полутакта заиомиианне мгновенного значення наиряжеиия сигнала, которое было зафиксировано в конце предыдущего полутакта.

Последующие ячейки работают аналогичным образом, но их входное напряжение в течение иолутакта «ввод остается неизменным (фиг. 2, i9 и е), и выходные нанряжения регистра, начиная со второй ячейки, приобретают классическую ступенчатую форму квантованного по времени сигнала.

Очередность состояний ячеек с нечетными и четными номерами обеспечивается определенным включением выводов вторичных обмоток траисформатора. Так как обмотки нечетных и четных ячеек включены нротнвоположным образом, магннтные потоки, возб ждаемые в сердечнике постоянными составляющими токов этих обмоток, взаимно компенсируются. Это позволяет существенно уменьшить габариты устройства за счет умеиьщеиия размеров и количества трансформаторов.

Предмет изобретения

Аналоговый регистр сдвига, содержащий последовательно включенные ячейки конденсаторной памяти с коммутируемыми в противофазе ключами п буферными усилителями, отличающийся тем, что, с целью упрощения при использовании бесконтактных ключей, он содержит многообмоточный трансформатор тактовой частоты, начало н конец каждой из вторичиых обмоток которого через два носледовательио включенных резнстора соединены с базами двух усилительио-ключевых траизнсторов протнвоположного типа проводимости, причем эмиттеры транзисторов через конденсаториые ячейки памяти соединены со средними точками следующнх но номеру вторичных обмоток, а между точкамн соединения резисторов включено по диоду.

Ь-Г

1

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЬЧНО-ТЕХНН'1ЕГКАЯБИБЛИОТЕКАГ. М. Дорский | 1971 |

|

SU301708A1 |

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| МНОГОУРОВНЕВЫЙ ТРАНЗИСТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 2009 |

|

RU2411629C1 |

| ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU428535A1 |

| Многоканальный коммутатор непрерывных сигналов | 1983 |

|

SU1116539A1 |

| Кольцевой реверсивный счетчик | 1972 |

|

SU441670A1 |

| КАСКАДНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2019 |

|

RU2717338C1 |

| КАСКАДНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2019 |

|

RU2735323C2 |

| Инвертор | 1979 |

|

SU845251A1 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1970 |

|

SU273272A1 |

Даты

1970-01-01—Публикация