Изобретение относится к области вычислительной и измерительной техники.

Известны аналоговые регистры сдвига, содержащие управляемые в противофазе от генератора прямоугольных импульсов тактовой частоты последовательно соединенные ячейки памяти на коммутируемых эмиттерных повторителях на составных транзисторах с запоминающими конденсаторами.

Предложенный аналоговый регистр сдвига отличается от известных тем, что в нем вход ячейки памяти подключен к базам р - п - р и п - р - п транзисторов, эмиттеры которых соединены соответственно с базами второй пары п - р - п и р - п - р транзисторов и через резисторы подключены к парафазным выходам генератора прямоугольных импульсов тактовой частоты, а эмиттеры второй пары транзисторов подсоединены к назаземленной обкладке запоминающего конденсатора и одновременно к базам транзисторов следующей ячейки памяти.

Это позволило упростить аналоговый регистр сдвига и расширить его частотный диапазон.

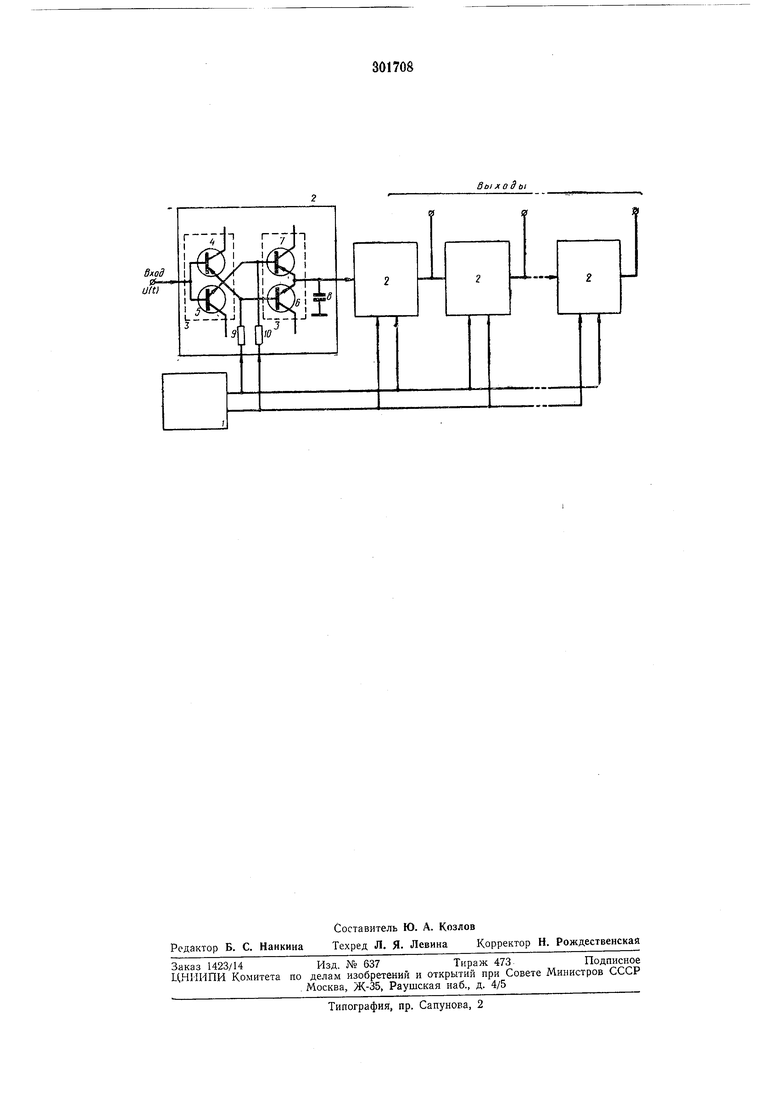

мых эмиттерных повторителях 3 на составных транзисторах 4, 5, 6, 7 с запоминающими конденсаторами 8; причем вход ячейки памяти 2 подключен к базам р - п - р транзистора 4 и п - р - п транзистора 5, эмиттеры которых соединены соответственно с базами второй пары п-р-п транзистора 6 и р-п-р транзистора 7 и через резисторы 9 -ц 10 подключены к парафазным выходам генератора

1 прямоугольных импульсов тактовой частоты. Эмиттеры второй пары транзисторов 6 и 7 подсоединены к незаземленной обкладке запоминающего конденсатора 8 и одновременно к базам транзисторов следующей ячейки

памяти 2.

Устройство состоит из заданного числа п последовательно соединенных ячеек памяти 2, представляющих собой конденсаторные схемы кратковременного запоминания напряжения, которые под воздействием управляющего сигнала, поступающего от генератора прямоугольных импульсов тактовой частоты, могут находиться в одном из двух возможных состояний: «Ввод - перезаряд запоминающего

конденсатора 8 очередным мгновенным значением напряжения сигнала U(ti), поступающего на вход ячейки через эмиттерный повторитель 3, обеспечивающий требуемый ток перезаряда, и «Запоминание - сохранение зарянапряжения через эмиттерный повторитель на запоминающий конденсатор следующей ячейки памяти или на выход аналогового регистра сдвига.

Работа аналогового регистра сдвига основана на том, что период сдвига (такт) разбивается на два равных интервала - полутакта, и управление состоянием ячеек памяти 2 осуществляется таким образом, чтобы на каждом полутакте состояния четных и нечетных ячеек памяти были противоположны, т. е. если нечетные ячейки памяти 2 находятся в состоянии «Ввод, четные должны находиться в состоянии «Запоминание и наоборот. При этом в аналоговом регистре сдвига происходит сдвиг входного сигнала, квантованного по времени с частотой выборки, равной тактовой частоте сдвига.

Во время первого полупериода тактовой частоты (первый полутакт) напряжение на нулевом выходе генератора / прямоугольных импульсов тактовой частоты положительно и равно напряжению коллекторного питания схемы, а напряжение на его другом выходе отрицательно. Все транзисторы в ячейке памяти 2 при этом открыты и образуют симметричный эмиттерный повторитель 3 с коэффициентом передачи по напряжению, близким к единице, связывающий вход ячейки памяти 2 с запоминающим конденсатором 8. Благодаря малому выходному сопротивлению эмиттерного повторителя 3 постоянная времени перезаряда запоминающего конденсатора 8 оказывается меньше периода верхней частоты сдвигаемого сигнала, и напряжение на запоминающем конденсаторе следует за входным напряжением ячейки памяти, которая находится в состоянии «Ввод.

Во время второго полупериода тактовой частоты (второй полутакт) напряжения на выходах генератора / прямоугольных импульсов тактовой частоты меняют знаки, при этом эмиттерный повторитель 3 в ячейке памяти

запирается, разрывая связь запоминающего конденсатора S со входом. В результате напряжение на запоминающем конденсаторе в течение BTojJoro полутакта остается практически неизменным, равным мгновенному значению сигнала на входе ячейки памяти 2, зафиксированному в конце первого полутакта, т. е. ячейка памяти находится в состоянии «Запоминание. Аналогично работают все нечетные ячейки памяти аналогового регистра сдвига.

Четные ячейки памяти 2 связываются с выходами генератора прямоугольных импульсов тактовой частоты противоположным образом,

и поэтому первому полутакту в них соответствует состояние: «Запоминание, а второму - «Ввод, чем обеспечивается требуемая последовательность состояний смежных ячеек памяти 2 аналогового регистра сдвига.

Предмет изобретения

Аналоговый регистр сдвига, содержащий

управляемые в противофазе от генератора прямоугольных импульсов тактовой частоты последовательно соединенные ячейки памяти на коммутируемых эмиттерных повторителях на составных транзисторах с запоминающими

конденсаторами, отличающийся тем, что, с целью упрощения устройства и расщирения частотного диапазона, в нем вход ячейки памяти подключен к базам р - п - р и п - / - п транзисторов, эмиттеры которых соединены соответственно с базами второй пары д - р - п и р - п - р транзисторов и через резисторы подключены к парафазным выходам генератора прямоугольных импульсов тактовой частоты, а эмиттеры второй пары

транзисторов подсоединены к пезаземленной обкладке запоминающего конденсатора и одновременно к базам транзисторов следующей ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU275533A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| ПАРАФАЗНЫЙ ГЕНЕРАТОР ЛИНЕЙНО-ИЗМЕНЯЮЩИХСЯНАПРЯЖЕНИЙ | 1972 |

|

SU423235A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU903988A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU957275A1 |

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU305480A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU868836A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873278A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

Даты

1971-01-01—Публикация