1

Изобретение относится к области автоматики и вычислительной техники.

Известны суммирующие линии задержки, содержащие последовательно соединенные аналоговые регистры сдвига на последовательно включенных ячейках памяти, выходы которых соединены с п входами устройства. Каждая ячейка памяти содержит входной буферный усилитель зарядного тока, соединенный через ключ с конденсаторным накопителем и выходом ячейки памяти. Управляющие входы ключей соединены с соответствующими противофазными выходами генератора тактовой частоты.

Предложенное устройство отличается от известных тем, что в него введены 2п двухпозиционных электронных переключателя, управляющие входы каждой пары которых соединены с соответствующими выходами генератора тактовой частоты. Один вход каждого двухпозиционного электронного переключателя подключен к выходу источника суммируемого сигнала, а другой вход - к шине нулевого потенциала. Выход каждого нечетного двухпозиционного электронного переключателя через дополнительный конденсаторный накопитель соединен с выходом ячейки памяти предыдущего разряда регистра. Выход каждого четного двухпозиционного электронного переключателя подключен через аналогичный конденсаторный накопитель к выходу ячейки памяти последующего разряда регистра.

Это позволило повысить точность и надежность работы устройства.

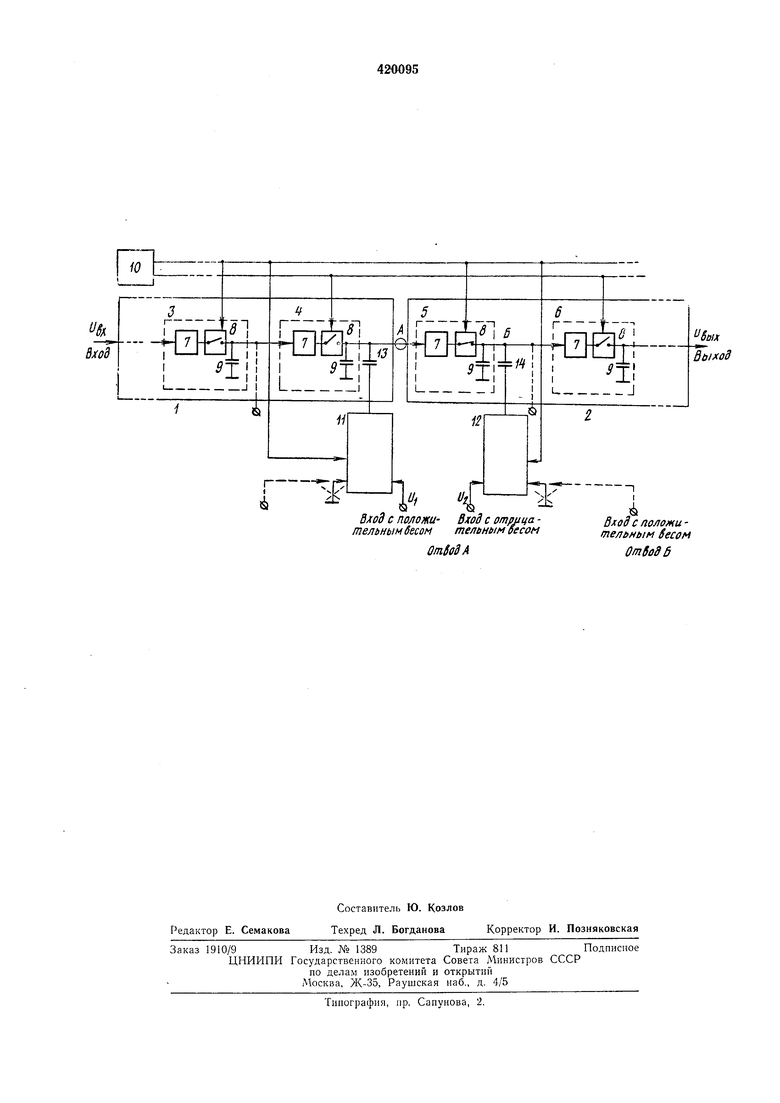

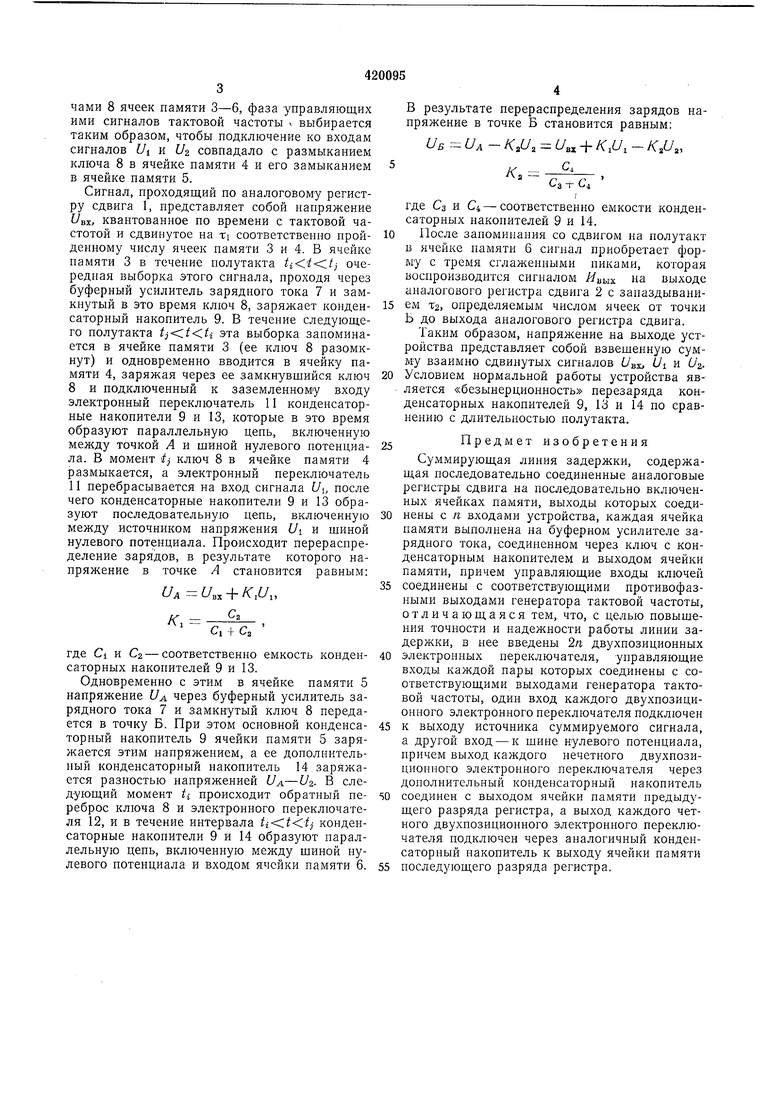

Блок-схема устройства приведена на чертеже.

Устройство содержит аналоговые регистры сдвига 1 и 2, ячейки памяти 3-6, каждая из которых содержит входной буферный усилптель зарядного тока 7, ключ 8 и конденсаторный накопитель 9, а кроме того, генератор тактовой частоты 10, 2п двухпозиционных электронных переключателя 11 и 12 и дополнительные конденсаторные накопители 13 и 14.

Устройство работает следующим образом.

Цикл управления ячейками памяти 3-6 состоит из двух интервалов (полуциклов): «ввод - заряд конденсаторного накопителя 9 мгновенным значением напряжения входного сигнала, и «запоминание - фиксация напряжения, оказавшегося на конденсаторном наконителе 9 в момент окончания предыдущего полуцикла.

Ячейки памяти 3-6 с четными и нечетными

номерами управляются в противофазе, обеспечивая последовательную передачу периодических выборок амплитуды сигнала вдоль аналогового регистра сдвига 1 и 2. Двухнозиционные электронные переключатели 11 и 12 переключаются синхронно с ключами 8 ячеек памяти 3-6, фаза управляющих ими сигналов тактовой частоты выбирается таким образом, чтобы подключение ко входам сигналов Ui и Uz совпадало с размыканием ключа 8 в ячейке памяти 4 и его замыканием в ячейке памяти 5.

Сигнал, проходящий по аналоговому регистру сдвига 1, представляет собой напряжение УВХ, квантованное по времени с тактовой частотой и сдвинутое на TI соответственно пройденному числу ячеек памяти 3 и 4. В ячейке памяти 3 в течение полутакта ti,t,tj очередная выборка этого сигнала, проходя через буферный усилитель зарядного тока 7 и замкнутый в это время ключ 8, заряжает конденсаторный накопитель 9. В течение следующего полутакта tj. эта выборка запоминается в ячейке памяти 3 (ее ключ 8 разомкнут) и одновременно вводится в ячейку памяти 4, заряжая через ее замкнувшийся ключ 8 и подключенный к заземленному входу электронный переключатель 11 конденсаторные накопители 9 и 13, которые в это время образуют параллельную цепь, включенную между точкой А и шиной нулевого потенциала. В момент tj ключ 8 в ячейке памяти 4 размыкается, а электронный переключатель 11 перебрасывается на вход сигнала LJ, после чего конденсаторные накопители 9 и 13 образуют последовательную цепь, включенную между источником напряжения Ui и шиной нулевого потенциала. Происходит перераспределение зарядов, в результате которого напряжение в точке Л становится равным:

UA вх + г,,

IV- t/2

AI - ., , f. С -г W2

где Ci и GZ - соответственно емкость конденсаторных накопителей 9 и 13.

Одновременно с этим в ячейке памяти 5 напряжение UA через буферный усилитель зарядного тока 7 и замкнутый ключ 8 передается в точку Б. При этом основной конденсаторный накопитель 9 ячейки памяти 5 заряжается этим напряжением, а ее дополнительный конденсаторный накопитель 14 заряжается разностью напряженней В следующий момент ti происходит обратный переброс ключа 8 и электронного переключателя 12, и в течение интервала конденсаторные накопители 9 и 14 образуют параллельную цепь, включенную между шиной нулевого потенциала и входом ячейки памяти 6.

В результате перераспределения зарядов напряжение в точке Б становится равным:

UB UA - K,U, зх + /С:, - К,и,,

. С,

/С.С.

где Сз и d - соответственно емкости конденсаторных накопителей 9 и 14.

После запоминания со сдвигом на полутакт в ячейке памяти 6 сигнал приобретает форму с тремя сглаженными пиками, которая воспроизводится сигналом //вых на выходе аналогового регистра сдвига 2 с заназдыванием Т2, определяемым числом ячеек от точки Б до выхода аналогового регистра сдвига.

Таким образом, напряжение на выходе устройства представляет собой взвешенную сумму взаимно сдвинутых сигналов Us: Ui и Uz.

Условием нормальной работы устройства является «безынерционность перезаряда конденсаторных накопителей 9, 13 и 14 по сравнению с длительностью полутакта.

Предмет изобретения

Суммирующая линия задержки, содержащая последовательно соединенные аналоговые регистры сдвига на последовательно включенных ячейках памяти, выходы которых соединены с п входами устройства, каждая ячейка памяти выполнена на буферном усилителе зарядного тока, соединенном через ключ с конденсаторным накопителем и выходом ячейки памяти, причем управляющие входы ключей

соединены с соответствующими противофазными выходами генератора тактовой частоты, отличающаяся тем, что, с целью повышения точности и надежности работы линии задержки, в нее введены 2п двухпозиционных

электронных переключателя, управляющие входы каждой пары которых соединены с соответствующими выходами генератора тактовой частоты, один вход каждого двухпозиционного электронного переключателя подключен

к выходу источника суммируемого сигнала, а другой вход - к шине нулевого потенциала, причем выход каждого нечетного двухпозиционного электронного переключателя через дополнительный конденсаторный накопитель

соединен с выходом ячейки памяти предыдущего разряда регистра, а выход каждого четного двухнозиционного электронного переключателя подключен через аналогичный конденсаторный накопитель к выходу ячейки памяти

последующего разряда регистра.

%

Bj(od

uSoix

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU275533A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873278A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU864342A1 |

| ТЕЬЧНО-ТЕХНН'1ЕГКАЯБИБЛИОТЕКАГ. М. Дорский | 1971 |

|

SU301708A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873279A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1451742A1 |

| Кусочно-полиномиальный аппроксиматор | 1986 |

|

SU1322327A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

тельным бесом телчным бесом OmSoSA

Даты

1974-03-15—Публикация

1972-06-12—Подача