Известны логарифмические иреобразователи напряжения в двоичный код с промежуточным преобразованием напряжения во временной интервал.

Недостаток известных преобразователей заключается в том, что максимальное время преобразования определяется числом разрядов кода результата преобразования и частотой .импульсов счета и не может быть уменьшено ниже определенного уровня, устанавливаемого из технических соображений. Повышение частоты импульсов счета для ускорения преобразования влечет за. собой уменьшение постоянной времени разряда конденсатора схемы формирования экспоненциально спадающего напряжения, что, в свою очередь, приводит к резкому росту динамических погрешностей преобразования.

Предложенный преобразователь отличается тем, что для ускореиия иреобразования в N 2 раз к выходу схемы формирования экспоненциально спадающего нaиpялieния подключено Л схем сравнения иаиряжеиий, выходы которых через одну схему сборки соединены со входом триггера управления. Выходы схем сравнения, кроме первой, через другую схему сборки соединены со входом ключа разряда конденсатора схемы формирования эксионенциально спадающего напряжения, а через остальные схемы сборки - со входами триггеров регистра старших разрядов кода.

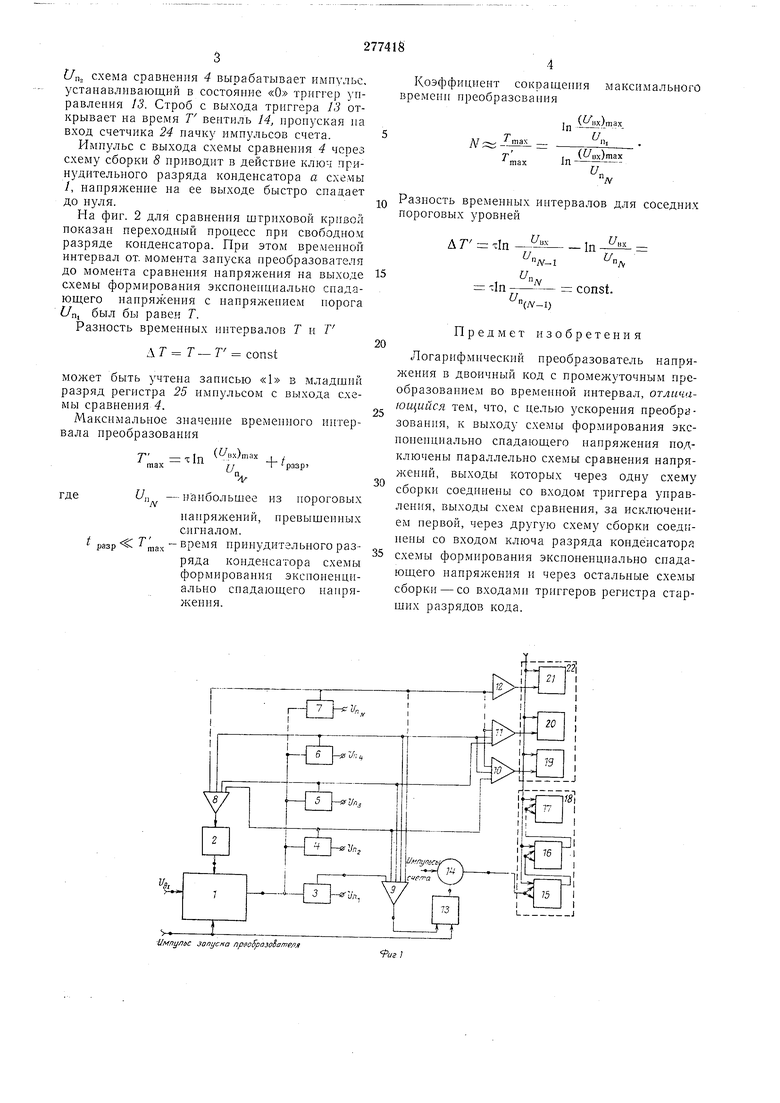

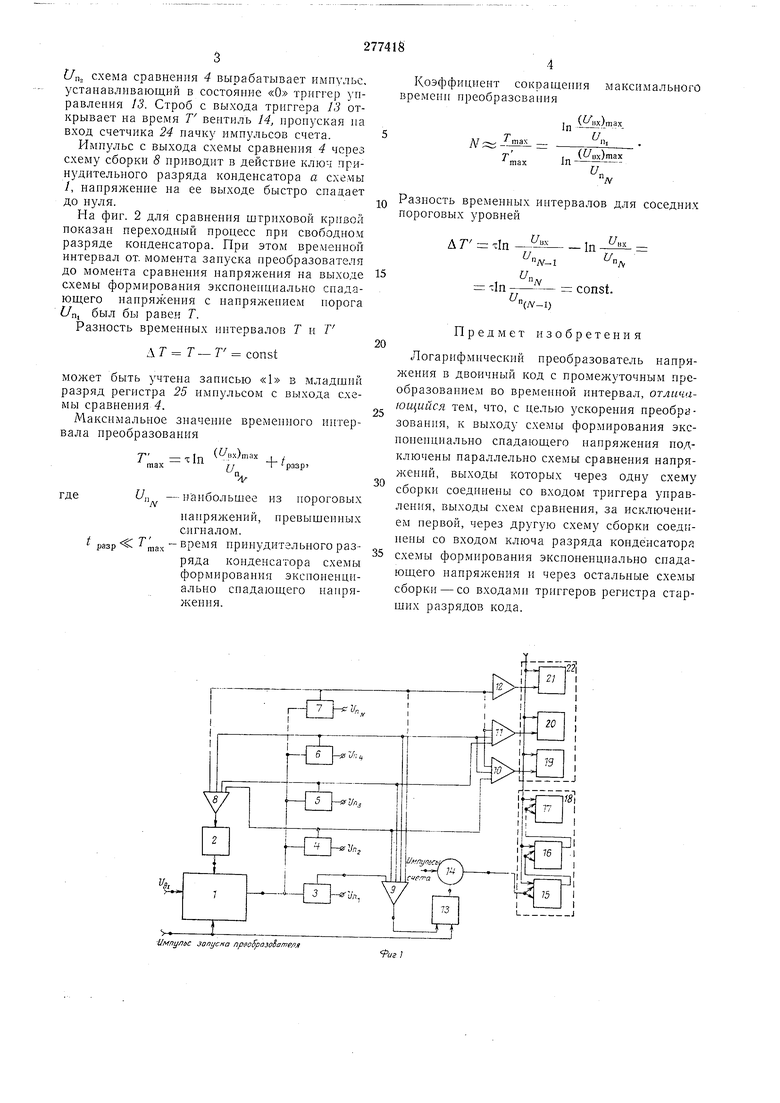

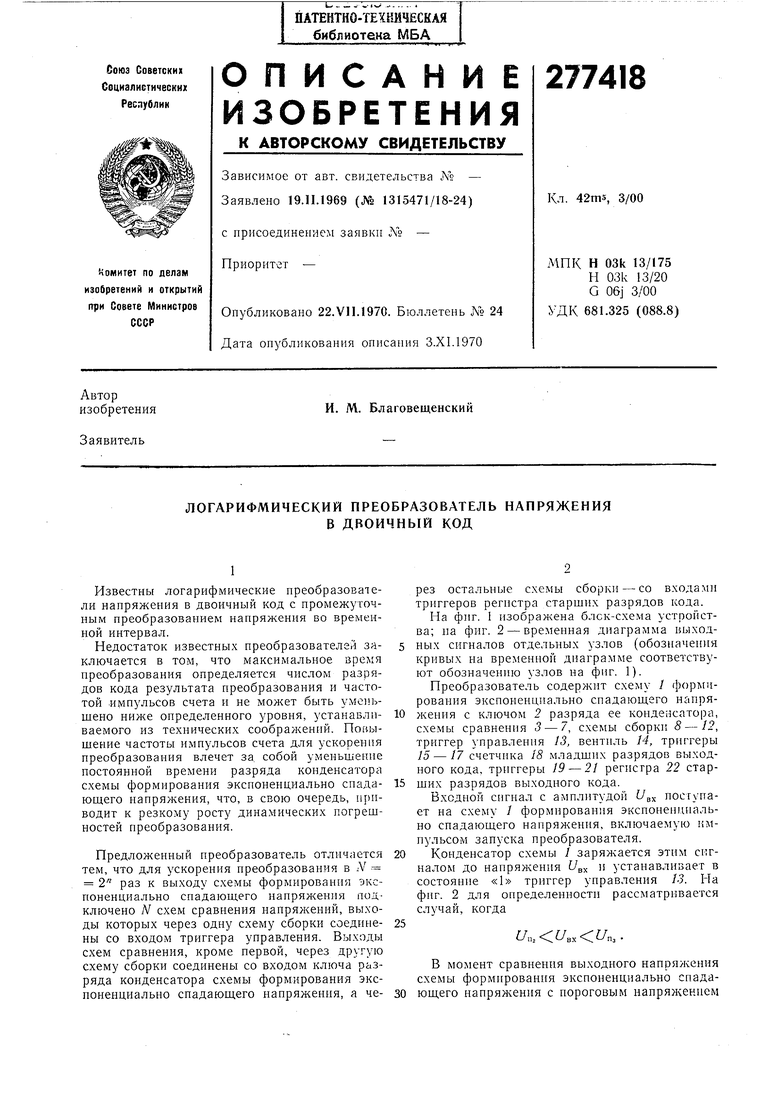

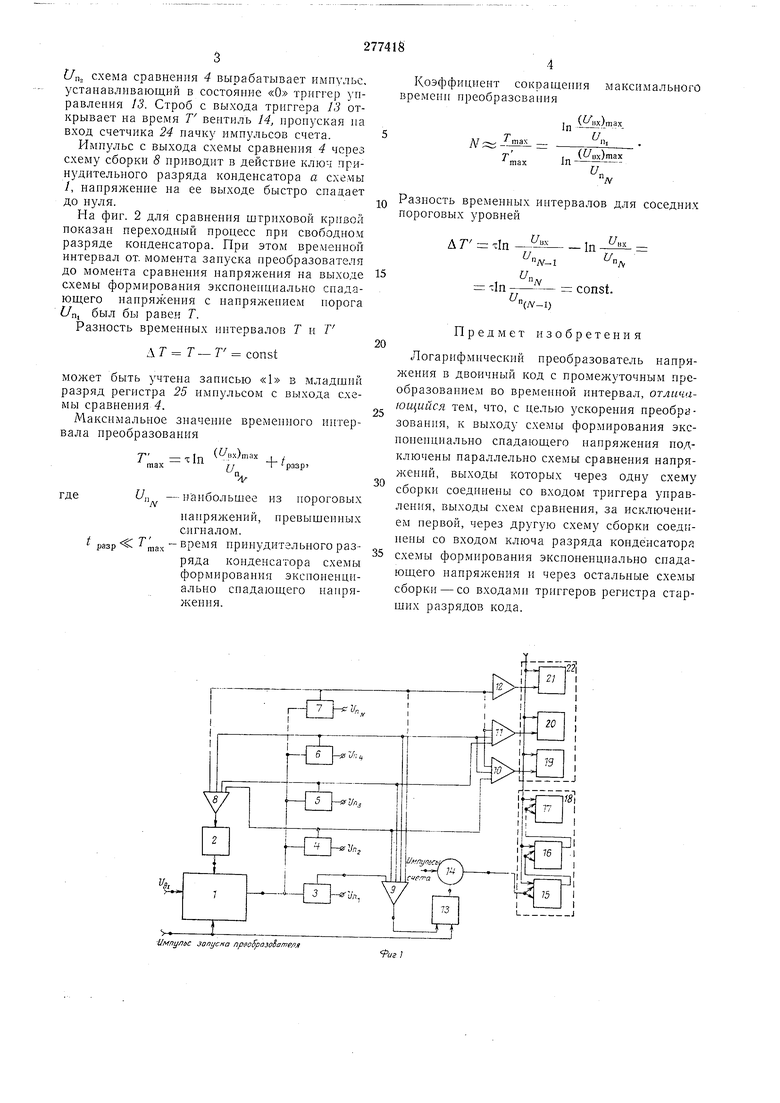

На фиг. 1 изображена блок-схема устройства; па фиг. 2 - временная диаграмма выходных сигналов отдельных узлов (обозначения кривых на временной диаграмме соответствуют обозначению узлов на фиг. 1).

Преобразователь содержит схему / (5 Р чрования экспоненциально спадающего напряження с ключом 2 разряда ее конденсатора, схемы сравнения 3 - 7, схемы сборки 8 - 12, триггер управления 13, вентиль 14, триггеры 15 - 17 счетчика 18 младших разрядов выходного кода, трнггеры 19 - 21 регисгра 22 старших разрядов выходного кода.

Входной сигнал с амплитудой поступает на схему / формирования экспоненциально спадающего напрялсения, включаемую импульсом запуска преобразователя.

Конденсатор схемы / заряжается этнм сигналом до напряжения t/g и устанавливает в состояние «1 триггер управления 13. На фиг. 2 для определенности рассматривается случай, когда

п., .

f/n, схема сравнения 4 вырабатывает импульс, устанавливающий в состояние «О триггер управления 13. Строб с выхода триггера 13 открывает на время Т вентиль 14, иропуская иа вход счетчика 24 пачку импульсов счета.

Имиульс с выхода схемы сравнения 4 через схему сборки 8 ириводит в действие ключ принудительного разряда конденсатора а схемы /, наирял :енне на ее выходе быстро спадает до нуля.

На фиг. 2 для сравнения штриховой кривой показан переходный процесс при свободном разряде конденсатора. При этом временной интервал от. момента запуска преобразователя до момента сравнения напряжения на выходе схемы формирования экспоненциально спадающего нанряження с напряжепием норога Цщ был бы равен Т.

Разность временных интервалов Т и Т

д Г Г - Г const

может быть учтена записью «1 в младщий разряд регистра 25 имнульсом с выхода схемы сравнения 4.

Максимальное значение временного интервала преобразования

( ox/max

.a.

+ /ра

i/n

разр

V

,1 -наибольшее

ИЗ пороговых

где

yv иревышеииых

иаиряжении сигналом.

-С время иринудительного разразрряда конденсатора схемы формирования экспоиенциально снадающего напряжения.

Коэффициеит сокращеиия

максимального времеии преобразования

(х)п

In

f/,,.

г (Bx)max

и„

N

Разность временных иптервалов для соседиих пороговых уровней

t/ux

и,,

А Г Tin -

In

i/,

f/,

л

Л-1

и,

In const.

(/V-I)

Предмет изобретения

Логарифмический преобразователь напряжеиия в двоичный код с промежуточным преобразованием во времеииой интервал, отличающийся тем, что, с целью ускорения преобразования, к выходу схемы формнрования экспоие1щиально спадающего напрял еиия подключены параллельно схемы сравнения напряжений, выходы которых через одну схему сборки соединены со входом триггера уиравления, выходы схем сравнения, за исключением первой, через другую схему сборки соедииеиы со входом ключа разряда конденсатора схемы формировання экспоненциально спадающего напряжения и через остальные схемы сборки - со входами триггеров регистра старших разрядов кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логорифмический преобразователь напряжения в код | 1975 |

|

SU540369A2 |

| Преобразователь код-временной интервал | 1983 |

|

SU1106011A1 |

| Логарифмический время-импульсный преобразователь амплитуды импульса в двоичный код | 1971 |

|

SU661785A1 |

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Логарифмический аналого-цифровой преобразователь | 1989 |

|

SU1656563A2 |

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU799130A1 |

UMntjfltjCbi

1

t

Даты

1970-01-01—Публикация