1

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных устройствах. ..

Известны логарифмические преобразователи, работа которых основана на свободном разряде конденсатора, заряженного до напряжения, близкого к амплитуде входного сигнала, и измерении временного интервала от момента начала разряда конденсатора до момента сравнения напряжения на конденсаторе с напряжением порога 1.

Недостатком таких преобразователей является значительный уровень систематических погрешностей.

Наиболее близким по технической сущности к предложенному является логарифмический преобразователь напряжения в двоичный код, содержащий формирователь экспоненциально спадающего напряжения, состоящий из, ключа, резистора, источника напряжения компенсации и конденсатора, причем вход формирователя экспоненциально спадающего напряжения подключен к шине входного сигнала, а выход - к одному из входов элемента сравнения напряжений, второй вход которого соединен с источником напряжения порога, а выход элемента подключен ко входу триггера, выход которого соединен с потенциальным входом элемента И, к импульсному входу которого подключен выход генератора импульсов, а выход которого соединен с входом счетчика, блок управления работой преобразователя соединен с единичным входом триггера и управляющим входом формирователя экспоненциально спадающего напряжения 2.

Недостатком такбго преобразователя является значительный уровень систематических погрешностей и повышенные требования, предъявляемые к основным аналоговым узлам по стабильности и точности.

Целью изобретения является повыщение точности преобразования.

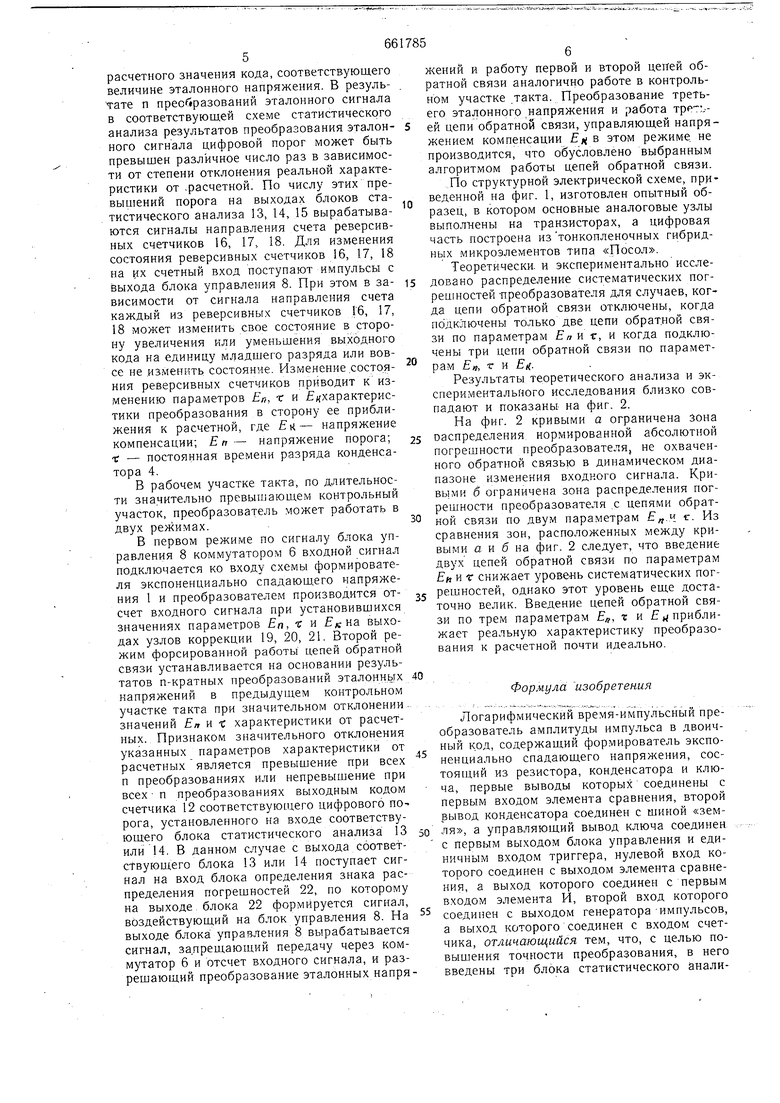

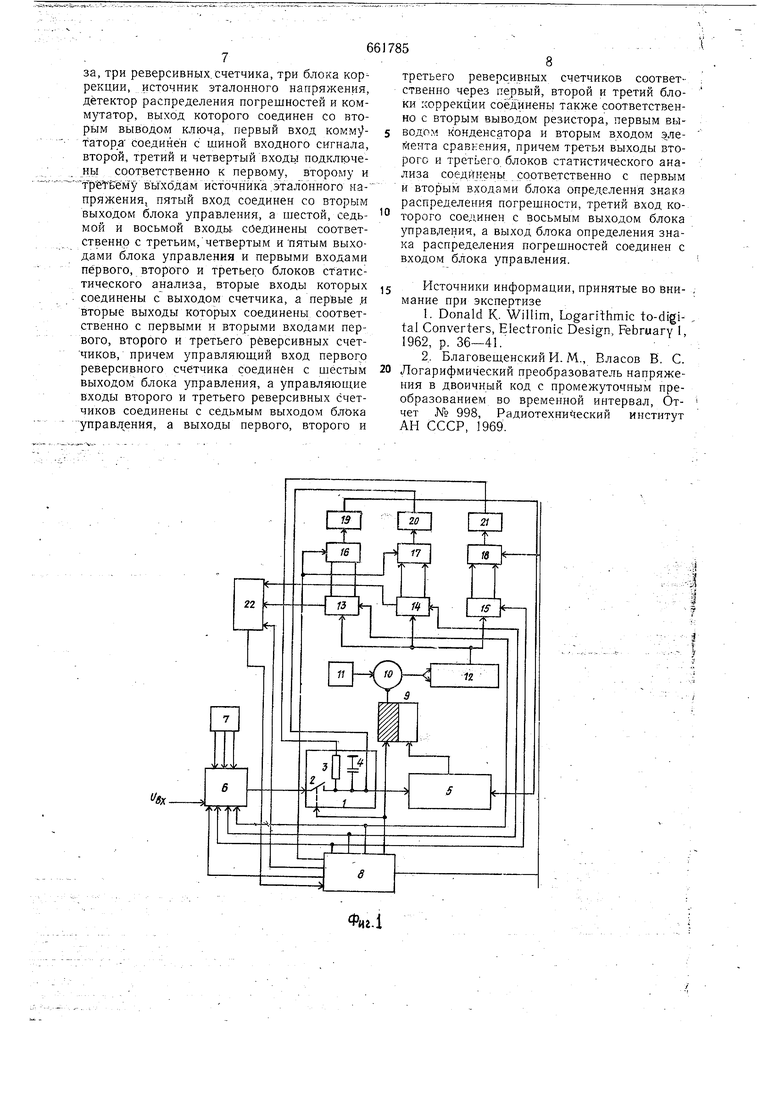

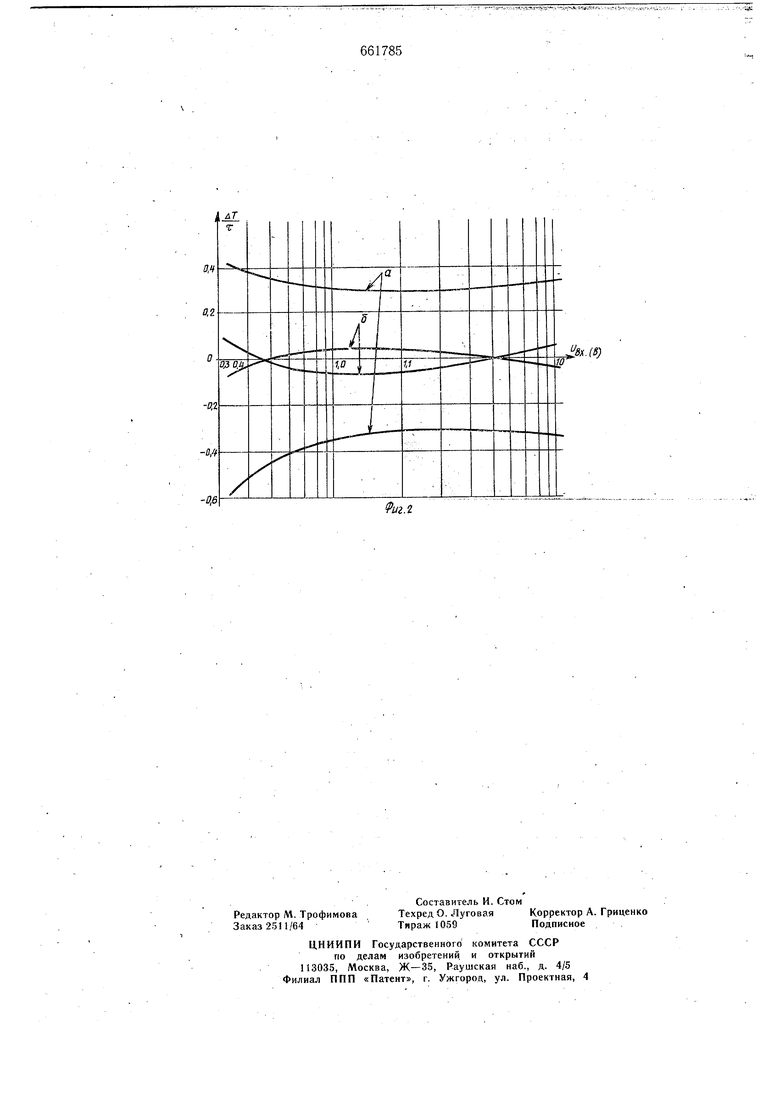

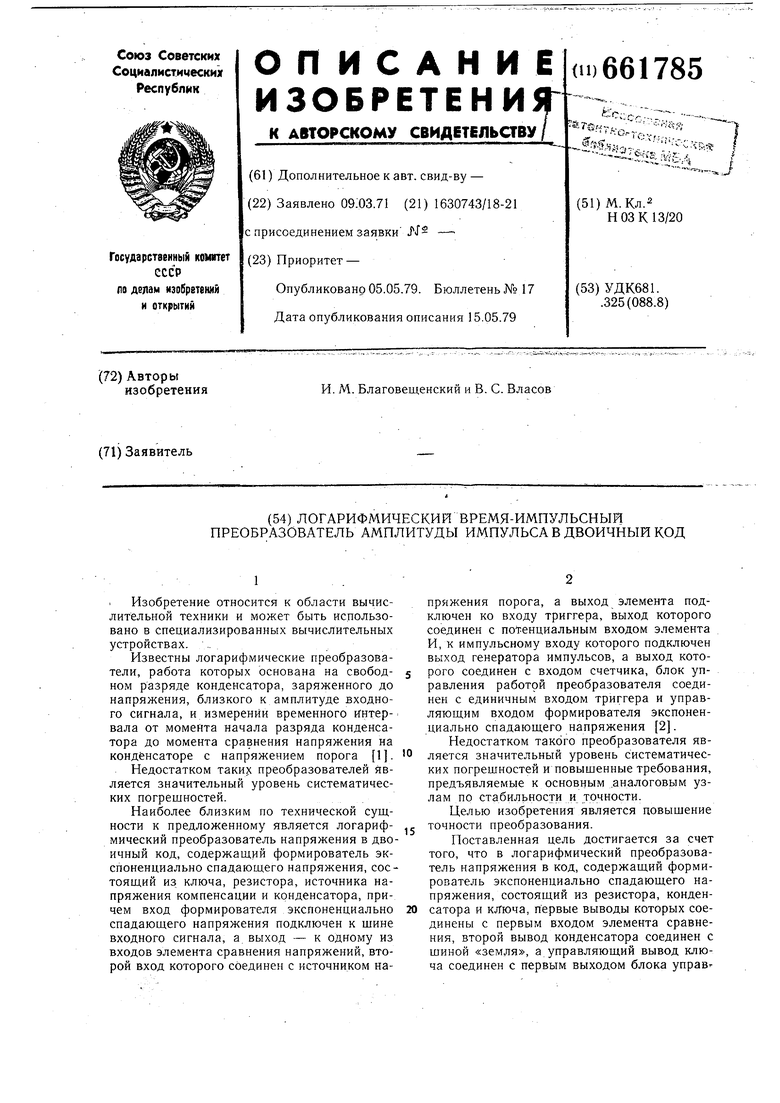

Поставленная цель достигается за счет того, что в логарифмический преобразователь напряжения в код, содержащий формирователь экспоненциально спадающего напряжения, состоящий из резистора, конденсатора и кЯюча, первые выводы которых соединены с первым входом элемента сравнения, второй вывод конденсатора соединен с шиной «земля, а управляющий вывод ключа соединен с первым выходом блока управг лёнйя и единичным входом триггера, нулевой вход которого соединен с выходом элемента сравнения, а выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генера тора импульсов, а выход которого соединен с в;хоДом счётчика/дополнйтёЛьно ввеДены три блока стйт-истйчёского анализа; три реверсивных счетчика, три блока коррекции, источник эталонного напряжения, детектор распределения погрешностей и коммутатор, выход которого соединенсо Bf0ръТй ыводом ключа, первый вход -коммутатора соединен с шиной входного сигнала, второй, третий и четвертый входы подключены соответственно к первому, второму и третьему выходам источника эталонного напряжения, пятый вход соединен со вторым выходом блока управления, а шестой, седьмой и восьмой вхо дьг с№динёньг соответственно; с трётЖм, четвертым и пятым выходами блока управления . и первыми входами первого, второго и третьего блоков статистического анаЛкза, вторые вхоДь которых Соёдинены с выходом счетчика, а первые и вторые выходы которых соединены соответственно с первыми и вторыми входами первого, второго и третьего реверсивных счетчиков, причем управляющий вход первого реверсивного счетчика соединен с ; шестым выходом блока управления, управ ляющйе входы второго и третьего рёверсив Hbix счетчиков ёбёдинёнь с ёёдьмьТм выхоДом блока управления, а выходы цервого, второго и третьего реверсивных счетчиков соответственно через первый, второй и третий блоки коррекции соединены так:4 е соот ветстйенно с вторым выводом резистора, первым выводом конденсатора и вторым входом элемента сравнения, причем третьи выходы второго и третьего блоков статистического агалйза соединены соответственно с первым и вторым входами блока определения знака распределения погрешностей, третий вход которого Соединен с восьмым выходом блока управления, а выход блока определения знака распределения погрешностей соединен с входом блока управления. На фиг. 1 представлена структурная элек Грическая схема предлагаемого логарифмического время-импульсного преобразователя амплитуды импульса в двоичный код; на фиг. 2 - кривые распределе ния нормированной абсолютной погрешности преобразователя. Преобразователь содержит формирователь экспоненциально спадающего напряжения 1, состоящий из ключа 2, резистора 3, конденсатора 4, пёрвьТё выШдЫГ кбТбрых соедийенЫ с первым входом элемента сравнения 5, второй вывод конденсатора 4 соединен с шиной «земля, второй вывод ключа 2 соединен с выходом коммутатора 6, первый которого соединен с шиной входного сигнала, а второй, третий и четвертый входы КбтбрбТо соединены с первым, вторым и третьим выходами источника эталонного напряжения 7, а управляющий вход ключа 2 соединен с первым выходом блока управления 8, второй выход которого соединен с пятым входом коммутатора и с единичным входом триггера 9, нулевой вход которого соединен с выходом элемента сравнения 5, а выход соединен с первым входом элемента 10 И, второй вход которого соединен с выходом генератора импульсов 11, элемента И 10 соединен со входом счетчика 2, выход которого подключен к одним входам блоков статистического анализа 13, 14 и 15, другие входы которых соединены соответственно с шестым, седьмым и восьмым входами коммутатора бис третьим, четвертым И пятым выходами блока управления 8, первые и вторые выходы блоков статистического анализа 13, 14 и 15 соединены соответственно с первыми и вторыми входами реверсивных счетчиков 16, 17 и 18, выходы которых через блоки коррекции 19, 20 и 21 соединены соответственно с вторым входом элемента сравнения 5, первым выводом кон-. денсатора 4 и вторым выводом резистора 2, управляюш,ий вход реверсивного счетчика 18 соединен с шестым выходом блока управления 8, а правляющие входы реверсивных счетчиков 16 и 17 соединены с седьмым выходом блШа управления, третьи выходы бл.оков статистического анализа 13 и 14 соединены с первым и вторым входами блока определения знака распределения погрешностей 22, третий вход которого соединен с восьмым выходом блока управления 8, вход Которого соединен с выходом блока определения знака распределения погрешностей 22., Логарифмический преобразователь работает следующим образом. Такт преобразования разбит по времени на два участка - контрольный и рабочий. В контрольном участке такта, расположенном в начале или конце такта преобразования по командам блока управления 8 коммутаторо.м 6 ко входу формирователя экспонёнциально спадающего напряжения 1 подключается каждый из трех эталонных сигналов. Синфазно с подключением эталонного сигнала открывается соответствующий блок статистического анализа, предназначенный дЛя исключения влияния на работу цепей обратной связи возможной погрешности однократного преобразования эталонного сигнала, связанной с несинхронностью измеряемого интервала времени Т и импульсов генератора, импульсов П. Блоком управления 8 формируются импульсы запуска преобразователя по каждому из эталонных сигналов. Производится п-кратное поочередное преобразование каждого из эталонных сигналов в одном контрольном участке такта. На входа1 : каждого из блоков статистического анализа 13, 14, 15 установлен цифровой порог; равный значению кода, отличающегося на 1/2 от расчетного значения кода, соответствующего величине эталонного напряжения. В результате п npeof pa30BaHHfl эталонного сигнала в соответствующей схеме статистического анализа результатов преобразования эталонного сигнала цифровой порог может быть превышен различное число раз в зависимости от степени отклонения реальной характеристики от -расчетной. По числу этих превыщений порога на выходах блоков статистического анализа 13, 14, 15 вырабатываются сигналы направления счета реверсивных счетчиков 16, 17, 18. Для изменения состояния реверсивных счетчиков 16, 17, 18 на их счетный вход поступают импульсы с выхода блока управления 8. При этом в зависимости от сигнала направления счета каждый из реверсивных счетчиков 16, 17, 18 может изменить свое состояние в сторону увеличения или уменьшения выходного кода на единицу младшего разряда или вовсе не изменить состояние. Изменение .состояния реверсивных счетчиков приводит к изменению параметров Еп, г и «характеристики преобразования в сторону ее приближения к расчетной, где Ек- напряжение компенсации; Еп- напряжение порога; t - постоянная времени разряда конденсатора 4. В рабочем участке такта, по длительности значительно превышающем контрольный участок, преобразователь может работать в двух режимах. В первом режиме по сигналу блока управления 8 коммутатором 6 входной сигнал подключается ко входу схемы формирователя экспоненциально спадающего напряжения 1 и преобразователем производится отсчет входного сигнала при установившихся значениях параметров Еп, С li « на выходах узлов коррекции 19, 20, 21. Второй режим форсированной работы цепей обратной связи устанавливается на основании результатов п-кратных преобразований эталонньгх напряжений в предыдущем контрольном участке такта при значительном отклонении значений л и t характеристики от расчетных. Признаком значительного отклонения указанных параметров характеристики от расчетных является превышение при всех п преобразованиях или непревышение при всех п преобразованиях выходным кодом счетчика 12 соответствующего цифрового порога, установленного на входе соответствующ;его блока статистического анализа 13 или 14. В данном случае с выхода соответctвyющeгo блока 13 или 14 поступает сигнал на вход блока определения знака распределения погрещностей 22, по которому на выходе, блока 22 формируется сигнал, воздействующий на блок управления 8. На выходе блока управления 8 вырабатывается сигнал, запрещающий передачу через коммутатор 6 и отсчет входного сигнала, и разрешающий преобразование эталонных напря жений и работу первой и второй цепей обратной связи аналогично работе в контрольном участке .такта. Преобразование третьего эталонного напряжения и работа .ей цепи обратной связи, управляющей напряжением компенсации Еf( в этом режиме, не производится, что обусловлено выбранным алгоритмом работы цепей обратной связи. По структурной электрической схеме, приведенной на фиг. 1, изготовлен опытный образец, в котором основные аналоговые узлы выполнены на транзисторах, а цифровая часть построена из тонкопленочных гибридных микроэлементов типа «Посол. Теоретически- и экспериментально исследовано распределение систематических погрешностей -преобразователя для случаев, когда цепи обратной связи отключены, когда подключены только две цепи обратной связи по параметрам Еп и г, и когда подключены три цепи обратной связи по параметрам ЕП, г и Eg. Результаты теоретического анализа и экспериментального исследования близко совпадают и показаны на фиг. 2. На фиг. 2 кривыми а ограничена Зона оаспределения нормированной абсолютной погрешности преобразователя, не охваченного обратной связью в динамическом диапазоне изменения входного сигнала. Кривь1ми б ограничена зона распределения погрешности преобразователя .с цепями обратной связи по двум параметрам ..4 f- Из сравнения зон, расположенных между кривыми а и б на фиг. 2 следует, что введение двух цепей обратной связи по параметрам ЕЙ и т снижает уровень систематических погрешностей, однако этот уровень еще достаточно велик. Введение цепей обратной связи по трем параметрам Е, т и приближает реальную характеристику преобразования к расчетной почти идеально. Формула изобретения Логарифмический время-импульсный преобразователь амплитуды импульса в двоичный к.од, содержащий формирователь экспоненциально спадающего напряжения, состоящий из резистора, конденсатора и ключа, первые выводы которых соединены с первым входом элемента сравнения, второй вывод конденсатора соединен с шиной «земля, а управляющий вывод ключа соединен с первым выходом блока управления и единичным входом триггера, нулевой вход которого соединен с выходом элемента сравнения, а выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора -импульсов, а выход которого соединен с входом счетчика, отличающийся тем, что, с целью повышения точности преобразования, в него введены три блока статистического знализа, три реверсивных, счетчика, три блока коррекции, источник эталонного напряжения, детектор распределения погрешностей и коммутатор, выход которого соединен со вторым выводом ключа, первый вход коммутатора соединен с шиной входного сигнала, второй, третий и четвертый входы подключены соответственно к первому, второму и ТрёТЕему выходам ист очнйка .эталонного напряжения, пятый вход соединен со вторым выходом блока управления, а шестой, седьмой и восьмой входы, соединены соответственно с третьим,четвертым ипятым выходами блока управления и первыми входами первого, второго и третьего блоков статистического анализа, вторые входы которых соединены с выходом счетчика, а первые .и вторые выходы которых соединены соответств.енно с первыми и вторыми входами первого, второго и третьего реверсивных счетчиков, причем управляющий вход первого реверси.вного счетчика соединен с шестым выходом блока управления, а управляюшие входы второго и третьего реверсивных счетчиков соединены с седьмым выходом блока управл ения, а выходы первого, второго и

третьего реверсивных счетчиков соответственно через первый, второй и третий блоки коррекции соединены также соответственно с вторым выводом резистора, первым выводом конденсатора и вторым входом элемента сравнения, причем третьи выходы второго и третьего блоков статистического анализа соединены соответственно с первым и вторым входами блока определения знака распределения погрешности, третий вход которого соединен с восьмым выходом блока управления, а выход блока определения знака распределения погрешностей соединен с входом блока управления.

Источники информации, принятые во вни- , мание при экспертизе

1.Donald К. Willim, Logarithmic to-digi- „ tal Converters, Electronic Design, February 1, 1962, p. 36-41/

2.Благовешенский И. М., Власов В. С. Логарифмический преобразователь напряжения в двоичный код с промежуточным преобразованием во временной интервал. Отчет № 998, Радиотехнический институт АН СССР, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь отношения сигналов | 1978 |

|

SU723602A1 |

| Логарифмический преобразователь | 1978 |

|

SU765819A1 |

| Логорифмический преобразователь напряжения в код | 1975 |

|

SU540369A2 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Логарифмический аналого-цифровой преобразователь | 1989 |

|

SU1656563A2 |

| Анализатор законов распределения | 1979 |

|

SU960845A1 |

| Цифровой датчик линейных перемещений | 1990 |

|

SU1739185A1 |

| Устройство аналого-цифрового преобразования | 1976 |

|

SU620018A1 |

иг.2

Авторы

Даты

1979-05-05—Публикация

1971-03-09—Подача