1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании устройств отображения для получения динамических изображений, например для отображения навигационной обстановки в реальном масштабе времени.

Известны устройства для отображения информации, содержащие электроннолучевую трубку (ЭЛТ), соединенную с блоками развертки по координатам X и У, которые связаны с двоичными умножителями, генератор импульсов, связанный с двоичным делителем частоты. В состав блока развертки входит реверсивный счетчик импульсов, соединенный с входом преобразователя код-аналог, а выход преобразователя подключен к отклоняющей системе ЭЛТ.

Известное устройство не обеспечивает автономного формирования динамического изображения в подвижной системе осей.

Цель изобретения - расширение области применения устройства.

Для этого предлагаемое устройство содержит последовательно соединенные накопительный сумматор, коммутатор и преобразователь, подключенный к первой схеме ИЛИ, регистры сдвига по координатам X и Y, входы которых через третьи схемы И соединены с выходами умножителей, а выходы - с третьей схемой ИЛИ и четвертой и пятой схемами И

соответствующей координаты, причем четвертые схемы И координаты X подключены ко второй схеме ИЛИ координаты Y, а четвертые схемы И координаты У подключены ко

второй схеме ИЛИ координаты X, последовательно соединенные счетчик импульсов, подключенный к четвертой схеме И, и распределитель, связанный с умножителями, схему ввода кодов, связанную с третьей схемой ИЛИ

и шестой схемой И, схему управления интерполяцией, входы которой подключены к делителю импульсов, а выход - к первым схемам И, схему ИЕ - И и дешифраторы, входы которых связаны с блоками развертки координат, а выходы подключены к схеме НЕ - И, связанной через четвертую схему ИЛИ со второй схемой И, инверторы, соединенные со вторыми схемами ИЛИ и умножителями, седьмые схемы И, связанные с блоками развертки и вторыми схемами ИЛИ.

Кроме того, в предлагаемом устройстве умножители выполнены на накопительных сумматорах, что позволяет автономно на экране ЭЛТ формировать динамические изображения.

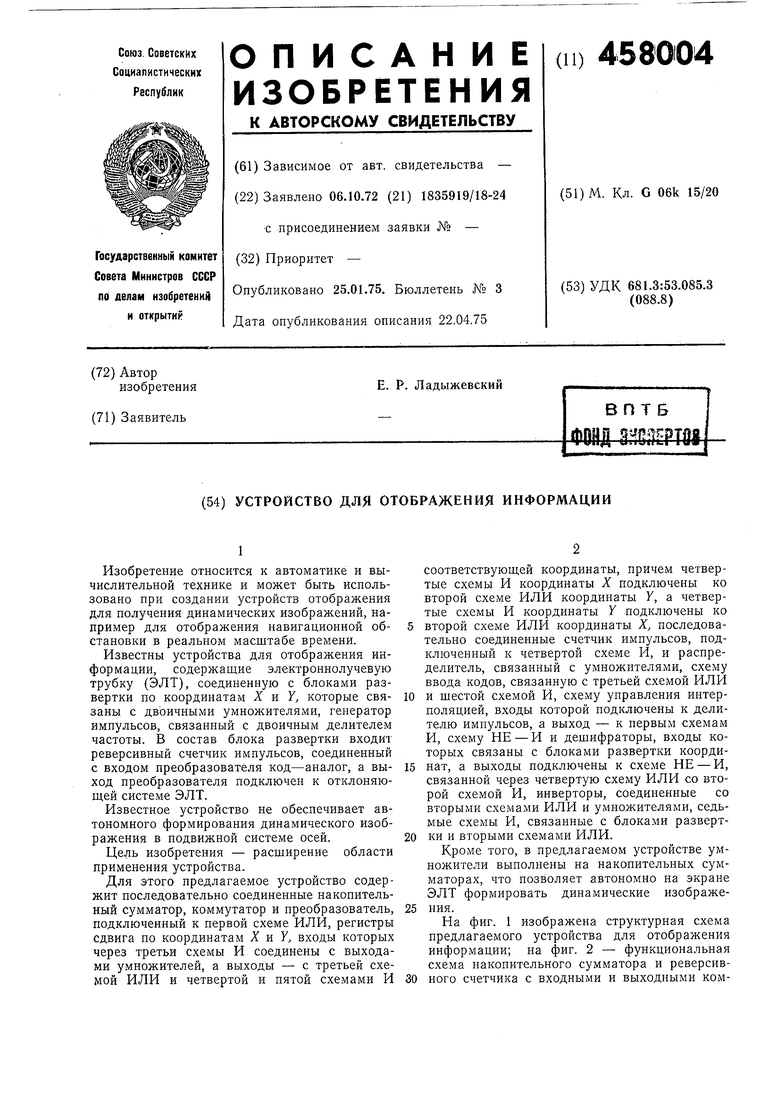

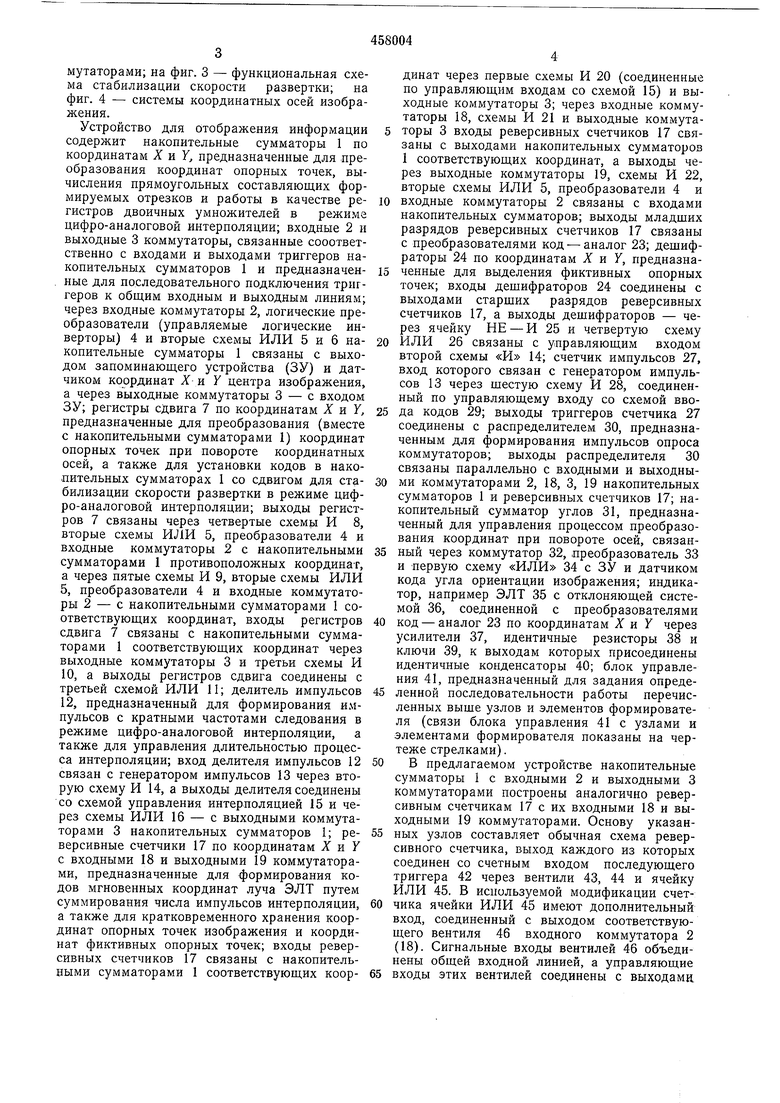

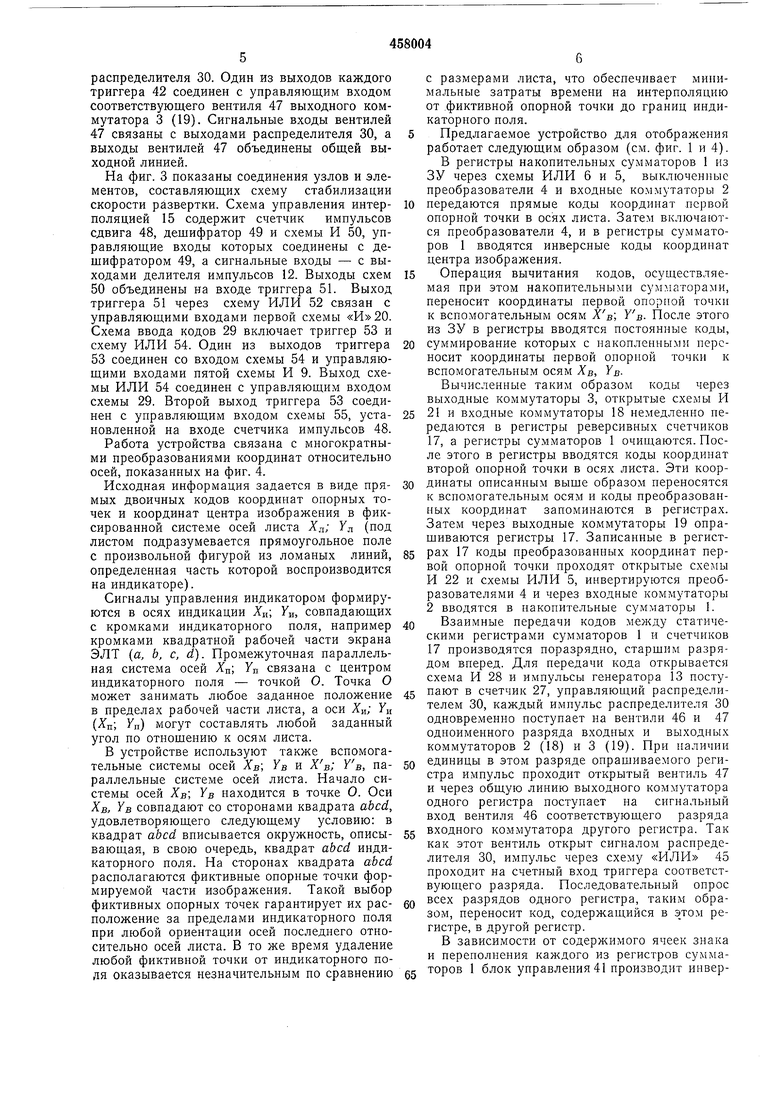

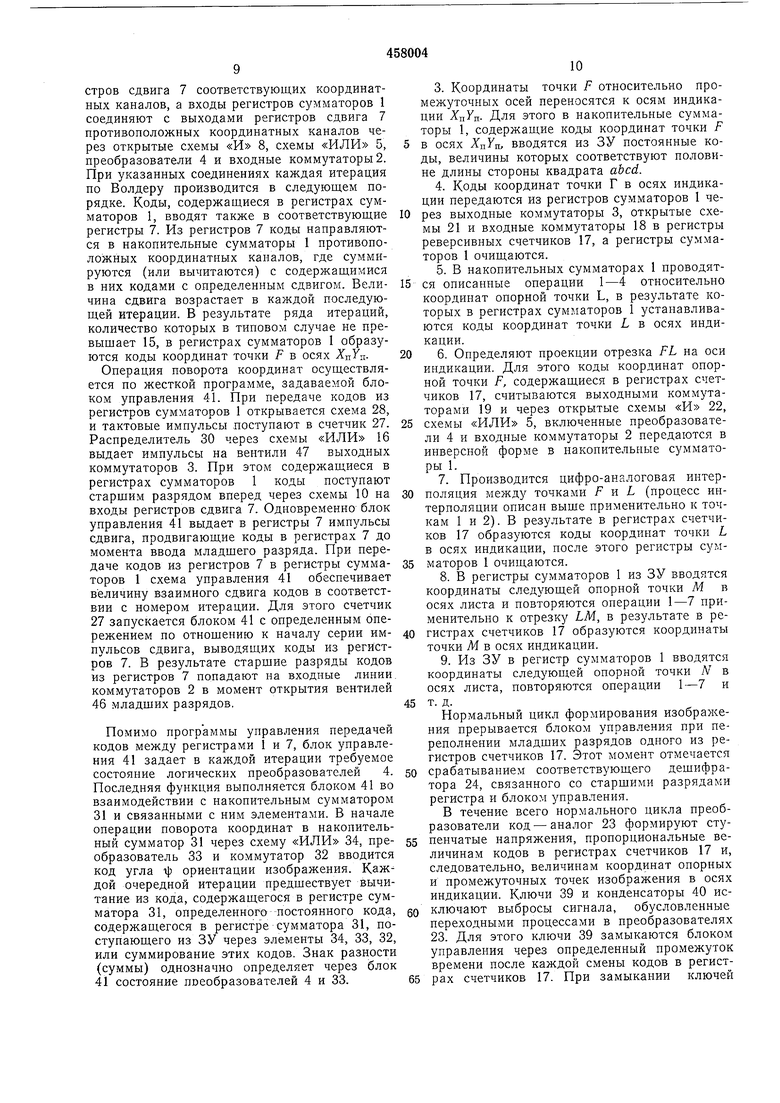

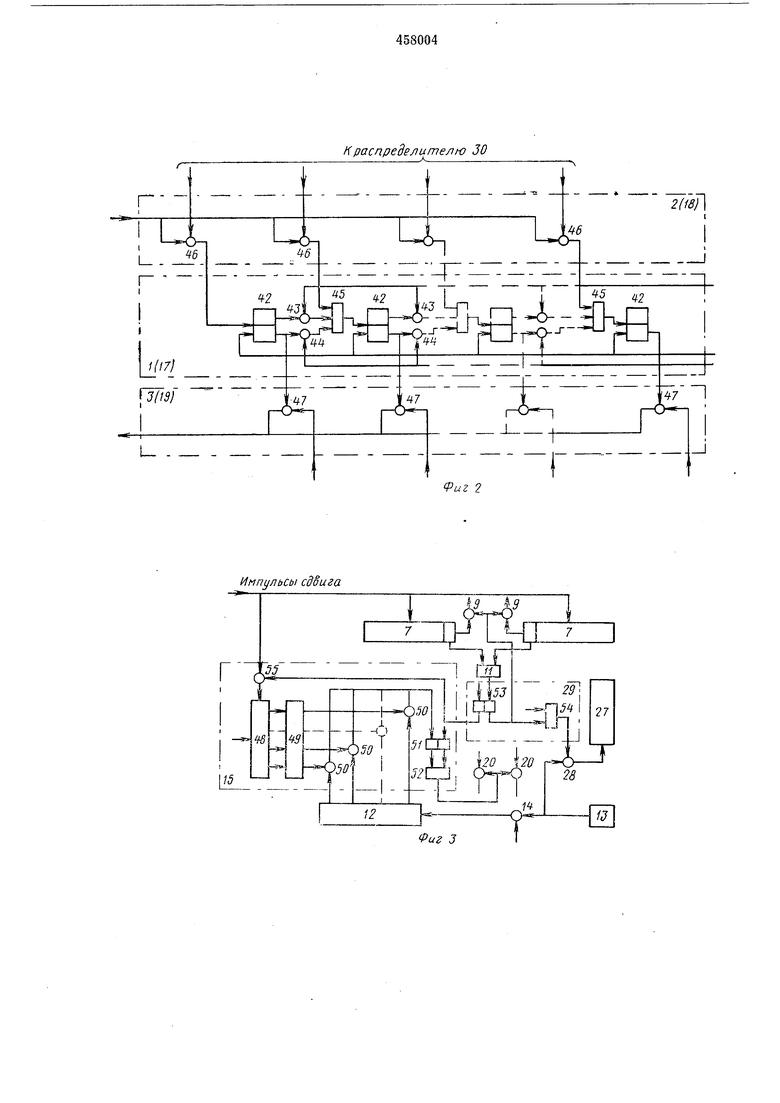

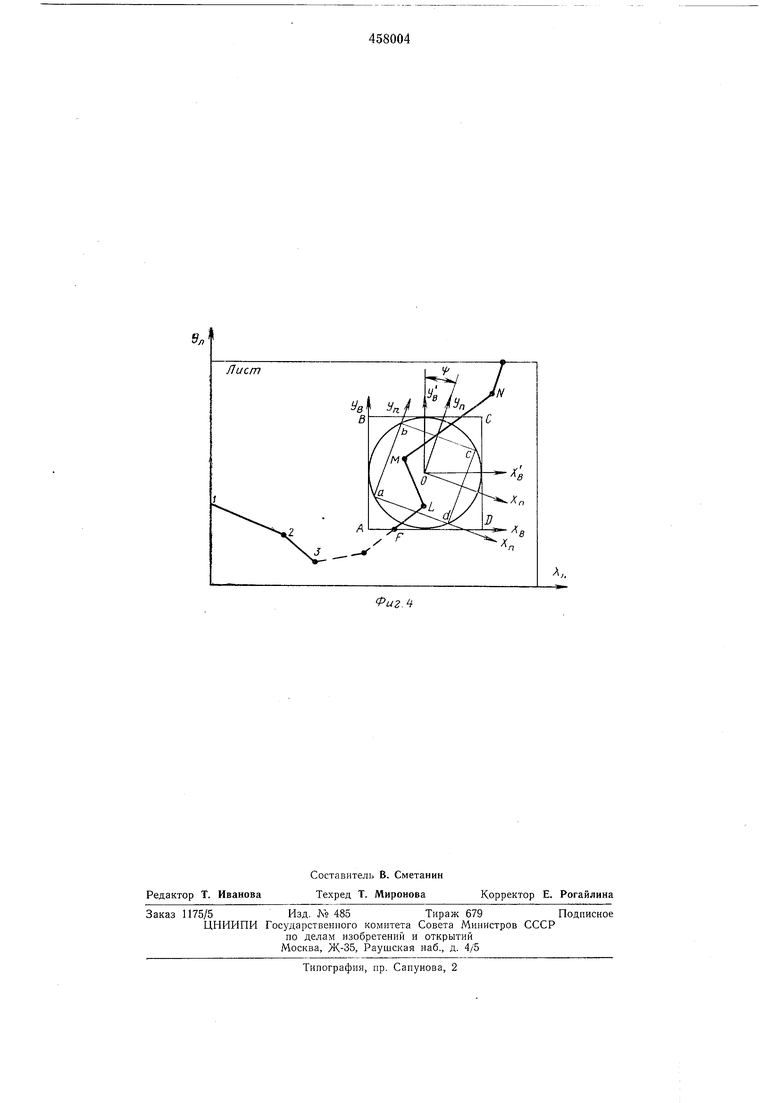

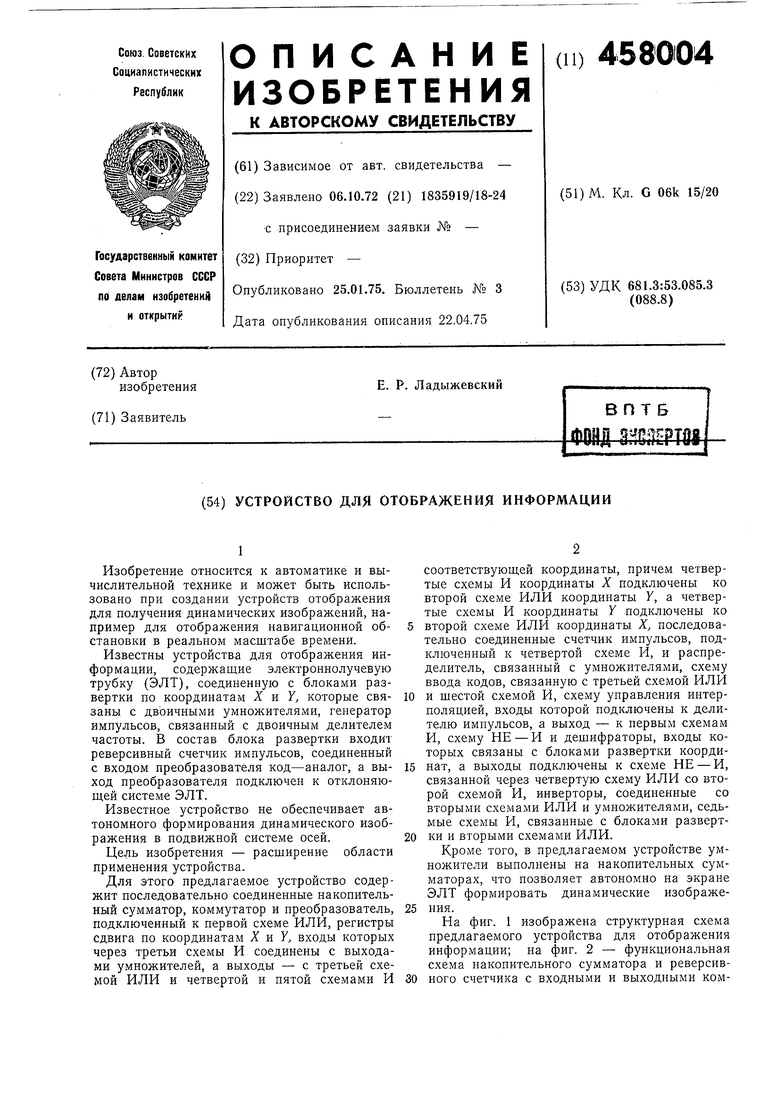

На фиг. 1 изображена структурная схема предлагаемого устройства для отображения информации; на фиг. 2 - функциональная схема накопительного сумматора и реверсивного счетчика с входными и выходными коммутаторами; на фиг. 3 - функциональная схема стабилизации скорости развертки; на фиг. 4 - системы координатных осей изображения.

Устройство для Отображения информации содержит накопительные сумматоры 1 по координатам X л Y, предназначенные для преобразования координат опорных точек, вычисления прямоугольных составляющих формируемых отрезков и работы в качестве регистров двоичных умножителей в режиме цифро-аналоговой интерполяции; входные 2 и выходные 3 коммутаторы, связанные сооответственно с входами и выходами триггеров накопительных сумматоров 1 и предназначенные для последовательного подключения триггеров к общим входным и выходным линиям; через входные коммутаторы 2, логические преобразователи (управляемые логические инверторы) 4 и вторые схемы ИЛИ 5 и 6 накопительные сумматоры 1 связаны с выходом запоминающего устройства (ЗУ) и датчиком координат X н Y центра изображения, а через выходные коммутаторы 3 - с входом ЗУ; регистры сдвига 7 по координатам X а Y, предназначенные для преобразования (вместе с накопительными сумматорами 1) координат опорных точек при повороте координатных осей, а также для установки кодов в накопительных сумматорах 1 со сдвигом для стабилизации скорости развертки в режиме цифро-аналоговой интерполяции; выходы регистров 7 связаны через четвертые схемь И 8, вторые схемы ИЛИ 5, преобразователи 4 и входные коммутаторы 2 с накопительными сумматорами 1 противоположных координат, а через пятые схемы И 9, вторые схемы ИЛИ 5, преобразователи 4 и входные коммутаторы 2 - с накопительными сумматорами 1 соответствующих координат, входы регистров сдвига 7 связаны с накопительными сумматорами 1 соответствующих координат через выходные коммутаторы 3 и третьи схемы И 10, а выходы регистров сдвига соединены с третьей схемой ИЛИ 11; делитель импульсов 12, предназначенный для формирования импульсов с кратными частотами следования в режиме цифро-аналоговой интерполяции, а также для управления длительностью процесса интерполяции; вход делителя импульсов 12 связан с генератором импульсов 13 через вторую схему И 14, а выходы делителя соединены со схемой управления интерполяцией 15 и через схемы ИЛИ 16 - с выходными коммутаторами 3 накопительных сумматоров 1; реверсивные счетчики 17 по координатам X к У с входными 18 и выходными 19 коммутаторами, предназначенные для формирования кодов мгновенных координат луча ЭЛТ путем суммирования числа импульсов интерполяции, а также для кратковременного хранения координат опорных точек изображения и координат фиктивных опорных точек; входы реверсивных счетчиков 17 связаны с накопительными сумматорами 1 соответствующих координат через первые схемы И 20 (соединенные по управляющим входам со схемой 15) и выходные коммутаторы 3; через входные коммутаторы 18, схемы И 21 и выходные коммутаторы 3 входы реверсивных счетчиков 17 связаны с выходад1И накопительных сумматоров 1 соответствующих координат, а выходы через выходные коммутаторы 19, схемы И 22, вторые схемы ИЛИ 5, преобразователи 4 и

входные коммутаторы 2 связаны с входами накопительных сумматоров; выходы младших разрядов реверсивных счетчиков 17 связаны с преобразователями код -аналог 23; дешифраторы 24 по координатам X к У, предназначенные для выделения фиктивных опорных точек; входы дешифраторов 24 соединены с выходами старших разрядов реверсивных счетчиков 17, а выходы дешифраторов - через ячейку НЕ - И 25 и четвертую схему

ИЛИ 26 связаны с управляющим входом второй схемы «И 14; счетчик импульсов 27, вход которого связан с генератором импульсов 13 через шестую схему И 28, соединенный по управляющему входу со схемой ввода кодов 29; выходы триггеров счетчика 27 соединены с распределителем 30, предназначенным для формирования импульсов опроса коммутаторов; выходы распределителя 30 связаны параллельно с входными и выходными коммутаторами 2, 18, 3, 19 накопительных сумматоров 1 и реверсивных счетчиков 17; накопительный сумматор углов 31, предназначенный для управления процессом преобразования координат при повороте осей, связанный через коммутатор 32, .преобразователь 33 и первую схему «ИЛИ 34 с ЗУ и датчиком кода угла ориентации изображения; индикатор, например ЭЛТ 35 с отклоняющей системой 36, соединенной с преобразователями

код - аналог 23 по координатам X и У через усилители 37, идентичные резисторы 38 и ключи 39, к выходам которых присоединены идентичные конденсаторы 40; блок управления 41, предназначенный для задания определенной последовательности работы перечисленных выше узлов и элементов формирователя (связи блока управления 41 с узлами и элементами формирователя показаны на чертеже стрелками).

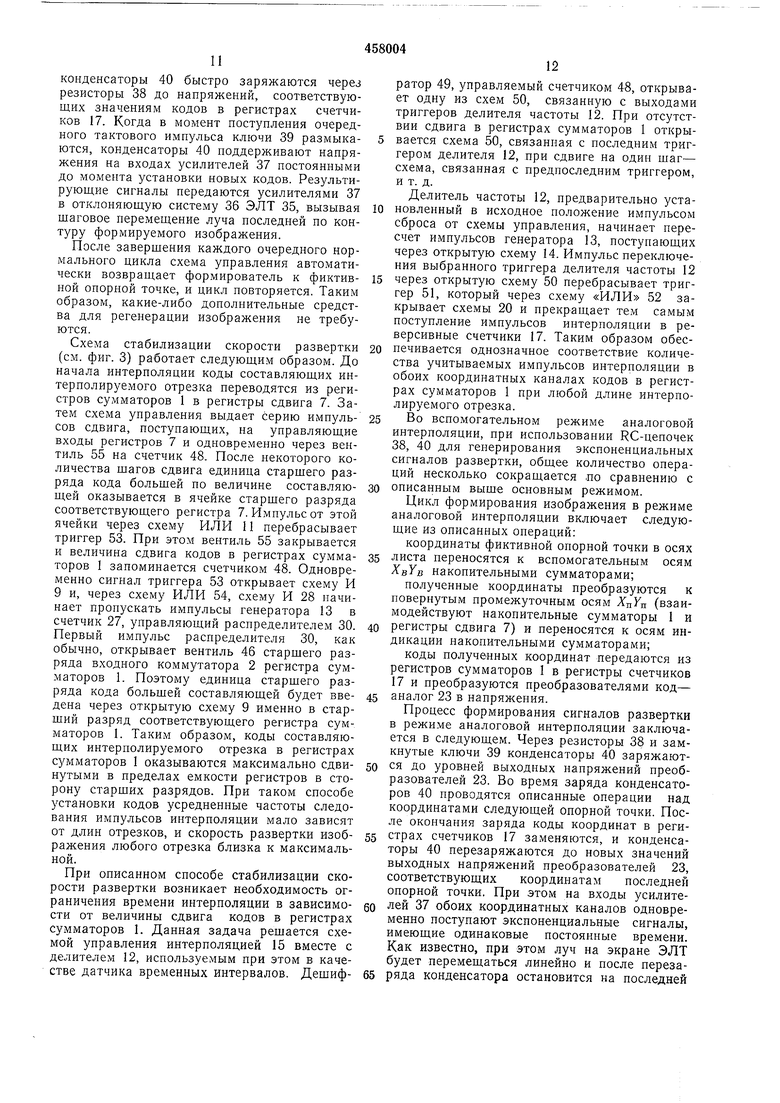

В предлагаемом устройстве накопительные сумматоры 1 с входными 2 и выходными 3 коммутаторами построены аналогично реверсивным счетчикам 17 с их входными 18 и выходными 19 коммутаторами. Основу указанных узлов составляет обычная схема реверсивного счетчика, выход каждого из которых соединен со счетным входом последующего триггера 42 через вентили 43, 44 и ячейку ИЛИ 45. В используемой модификации счетчика ячейки ИЛИ 45 имеют дополнительный вход, соединенный с выходом соответствующего вентиля 46 входного коммутатора 2 (18). Сигнальные входы вентилей 46 объединены общей входной линией, а управляющие

входы этих вентилей соединены с выходами

распределителя 30. Один из выходов каждого триггера 42 соединен с управляющим входом соответствующего вентиля 47 выходного коммутатора 3 (19). Сигнальные входы вентилей 47 связаны с выходами распределителя 30, а выходы вентилей 47 объединены общей выходной линией.

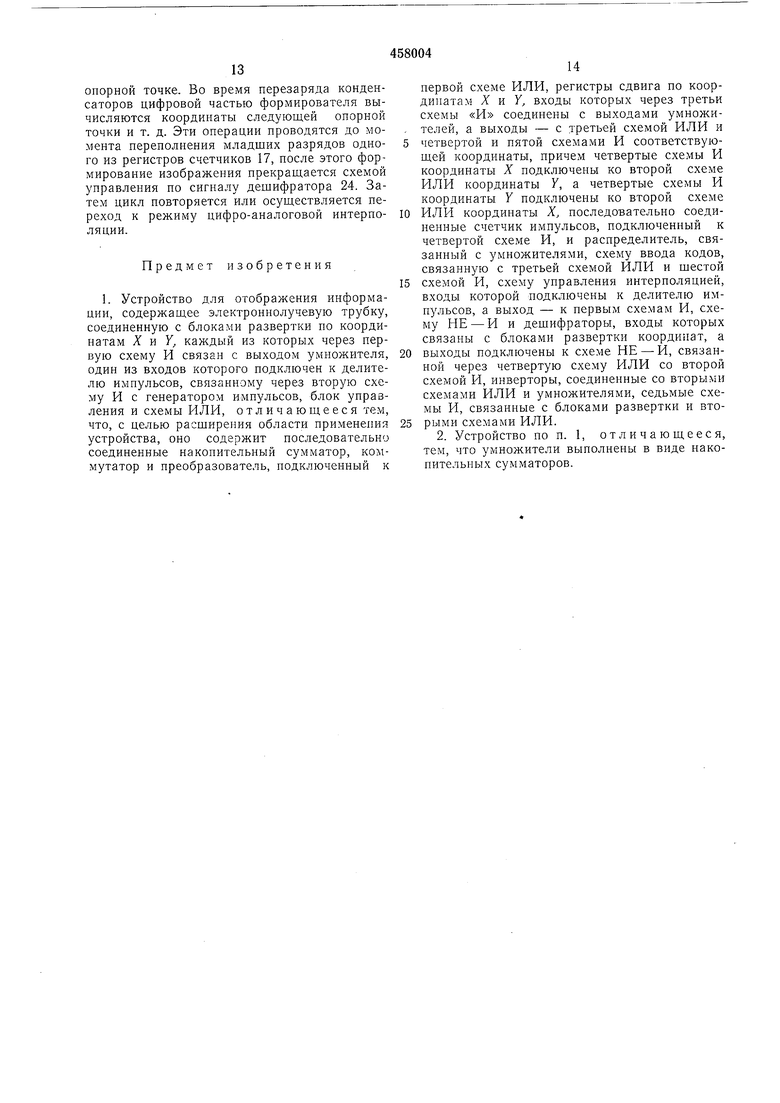

На фиг. 3 показаны соединения узлов и элементов, составляющих схему стабилизации скорости разв-ертки. Схема управления интерполяцией 15 содержит счетчик импульсов сдвига 48, дешифратор 49 и схемы И 50, управляющие входы которых соединены с дещифратором 49, а сигнальные входы - с выходами делителя импульсов 12. Выходы схем 50 объединены на входе триггера 51. Выход триггера 51 через схему ИЛИ 52 связан с управляющими входами первой схемы «И 20. Схема ввода кодов 29 включает триггер 53 и схему ИЛИ 54. Один из выходов триггера 53 соединен со входом схемы 54 и управляющими входами пятой схемы И 9. Выход схемы ИЛИ 54 соединен с управляющим входом схемы 29. Второй выход триггера 53 соединен с управляющим входом схемы 55, установленной на входе счетчика импульсов 48.

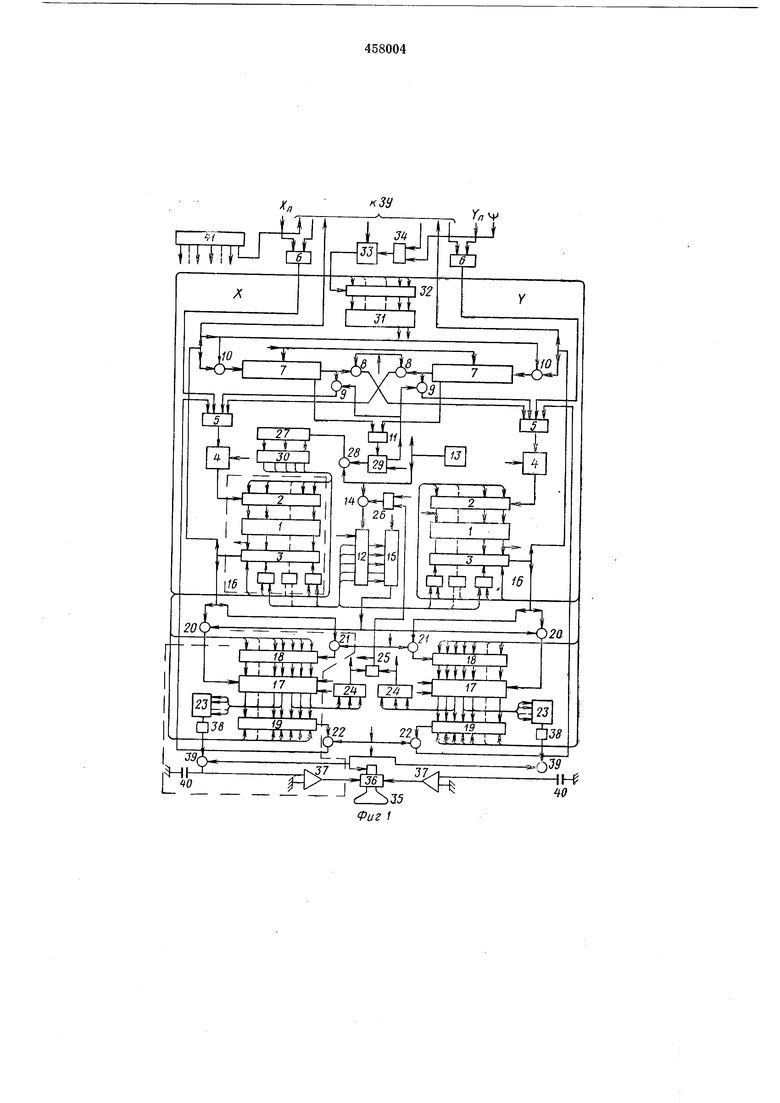

Работа устройства связана с многократными преобразованиями координат относительно осей, показанных на фиг. 4.

Исходная информация задается в виде прямых двоичных кодов координат опорных точек и координат центра изображения в фиксированной системе осей листа Уд (под листом подразумевается прямоугольное поле с произвольной фигурой из ломаных линий, определенная часть которой воспроизводится на индикаторе).

Сигналы управления индикатором формируются в осях индикации , УИ, совпадающих с кромками индикаторного поля, например кромками квадратной рабочей части экрана ЭЛТ (а, Ь, с, d). Промежуточная параллельная система осей Х, УП связана с центром индикаторного поля - точкой О. Точка О может занимать любое заданное положение в пределах рабочей части листа, а оси Хк; УИ (Хи, УП) могут составлять любой заданный угол по отнощению к осям листа.

В устройстве используют также вспомогательные системы осей Хв, Ув и Хв Ув, параллельные системе осей листа. Начало системы осей Хв, УВ находится в точке О. Оси Хв, УВ совпадают со сторонами квадрата abed, удовлетворяющего следующему условию: в квадрат abed вписывается окружность, описывающая, в свою очередь, квадрат abed индикаторного поля. На сторонах квадрата abed располагаются фиктивные опорные точки формируемой части изображения. Такой выбор фиктивных опорных точек гарантирует их расположение за пределами индикаторного поля при любой ориентации осей последнего относительно осей листа. В то же время удаление любой фиктивной точки от индикаторного подя оказывается незначительным по сравнению

с размерами листа, что обеспечивает минимальные затраты времени на интерполяцию от фиктивной опорной точки до границ индикаторного поля.

Предлагаемое устройство для отображения

работает следующим образом (см. фиг. 1 и 4).

В регистры накопительных сумматоров 1 из

ЗУ через схемы ИЛИ 6 и 5, выключенные

преобразователи 4 и входные коммутаторы 2

передаются прямые коды координат первой опорной точки в осях листа. Затем включаются преобразователи 4, и в регистры сумматоров 1 вводятся инверсные коды координат центра изображения.

Операция вычитания кодов, осуществляемая при этом накопительными сумматорами, переносит координаты первой опорной точки к вспомогательным осям в; Ув. После этого из ЗУ в регистры вводятся постоянные коды,

суммирование которых с накопленными переносит координаты первой опорной точки к вспомогательным осям Хв, УВВычисленные таким образом коды через выходные коммутаторы 3, открытые схемы И

21 и входные коммутаторы 18 немедленно передаются в регистры реверсивных счетчиков 17, а регистры сумматоров 1 очищаются. После этого в регистры вводятся коды координат второй опорной точки в осях листа. Эти координаты описанным выше образом переносятся к вспомогательным осям и коды преобразованных координат запоминаются в регистрах. Затем через выходные коммутаторы 19 опрашиваются регистры 17. Записанные в регистpax 17 коды преобразованных координат первой опорной точки проходят открытые схемы И 22 и схемы ИЛИ 5, инвертируются преобразователями 4 и через входные коммутаторы 2 вводятся в накопительные сумматоры 1.

Взаимные передачи кодов между статическими регистрами сумматоров 1 и счетчиков 17 производятся поразрядно, старшим разрядом вперед. Для передачи кода открывается схема И 28 и импульсы генератора 13 поступают в счетчик 27, управляющий распределителем 30, каждый импульс распределителя 30 одновременно поступает на вентили 46 и 47 одноименного разряда входных и выходных коммутаторов 2 (18) и 3 (19). При наличии

единицы в этом разряде опрашиваемого регистра импульс проходит открытый вентиль 47 и через обшую линию выходного коммутатора одного регистра поступает на сигнальный вход вентиля 46 соответствующего разряда

входного коммутатора другого регистра. Так как этот вентиль открыт сигналом распределителя 30, импульс через схему «ИЛИ 45 проходит на счетный вход триггера соответствующего разряда. Последовательный опрос

всех разрядов одного регистра, таким образом, переносит код, содержащийся в регистре, в другой регистр.

В зависимости от содержимого ячеек знака и переполнения каждого из регистров сумматоров 1 блок управления 41 производит инверсию мантиссы образовавшегося кода или циклический перенос единицы и из ячейки переполнения. В результате всех описанных операций в регистрах сумматоров 1 устанавливаются прямые коды проекций первого отрезка на оси листа, а в регистрах счетчиков 17 - прямые коды коордипат начальной точки этого отрезка во вспомогательной системе координат.

Следующей операцией является цифро-аналоговая линейная интерполяция между первой и второй опорными точками. При этом регистры накопительных сумматоров 1 работают как регистры двоичных умножителей, а вентили выходных коммутаторов 3 - как вентили двоичных умножителей. Интерполяция начинается после открытия схемы 14, соединяющей двоичный делитель частоты 12 с генератором импульсов 13. Последовательности импульсов с кратными частотами следования от триггеров делителя 12 поступают через схемы «ИЛИ 16 на сигнальные входы схем 47 выходных коммутаторов 3. При этом на выходных линиях коммутаторов возникают последовательности импульсов, усредненные частоты следования которых пропорциональны величинам прямоугольных составляющих интерполируемого отрезка. Длительность процесса интерполяции задается схемой 15, управляющей первой схемой «И 20 таким образом, что общее количество импульсов, поступивших на входы реверсивных счетчиков 17, является число - импульсным выражением величин указанных составляющих. В зависимости от состояния знаковых разрядов регистров сумматоров 1 реверсивные счетчики 17 работают на сложение или вычитание, суммируя или вычитая число поступивших импульсов и коды координат начальной точки отрезка, которые ранее были записаны в регистрах счетчиков 17. При этом последовательности образующихся в счетчиках 17 кодов соответствуют последовательности кодов координат точек интерполируемого отрезка. Коды, образовавщиеся в счетчиках 17 в момент окончания интерполяции, являются кодами координат точки конца первого отрезка. Далее регистры сумматоров 1 очищаются и в них из ЗУ передаются коды координат следующей опорной точки, которые переносятся к вспомогательным осям аналогично координатам предыдущей опорной точки и в них описанным выше образом формируются коды прямоугольных составляющих второго отрезка. Производится линейная интерполяция между точками 2 и 3 и т. д. Описанные чередующиеся операции установки кодов в регистрах сумматоров 1 и счетчиков 17 и иптерполяции производятся до определения фиктивной опорной точки изображения.

Фиктивная опорная точка F находится в пересечении очередного интерполируемого отрезка с периметром квадрата abed. Координаты фиктивной опорной точки образуются в регистрах счетчиков 17 при остановке процесса

иптерполяции в момент совпадения значений мгновенных координат в регистрах счетчиков 17 с координатами одной из точек периметра квадрата. Это условие выполняется, когда обе величины в счетчиках 17 оказываются меньше определенного предела, соответствующего длине стороны квадрата abed. Указанный предел определяется очищением старших разрядов счетчиков 17, состояние которых

контролируется дешифраторами 24. Момент срабатывания обоих дещифраторов отмечается схемой ПЕ - И 25, запирающей через схемы ИЛИ 26 схемы «И 14 и прерывающей тем самым процесс интерполяции. Коды, накопленные к этому моменту в регистрах счетчиков 17, являются кодами координат фиктивной опорной точки в системе вспомогательных осей. Эти коды через выходные коммутаторы 19, схемы «И 22, схемы «ИЛИ 5,

преобразователи 4 и входные коммутаторы 2 переводятся в накопительные сумматоры 1, после чего регистры счетчиков 17 полностью очищаются. В накопительных сумматорах I координаты точки F двумя операциями суммирования последовательно переносятся к осям Хв, У в и осям листа. Полученные коды координат фиктивной опорной точки в осях листа через выходные коммутаторы 3 передаются из регистров сумматоров 1 в ЗУ, а регистры сумматоров .очищаются.

Частота проведения вычисления координат фиктивной опорной точки зависит от скорости перемещения центра изображения по полю листа; в типовом случае фиктивная опорная

точка определяется через интервалы времени порядка нескольких десятков секунд. В промежутках координаты фиктивной опорной точки, интерпретируемой как первая опорная точка формируемого изображения, выдаются из

ЗУ. Исходя из этого, рассматривают нормальный цикл формирования изображения (ломаная линия FL, MN на фиг. 4).

Пормальный цикл формирования изображения состоит из следующей последовательности

операций:

1.Определяют координаты точки F относительно вспомогательных осей ХвУв- Для этого в регистры накопительных сумматоров 1 через схемы «ИЛИ 6 и 5, выключенные логические преобразователи 4 и входные коммутаторы 2 вводят из ЗУ прямые коды координат точки F в осях листа. Затем в регистры сумматоров I через схемы ИЛИ 6 и 5, включенные преобразователи 4 и входные коммутаторы 2 вводят инверсные коды точки О центра изображения. Суммы указанных кодов соответствуют координатам точки F в осях

Хв YB2.Координаты точки F в осях ХвУв преобразуют к промежуточным осям . Преобразование координат выполняют по известному тригонометрическому алгоритму Волдера. Для этого выходы регистров накопительных сумматоров через выходные коммутаторы 3 и

открытые схемы 10 соединяют входами реги9

стров сдвига 7 соответствующих координатных каналов, а входы регистров сумматоров 1 соединяют с выходами регистров сдвига 7 противоположных координатных каналов через открытые схемы «И 8, схемы «ИЛИ 5, преобразователи 4 и входные коммутаторы 2. При указанных соединениях каждая итерация по Волдеру производится в следующем порядке. Коды, содержащиеся в регистрах сумматоров 1, вводят также в соответствующие регистры 7. Из регистров 7 коды направляются в накопительные сумматоры 1 противоположных координатных каналов, где суммируются (или вычитаются) с содержащимися в них кодами с определенным сдвигом. Величина сдвига возрастает в каждой последующей итерации. В результате ряда итераций, количество которых в типовом случае не превышает 15, в регистрах сумматоров 1 образуются коды координат точки F в осях п пОперация поворота координат осуществляется но жесткой программе, задаваемой блоком управления 41. При передаче кодов из регистров сумматоров 1 открывается схема 28, и тактовые импульсы поступают в счетчик 27. Распределитель 30 через схемы «ИЛИ 16 выдает импульсы на вентили 47 выходных коммутаторов 3. При этом содержащиеся в регистрах сумматоров 1 коды поступают старщим разрядом вперед через схемы 10 на входы регистров сдвига 7. Одновременно блок управления 41 выдает в регистры 7 импульсы сдвига, продвигающие коды в регистрах 7 до момента ввода младшего разряда. При передаче кодов из регистров 7 в регистры сумматоров 1 схема управления 41 обеспечивает величину взаимного сдвига кодов в соответствии с номером итерации. Для этого счетчик 27 запускается блоком 41 с определенным опережением по отношению к началу серии импульсов сдвига, выводящих коды из регистров 7. В результате старшие разряды кодов нз регистров 7 попадают на входные линии, коммутаторов 2 в момент открытия вентилей 46 младших разрядов.

Помимо программы управления передачей кодов между регистрами 1 и 7, блок управления 41 задает в каждой итерации требуемое состояние логических преобразователей 4. Последняя функция выполняется блоком 41 во взаимодействии с накопительным сумматором 31 и связанными с ним элементами. В начале операции поворота координат в накопительный сумматор 31 через схему «ИЛИ 34, преобразователь 33 и коммутатор 32 вводится код угла ориентации изображения. Каждой очередной итерации предшествует вычитание из кода, содержащегося в регистре сумматора 31, определенного -постоянного кода, содержащегося в регистре сумматора 31, поступающего из ЗУ через элементы 34, 33, 32, или суммирование этих кодов. Знак разности (суммы) однозначно определяет через блок 41 состояние поеобразователей 4 и 33.

10

3.Координаты точки F относительно промежуточных осей переносятся к осям индикации ХпУп- Для этого в накопительные сумматоры 1, содержащие коды координат точки -F

в осях вводятся из ЗУ постоянные коды, величины которых соответствуют половине длины стороны квадрата abed.

4.Коды координат точки Г в осях индикации передаются из регистров сумматоров 1 через выходные коммутаторы 3, открытые схемы 21 и входные коммутаторы 18 в регистры реверсивных счетчиков 17, а регистры сумматоров I очищаются.

5.В накопительных сумматорах 1 проводятся описанные операции 1-4 относительно

координат опорной точки L, в результате которых в регистрах сумматоров 1 устанавливаются коды координат точки L в осях индикации.

6. Определяют проекции отрезка FL на оси индикации. Для этого коды координат опорной точки F, содержащиеся в регистрах счетчиков 17, считываются выходными коммутаторами 19 и через открытые схемы «И 22,

схемы «ИЛИ 5, включенные преобразователи 4 и входные коммутаторы 2 передаются в инверсной форме в накопительные сумматоры 1.

7.Производится цифро-аналоговая интерполяция между точками F vi L (процесс интерполяции описан выше применительно к точкам 1 и 2). В результате в регистрах счетчиков 17 образуются коды координат точки L в осях индикации, после этого регистры сумматоров 1 очищаются.

8.В регистры сумматоров 1 из ЗУ вводятся координаты следующей опорной точки М в осях листа и повторяются операции 1-7 применительно к отрезку LM, в результате в регистрах счетчиков 17 образуются координаты точки М в осях индикации.

9.Из ЗУ в регистр сумматоров 1 вводятся координаты следующей опорной точки Л в осях листа, повторяются операции 1-7 и

т. д.

Пормальный цикл формирования изображения прерывается блоком управления при переполнении младших разрядов одного из регистров счетчиков 17. Этот момент отмечается

срабатыванием соответствующего дещифратора 24, связанного со старшими разрядами регистра и блоком управления.

В течение всего нормального цикла преобразователи код - аналог 23 формируют ступенчатые напряжения, пропорциональные величинам кодов в регистрах счетчиков 17 и, следовательно, величинам координат опорных и промежуточных точек изображения в осях индикации. Ключи 39 и конденсаторы 40 исключают выбросы сигнала, обусловленные переходными процессами в преобразователях 23. Для этого ключи 39 замыкаются блоком управления через определенный промежуток времени после каждой смены кодов в регистpax счетчиков 17. При замыкании ключей

11

конденсаторы 40 быстро заряжаются через резисторы 38 до напряжений, соответствующих значениям кодов в регистрах счетчиков 17. Когда в момент поступления очередного тактового импульса ключи 39 размыкаются, конденсаторы 40 поддерживают напряжения на входах усилителей 37 постоянными до момента установки новых кодов. Результируюш,ие сигналы передаются усилителями 37 в отклоняющую систему 36 ЭЛТ 35, вызывая щаговое перемещение луча последней по контуру формируемого изображения.

После заверщения каждого очередного нормального цикла схема управления автоматически возвращает формирователь к фиктивной опорной точке, и пикл повторяется. Таким образом, какие-либо дополнительные средства для регенерации изображения не требуются.

Схема стабилизации скорости развертки (см. фиг. 3) работает следующим образом. До начала интерполяции коды составляющих интерполируемого отрезка переводятся из регистров сумматоров 1 в регистры сдвига 7. Затем схема управления выдает серию импульсов сдвига, поступающих, на управляющие входы регистров 7 и одновременно через вентиль 55 на счетчик 48. После некоторого количества щагов сдвига единица старщего разряда кода больщей по величине составляющей оказывается в ячейке старщего разряда соответствующего регистра 7. Импульс от этой ячейки через схему ИЛИ 11 перебрасывает триггер 53. При этом вентиль 55 закрывается и величина сдвига кодов в регистрах сумматоров 1 запоминается счетчиком 48. Одновременно сигнал триггера 53 открывает схему И 9 и, через схему ИЛИ 54, схему И 28 начинает пропускать импульсы генератора 13 в счетчик 27, управляющий распределителем 30. Первый импульс распределителя 30, как обычно, открывает вентиль 46 старщего разряда входного коммутатора 2 регистра сум.маторов 1. Поэтому единица старщего разряда кода больщей составляющей будет введена через открытую схему 9 именно в старщий разряд соответствующего регистра сумматоров 1. Таким образом, коды составляющих интерполируемого отрезка в регистрах сумматоров 1 оказываются максимально сдвинутыми в пределах емкости регистров в сторону старщих разрядов. При таком способе установки кодов усредненные частоты следования импульсов интерполяции мало зависят от длин отрезков, и скорость развертки изображения любого отрезка близка к максимальной.

При описанном способе стабилизации скорости развертки возникает необходимость ограничения времени интерполяции в зависимости от величины сдвига кодов в регистрах сумматоров 1. Данная задача рещается схемой управления интерполяцией 15 вместе с делителем 12, используемым при этом в качестве датчика временных интервалов. Дешиф12

ратор 49, управляемый счетчиком 48, открывает одну из схем 50, связанную с выходами триггеров делителя частоты 12. При отсутствии сдвига в регистрах сумматоров 1 открывается схема 50, связанная с последним триггером делителя 12, при сдвиге на один шаг- схема, связанная с предпоследним триггером, и т. д. Делитель частоты 12, предварительно установленный в исходное положение импульсом сброса от схемы управления, начинает пересчет импульсов генератора 13, поступающих через открытую схему 14. Импульс переключения выбранного триггера делителя частоты 12

через открытую схему 50 перебрасывает триггер 51, который через схему «ИЛИ 52 закрывает схемы 20 и прекращает тем са.мым поступление импульсов интерполяции в реверсивные счетчики 17. Таким образом обеспечивается однозначное соответствие количества учитываемых импульсов интерполяции в обоих координатных каналах кодов в регистрах сумматоров 1 при любой длине интерполируемого отрезка.

Во вспомогательном режиме аналоговой интерполяции, при использовании RC-цепочек 38, 40 для генерирования экспоненциальных сигналов развертки, общее количество операций несколько сокращается ло сравнению с

описанным выще основным режимом.

Цикл формирования изображения в режиме аналоговой интерполяции включает следующие из описанных операций: координаты фиктивной опорной точки в осях

листа переносятся к вспомогательным осям ХвУв накопительными сумматорами;

полученные координаты преобразуются к повернутым промежуточным осям (взаимодействуют накопительные сумматоры 1 и

регистры сдвига 7) и переносятся к осям индикации накопительными сумматорами;

коды полученных координат передаются из регистров сумматоров I в регистры счетчиков 17 и преобразуются преобразователями код-

аналог 23 в напряжения.

Процесс формирования сигналов развертки в режиме аналоговой интерполяции заключается в следующем. Через резисторы 38 и замкнутые ключи 39 конденсаторы 40 заряжаются до уровней выходных напряжений преобразователей 23. Во время заряда конденсаторов 40 проводятся описанные операции над координатами следующей опорной точки. После окончания заряда коды координат в регистрах счетчиков 17 заменяются, и конденсаторы 40 перезаряжаются до новых значений выходных напряжений преобразователей 23, соответствующих координатам последней опорной точки. При этом на входы усилителей 37 обоих координатных каналов одновременно поступают экспоненциальные сигналы, имеющие одинаковые постоянные времени. Как известно, при этом луч на экране ЭЛТ будет перемещаться линейно и после перезаряда конденсатора остановится на последней

13

опорной точке. Во время перезаряда конденсаторов цифровой частью формирователя вычисляются координаты следующей опорной точки и т. д. Эти операции проводятся до момента переполнения младших разрядов одного из регистров счетчиков 17, после этого формирование изображения прекращается схемой управления по сигналу дещифратора 24. Затем цикл повторяется или осуществляется переход к режиму цифро-аналоговой интерполяции.

Предмет изобретения

1. Устройство для отображения информации, содержащее электроннолучевую трубку, соединенную с блоками развертки по координатам X и 7 каждый из которых через первую схему И связан с выходом умножителя, один из входов которого подключен к делителю импульсов, связанному через вторую схему И с генератором импульсов, блок управления и схемы ИЛИ, отличающееся тем, что, с целью расщирения области применения устройства, оно содержит последовательно соединенные накопительный сумматор, коммутатор и преобразователь, подключенный к

14

первой схеме ИЛИ, регистры сдвига по координатам X и Y, входы которых через третьи схемы «И соединены с выходами умножителей, а выходы - с третьей схемой ИЛИ и

четвертой и пятой схемами И соответствующей координаты, причем четвертые схемы И координаты X подключены ко второй схеме ИЛИ координаты Y, а четвертые схемы И координаты Y подключены ко второй схеме

ИЛИ координаты X, последовательно соединенные счетчик импульсов, подключенный к четвертой схеме И, и распределитель, связанный с умножителями, схему ввода кодов, связанную с третьей схемой ИЛИ и гнестой

схемой И, схему управления интерполяцией, входы которой подключены к делителю импульсов, а выход - к первым схемам И, схему НЕ - И и дещифраторы, входы которых связаны с блоками развертки координат, а

выходы подключены к схеме НЕ - И, связанной через четвертую схему ИЛИ со второй схемой И, инверторы, соединеиные со вторыми схемами ИЛИ и умножителями, седьмые схемы И, связанные с блоками развертки и вторыми схемами ИЛИ.

2. Устройство по п. 1, отличающееся, тем, что умножители выполнены в виде накопительных сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображенияиНфОРМАции | 1976 |

|

SU798961A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1525723A2 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300542A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1513506A2 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

хпппх

7 СЖ

т:

Г

)20

J5

К распределителю 30

Г I

Импульсы сдоига

2(kJ

Фиг vJt r-ijL У1Л ь гЛЬВ- 1± 1 ггп

Авторы

Даты

1975-01-25—Публикация

1972-10-06—Подача