Изобретение относится к устройствам автоматики и вычислительной техники.

Известны вычитатели лоследовательностей импульсов, содержащие ферритовые кольца с ППГ и блокинг-генераторы, которые содержат значительное количество активных и пассивных элементов и имеют ограничения как по нижнему, так и по верхнему -пределу частот.

В предложенном вычитателе последовательностей импульсов применен двухотверстный трансфлюксор со входными обмотками, по которым происходит блокировка (установка в «О) и разблокировка (установка в «1) трансфлюксора, обмоткой считывания и выходной обмоткой, к которой через диод подключей накопительный конденсатор.

Это позволяет упростить устройство и снять ограничение по нижнему пределу частот.

Вычитатель осуществляет преобразование двух последовательностей имнульсов с частотами /1 (уменьшаемое) и f. (вычитаемое) в последовательность импульсов с частотой fa (раз-кость).

Вычитатель ра-ботает по следующему принципу: Каждый импульс вычитаемой последовательности воздействует на схему таким образом, что следующий за ним во времени первый импульс уменьщаемой последовательности на выход вычитателя не проходит. Следовательно, количество выходных импульсов за определенный интервал времени равно разности между количеством импульсов уменьщаемой н вычитаемой последовательности за тот же интервал времени.

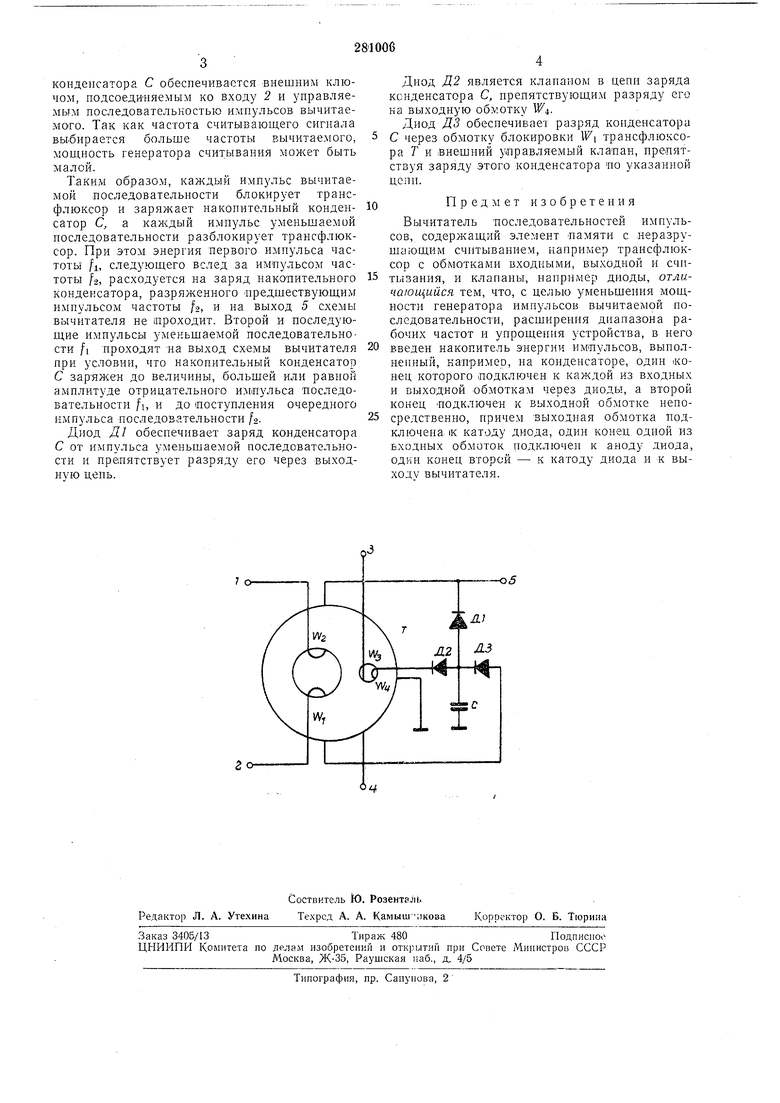

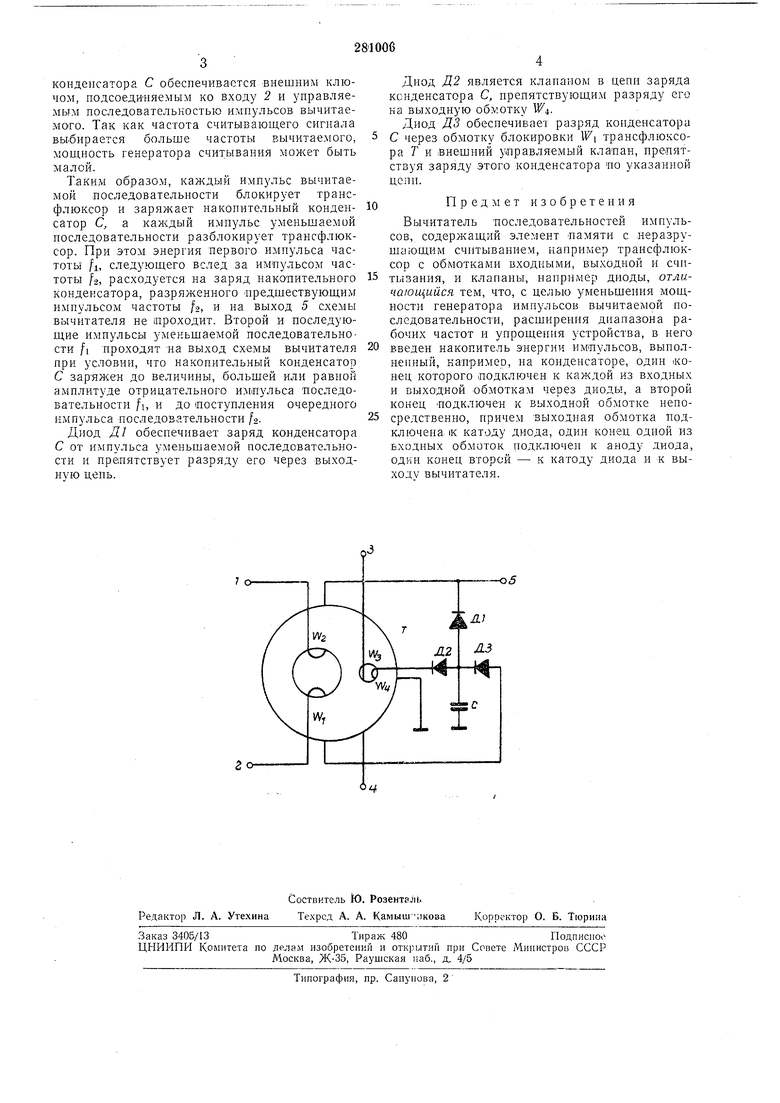

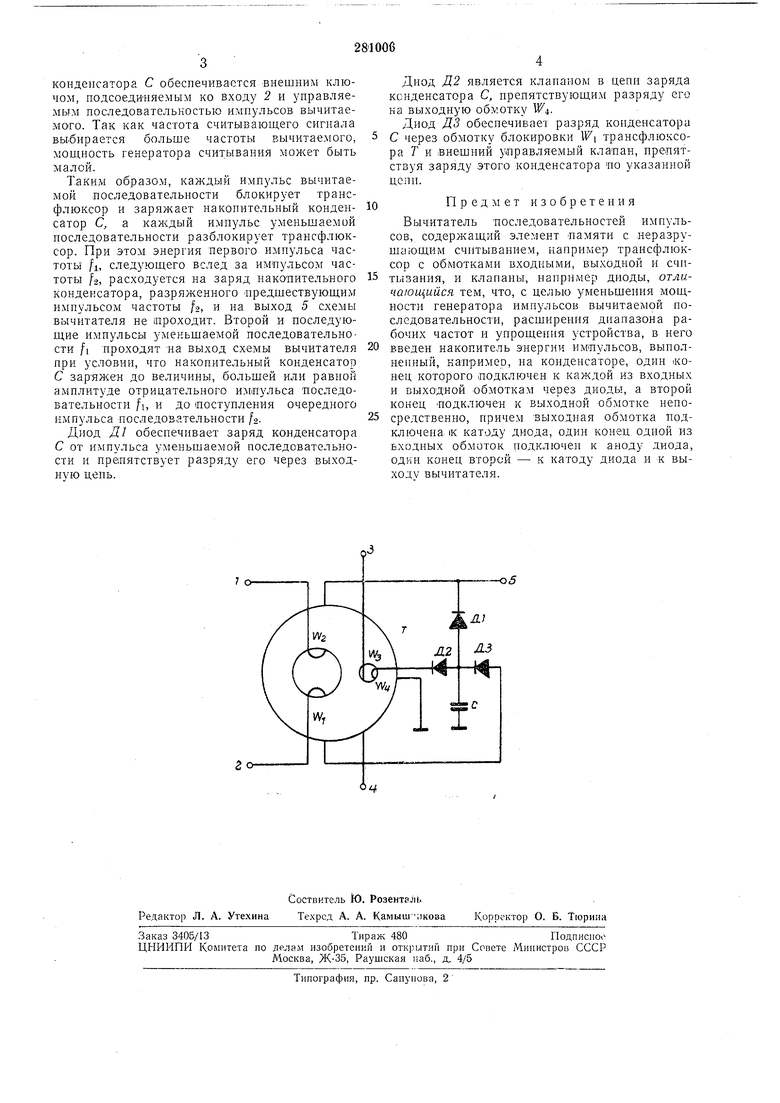

Принципиальная схема вычитателя последовательностей импульсов -приведена на чертеже.

Установочные обмотки для блокировки W, и разблокировки Ws трансфтюксора Т -проходят через больщое отверстие, считывающая Ws и выходная Wi обмот1ки - через малое отверстие.

.Отрицательные импульсы уменьшаемой последовательности с частотой /1 подаются на вход } и разблокируют трансфлюксор, а положительные импульсы вычитаемой последовательности с частотой fv подаются на вход 2 и блокируют трансфлюксор.

Считывающий сигнал подается непрерывно на входы 5 и от генератора считыва-ния. При разблокированном состоянии трансфлюксора Т нако-пительный конденсатор С заряжается до величины амплитуды выходных импульсов. Время заряда -конденсатора -при выбранных элементах схемы определяется мощностью считывающих импульсов и частотой их следова-ния. ,

конденсатора С обеснечиваотся внешним ключом, подсоединяемым ко входу 2 и управляемым последовательностью импульсов вычитаемого. Так как частота считывающего сигнала выбирается больше частоты вычитаемого, мощность генератора считывания может быть малой.

Таким образом, каждый импульс вычитаемой последовательности блокирует траисфлюксор и заряжает накопительный конденсатор С, а каж;дый импульс уменьшаемой носледовательности разблокирует трансфлюксор. При этом энергия первого импульса частоты /1, следующего вслед за импульсом частоты f-, расходуется на заряд накопительного конденсатора, разряженного предществующим импульсом частоты /а, и на выход 5 схемы вычитателя не проходит. Второй и последующие импульсы уменьшаемой последовательности /1 проходят на выход схемы вычитателя при условии, что накопительный конденсатор С заряжен до величины, большей или равной амплитуде отрицательного импульса последовательности fi, и до поступления очередного импульса последовательности /аДиод Д} обеспечивает заряд конденсатора С от импульса уменьшаемой последовательности и препятствует разряду его через ВЫХОДНУЮ цепь.

Дпод Д2 является клапаном в цепи заряда конденсатора С, нрепятствующим разряду его на выходную обмотку W.

Диод ДЗ обеспечивает разряд конденсатора С через обмотку блокировки Wi трансфлюксора Г и внешний заправляемый клапан, препятствуя заряду этого конденсатора по указанной цепи.

Предмет изобретения

Вычитатель последовательностей импульсов, содержащий элемент памяти с неразрушающим считыванием, например трансфлюксор с обмотками входными, выходной и счптызания, и клапаны, например диоды, отличающийся тем, что, с целью уменьшения мощности генератора импульсов вычитаемой последовательности, расширения диапазона рабочих частот и упрощения устройства, в него

введен накопитель энергии импульсов, выполненный, напримео, на конденсаторе, один конец которого подключен к каждой из входных и выходной обмоткам через диоды, а второй конец подключен к выходной обмотке непосредственно, причем выходная обмотка подключена 1К катоду диода, один конец одной из входных обмоток подключен к аноду диода, один конец второй - к катоду диода и к ВЫХОДУ вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТГХИИЧЕСКАЙЬИ&ЛИОТИА | 1970 |

|

SU271576A1 |

| ТРОИЧНЫЙ ЭЛЕМЕНТБс:'Со;о:7НАЛ [;--т^;ГГг-;-,-.,у;.':--^ч;др(1- .. u..5i .It^ . J.i>&;.'; ;«,,ldr1ii' | 1971 |

|

SU319074A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU350157A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ ЧИСЕЛ в РЕКУРРЕНТНОЛ!КОДЕ | 1972 |

|

SU353346A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ЧИСЕЛ В КОДЕ ХЭММИНГАЬ-'СЕСОЮЗНДЯ|^ДШ1НО-Г?ХЩ»;?еКДЯ^ИЗЯНОТЕНА' | 1971 |

|

SU310389A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И» | 1971 |

|

SU305585A1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ЧИСЕЛ в ЦИКЛИЧЕСКОМКОДЕ | 1971 |

|

SU306460A1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1971 |

|

SU306571A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ФУНКЦИЙ РАВНОЗНАЧНОСТИ | 1973 |

|

SU370726A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

-о 5

Авторы

Даты

1970-01-01—Публикация