Известно запоминающее устройство (ЗУ), содержащее числовые линейки из элементов памяти с неразрушающ,им считыванием, например двухотверстиых трансфлюксоров, прошитых по большому отверстию обмоткой установки в «I и обмоткой установки в «О и по малому отверстию - выходной обмоткой и обмоткой считывания, клапаны, управляющие входы которых подсоединены к кодовым шинам числа, а также кодовые шины и выходные шины.

Недостатками известного ЗУ являются большое потребление мощности, невысокая надежность и необходимость строгого отбора трансфлюксоров по однородности параметров.

Предложенное ЗУ оличается от известного тем, что в каждый элемент памяти введены накопительный конденсатор и два диода, обмотки установки в «1 всех трансфлюксоров каждой линейки соединены последовательно и подключены к кодовым шинам адреса, обмотки установки в «О трансфлюксоров одноименных разрядов всех числовых линеек одними концами подсоединены к выходным шинам устройства и к информационным входам клапанов, другими - через первые диоды к соответствующим накопительным конденсаторам. Каждый накопительный конденсатор подключен через второй диод к выходной обмотке соответствующего трансфлюксора,

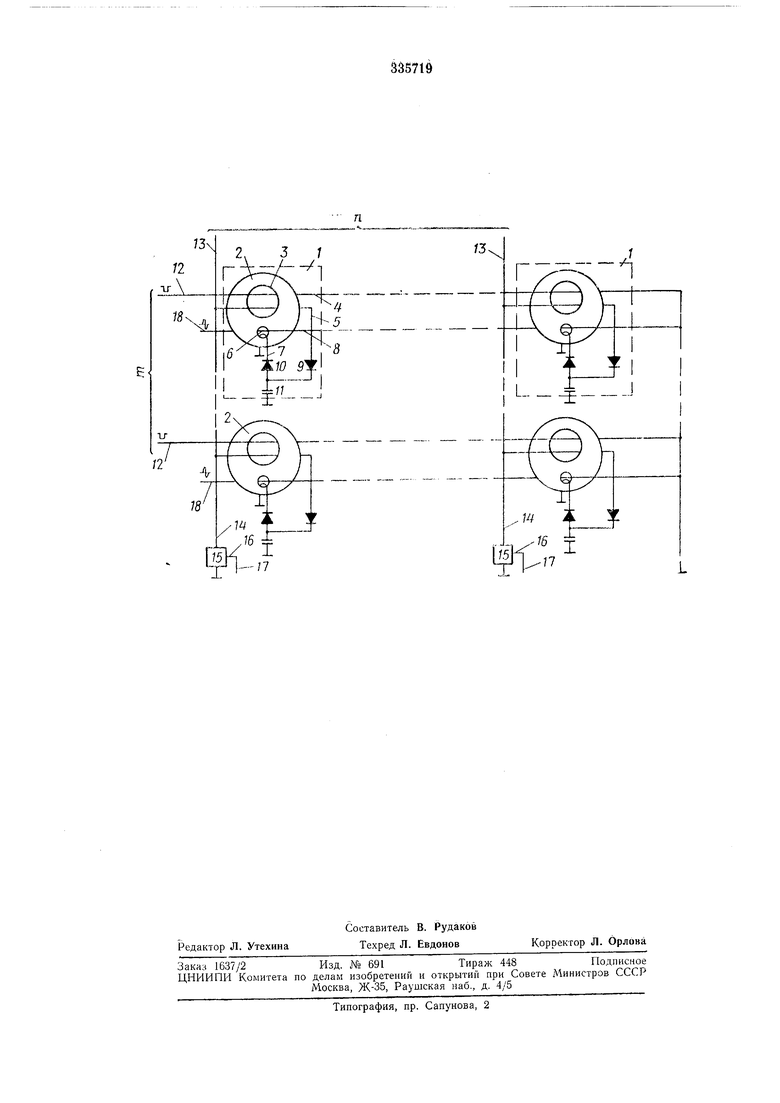

Принципиальная схема матрицы ЗУ на трансфлюксорах приведена на чертеже.

Матрица ЗУ состоит из элементов намят; /. Элементы, расположенные в одном горизонтальном ряду, составляют числовую линейку, а элементы, расположенные в одном столбце, служат для хранения одноименных разрядов запоминаемых чисел. Каждая числовая линейка содержит п элементов памяти (п - разрядов запоминаемых чисел). Матрица содержит т числовых линеек (т - запоминаемых чисел).

Элемент памяти состоит из двухотверстного трансфлюксора 2, прошитого по большому

отверстию 3 обмоткой 4 установки в «1 и обмоткой 5 установки в «О и по малому отверстию 6 - выходной обмоткой 7 и обмоткой 8 считывания, первого 9 и второго W диодов и накопительного конденсатора 11.

Обмотки 4 всех трансфлюксоров 2 каждой числовой линейки соединены последовательно и подключены к кодовым шинам 12 адреса. Обмотки 5 трансфлюксоров 2 одноименных разрядов всех числовых линеек одними концами подсоединены к выходным шинам 13 устройства и к информационным входам 14 клапанов 15, управляющие входы которых подключены к кодовым шннам 17 числа. Другими концами эти обмотки подключены через перным конденсаторам 11. Каждый конденсатор 11 подключен через второй диод 10 к выходной обмотке 7 соответствующего трансфлюксора 2. Обмотки считывания 8 трансфлюксоров 2 каждой числовой линейки соединены последовательно и подключены к адресным шинам 18 считывания.

Число витков установочных обмоток 4 и 5 выбираются соответственно из условия разблокировки (установки в «1) и блокировки (установки в «О) трансфлюксора 2. При прохождении двухиолярного сигнала считывания по обмотке считывания 8 с выходной обмотки 7 трансфлюксора 2, если он находится в состоянии «1, снимается напряжение на заряд конденсатора 11 через диод 10. Время заряда этого конденсатора при выбранных элементах схемы определяется мощностью считывающего сигнала и его частотой. Конденсатор 11 заряжается до амплитудного значения импульсов выходной обмотки 7, благодаря чему на конденсаторе // имеется отрицательный потенциал, который снимается через диод 9.

Запись числа в ЗУ производится следующим образом.

В числовую линейку, соответствующую выбранному адресу, подается отридательный импульс по кодовой шипе 12 адреса, который разблокирует все транофлюксоры данной числовой линейки (устанавливает все трансфлю,ксоры вЫбранной линейки в «1) и знакопеременный сигнал по адресной щине 18 считывания, благодаря которому заряжаются конденсаторы 11 данной линейки. Через определенный интервал, достаточный для полного заряда указанных конденсаторов 11, по кодовым шинам 17 числа, соответствующим нулевым значениям разрядов в записываемом числе, .подаются сигналы на открытие одноименных клапанов. Конденсаторы 11, соответствующие нулевым значениям в записываемом числе, разряжаются через указанные клаланы 75 w обмотки 5 трансфлюксоров 2 и устанавливают их Б «О. В результате в выбранной числовой линейке записывается необходимое число.

Считывание числа из ЗУ производится при подаче знакопеременного сигнала в адресную шину 18 считывания выбранной числовой линейки. В результате с выходных щин 13 устройства снимается иотенциальный код записанного числа на время подачи считывающего сигнала, иричем за «1 на выходе устройства принимается отрицательный потенциал заряженного конденсатора И разблокнрованного трансфлюксора 2.

Предмет изобретения

Запоминающее устройство, содержащее числовые линейки из элементов памяти с неразрущающим считыванием, например двухотверстных трансфлюксоров, прошитых по большому отверстию обмоткой установки в «1 и обмоткой установки в «О и по малому отверстию- выходной обмоткой и обмоткой считывання, клапаны, управляющие входы которых подсоединены к кодовым шинам числа, а также кодовые шины адреса и выходные П1Ины, отличающееся тем, что, с целью уменьшения потребляемой мощности и повышения надежности устройства, в каждый элемент памяти введены на.копительный конденсатор и два диода, обмотки установки в «1 всех трансфлюксоров каждой числовой линейки соединены последовательно и подключены к кодовым шинам адреса, обмотки установки в «О трансфлюксоров одноименных разрядов всех числовых лияеек одними концами подсоединены к выходным шинам устройства и к информационным входам клапанов, другими концами - через первые диоды к соответствующим накопительным конденсаторам, а каждый накопительный конденсатор подключен через второй диод к выходной обмотке соответствующего трансфлюксора.

| название | год | авторы | номер документа |

|---|---|---|---|

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| Запоминающее устройство | 1973 |

|

SU444239A1 |

| СТАТИЧЕСКИЙ ТРИГГЕР | 1973 |

|

SU363193A1 |

| ТРОИЧНЫЙ ЭЛЕМЕНТБс:'Со;о:7НАЛ [;--т^;ГГг-;-,-.,у;.':--^ч;др(1- .. u..5i .It^ . J.i>&;.'; ;«,,ldr1ii' | 1971 |

|

SU319074A1 |

| ТГХИИЧЕСКАЙЬИ&ЛИОТИА | 1970 |

|

SU271576A1 |

| МАГНИТНЫЙ ДЕШИФРАТОР | 1973 |

|

SU374726A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ЧИСЕЛ В КОДЕ ХЭММИНГАЬ-'СЕСОЮЗНДЯ|^ДШ1НО-Г?ХЩ»;?еКДЯ^ИЗЯНОТЕНА' | 1971 |

|

SU310389A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

| Преобразователь кода грея в двоичный код | 1977 |

|

SU661790A1 |

Даты

1972-01-01—Публикация