1

Изобретение может быть применено в автоматике и 1вычи1слительной техии-ке.

Известны устройства формирования функций равнозначности и нера ВНоз«ачности, выподненные на магнитных элементах.

В .предложенном устройстве для его упрощения, снижения Потребляемой Мощиости и повышения «адежяости применены двухотiBepicpHbie траЕсфлюксоры с обмотками блокировочными, разблОКировочньгми, выходивши и Считывания, койден-саторы и диоды.

Блокировоч,ные об-мотки всех трансфлюксоров соединены последовательно со-гласно и подсоединены ко входу установки в «О устРойства, обмотки считываиия всех трансфлюксоров соединены последовательно согласно и подсоединены ко входу считывающего генератора, разблокировочные обмотки первых двух траисфлкжсоров подсоединены ко входам исходных сигналов. Выходные обмотки этих двух трансфлюксоров соединены последовательно встречно и через диод подсоединены 1К накопительному конденсатору этой пары трансфлюксоров, -к выходу неравнозначности устроЙ1Ства и к разблокировочной обмотке третьего трансфлюксора, другой конец которой подсоединен через диод ко входу инвертирования. Выходная обмотка третьего трансфлюксора через диод подсоединена к

свое.му на-копительно-му конденсатору и к выходу равнозначности устройства.

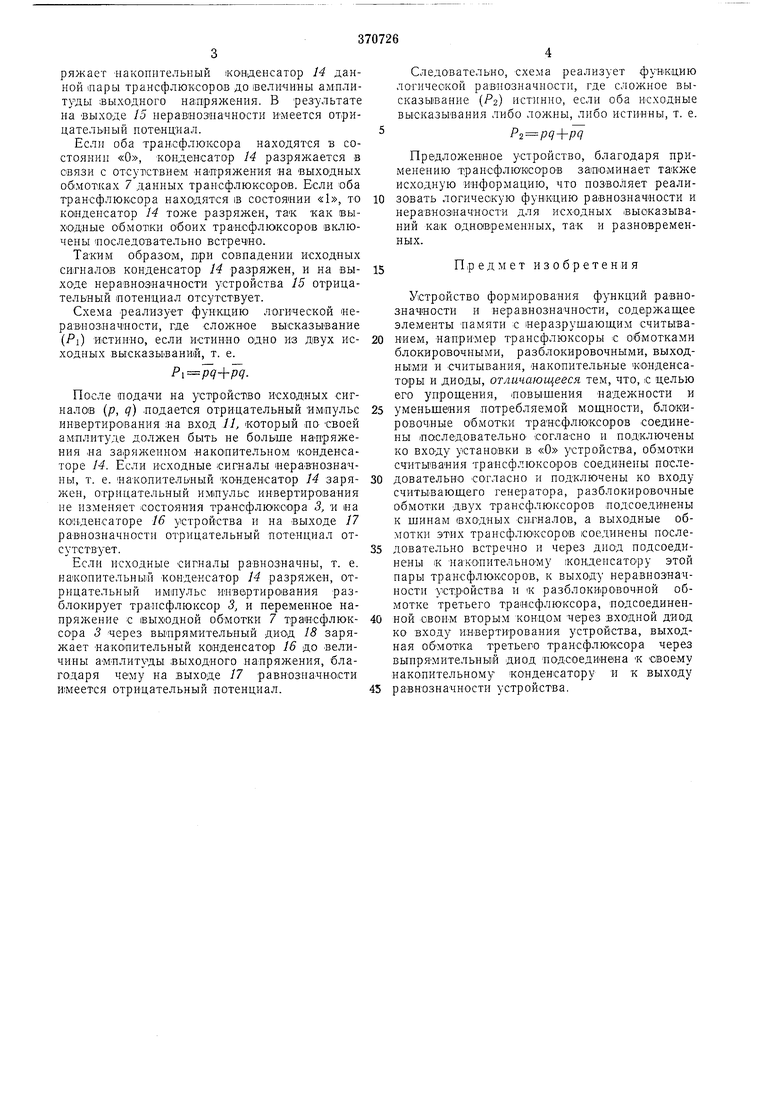

Принципиальная электрическая схема предложенного устройства формирования функций

равноЗНачности и неравнозначности приведена «а чертеже.

В схеме устройства использованы двухотверстные трансфлюксоры 1-3. Обмотки 4 разблокировки (установка в «1) и обмотки 5

блокировки (устано;вка в «О) каждого тра«сфлюксора проходят через большое отверстие, обмотки б считывания и выходные обмотки 7 - через малое отверстие трансфлюксора. Разблокировка и блокировка трансфлюксоров

производятся импульсами отрицательной полярности, подаваемыми на входы 8-11 устройства. Информация считывается знако переменным сигналом, подаваемым непрерывно на вход 12 устройства от считывающего генератора.

До подачи исходных отрицательных сигналов (р, д) по входам 8, 9 устройство )станавливают в состояние «О подачей отрицательного сигнала на вход 10, (что блокирует все

трансфлюксоры).

Если один из двух трансфлюксоров 1,2s результате поступления исходных сигналов находится в состоянии «1, переменное напряжение с выходной обмотки 7 этого трансфлюксора через выпрямительный диод 13 заряжает накопительный конденсатор 14 данной тары трансфлюксоров до величины амплитуды выходного нааряжеиия. В результате на выходе 15 неравнозиачности и-меется отрицательный потенциал. Если оба тран;сфлюксора находятся в состоянии «О, конденсатор 14 разряжается в связи с отсутствием Напряжения на выходных обмотках 7 данных трансфлюксоров. Бели оба трансфлюксора находятся IB состоящий «1, то конденсатор 14 тоже разряжен, так как овыхадные обмотки обоих тра«сфлюксоров включены последовательно встречно. Таким образом, .ври совпадении и-сходных сигналов конденсатор 14 разряжен, и на выходе неравнозначности устройства 15 отрицательный потенциал отсутствует. Схема реализует функцию логической «еравнозначности, где сложное высказывание (PI) истинно, если истинно одно из двух исходных высказываний, т. е. . После еодачи на устройство исходных сигналов (р, q) подается отрицательный импульс инвертирования :на вход 11, который по своей амплитуде должен быть не болыще напряжения на заряженнОМ накопительном конденсаторе 14. Если исходные сигналы неравнозначны, т. е. накопительный конденсатор 14 заряжен, отрицательный имтульс инвертир01вания не изменяет состояния трансфлю ксора 3, и на конденсаторе 16 устройства и на выходе 17 равнозначности отрицательный потенциал отсутствует. Если исходные сигналы равнозначны, т. е. на копительный конденсатор 14 разряжен, отрицательный им1пульс инвертирования разблокирует трапсфлюксор 3, и переменное напряжение с выходной обмотки 7 трансфлюксора 3 через выпрямительный диод 18 заряжает накопительный конденсатор 16 до величины амплитуды выходного напряжения, благодаря чему на выходе 17 равнозначности И меется отрицательный потенциал. Следовательно, схема реализует фувкцию лоГичеокой раВПозначно.сти, где сложное высказывание (Pz) истинно, если оба исходные высказывания либо ложны, либо истинны, т. е. P2 pq+pq Предложенное устройство, благодаря применению трансфлюксоров запоминает та1кже исходную информацию, что позволяет реализовать логическую функцию равнознач«0|Сти и неравнозиачности для исходных высказываний как одновременных, та-к и разновременных. Предмет изобретения Устройство формирования функций равнозначности и неравнозначности, содержащее элементы памяти с неразрушающим считыванием, например трансфлюксоры с о-бмотками блокировочными, разблокировочными, выходными в считывания, накопительные конденсаторы и дноды, отличающееся тем, что, с целью его упрощения, повыщения надежности и уменьшения потребляемой мощности, блокировачные обмотки трансфлюксоров соединены последовательно согласно и подключены ко входу установки в «О устройства, обмотки считывания трансфлюксоров соединены последовательно согласно и подключены ко входу считывающего генератора, разблокировочные обмотки двух трансфлюксоров подсоединены к щинам входных сигналов, а выходные обмотки этих трансфлюксоров соединены последовательно встречно и через диод подсоединены 1К накопительному 1конденсатору этой пары трансфлю.ксоров, к выходу неравнозначности устройства и 1К разблокировочной обмотке третьего трансфлюксора, подсоединенной своим вторым концом через входной диод ко входу инвертирования устройства, выходная об мотка третьего трансфлюксора через выпрямительный диод подсоединена к своему накопительному конденсатору и к выходу равнозначности устройства.

О

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ЧИСЕЛ в ЦИКЛИЧЕСКОМКОДЕ | 1971 |

|

SU306460A1 |

| МАГНИТНЫЙ ДЕШИФРАТОР | 1973 |

|

SU374726A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU350157A1 |

| ТРОИЧНЫЙ ЭЛЕМЕНТБс:'Со;о:7НАЛ [;--т^;ГГг-;-,-.,у;.':--^ч;др(1- .. u..5i .It^ . J.i>&;.'; ;«,,ldr1ii' | 1971 |

|

SU319074A1 |

| ТГХИИЧЕСКАЙЬИ&ЛИОТИА | 1970 |

|

SU271576A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И» | 1971 |

|

SU305585A1 |

| Преобразователь кода грэя в двоичныйКОд и ОбРАТНО | 1979 |

|

SU843225A1 |

| ВЫЧИТАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ | 1970 |

|

SU281006A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| СТАТИЧЕСКИЙ ТРИГГЕР | 1973 |

|

SU363193A1 |

Авторы

Даты

1973-01-01—Публикация