Описываемая схема ячейки намяти на основе металл - окисел - полупроводник (МОП-транзистор) может быть использована для построения оперативных запоминающих устройств, характеризующихся малыми габаритами и низкой рассеиваемой мощностью.

Известны ячейки памяти, содержащие информационные транзисторы, выполненные на основе металл - окисел - полупроводник, конденсаторы, подключенные к транзисторам, формирователи восстановления и разрядные линии «единицы и «нуля.

В описываемой ячейке памяти осуществлено дальнейщее уменьшение потребляемой энергии и увеличена надежность ее работы.

Это достигается тем, что формирователь восстановления выполнен в виде генератора с медленно нарастающим и спадающим напряжением и подсоединен через конденсатор и транзистор, выполненный на основе металл - окисел - полупроводник, к информационным транзисторам, последовательно к которым подключены буферные транзисторы, выполненные на основе металл - окисел - полупроводннк.

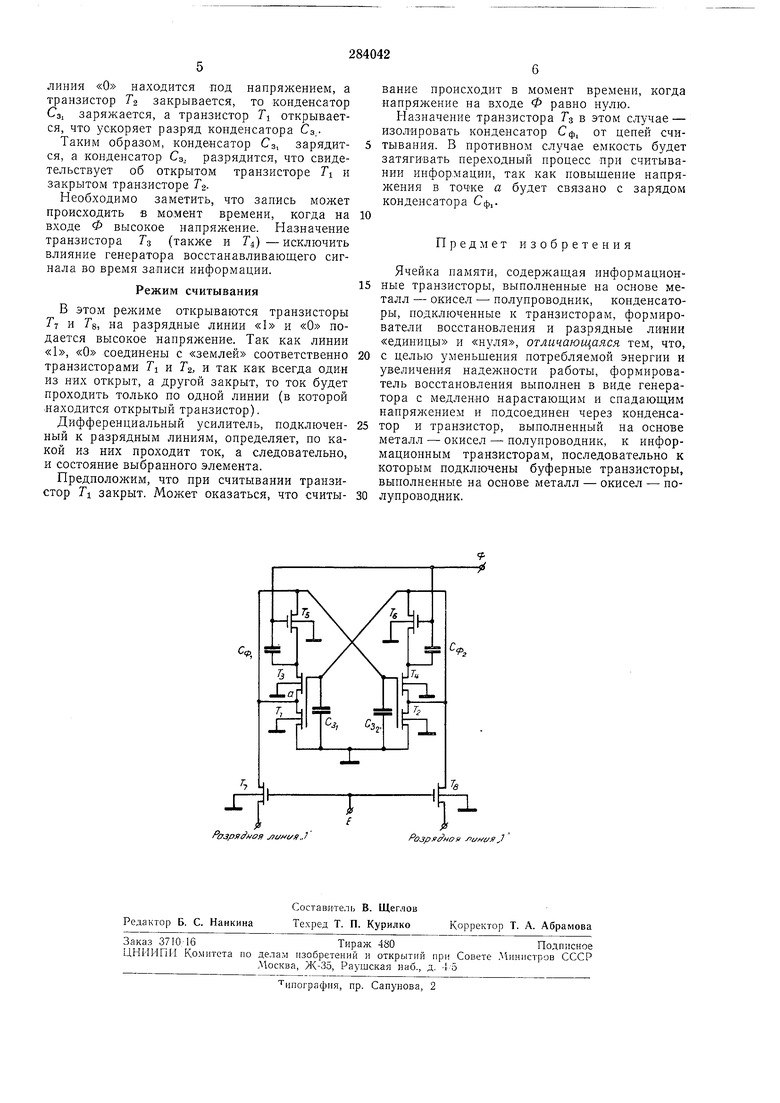

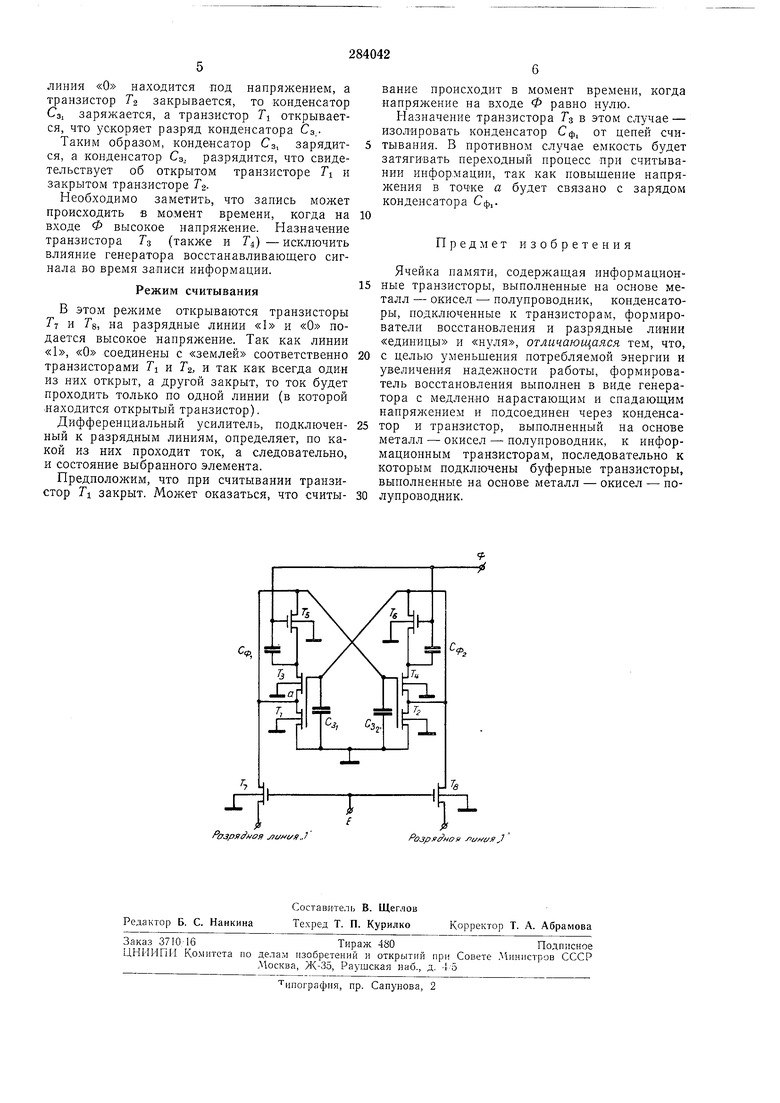

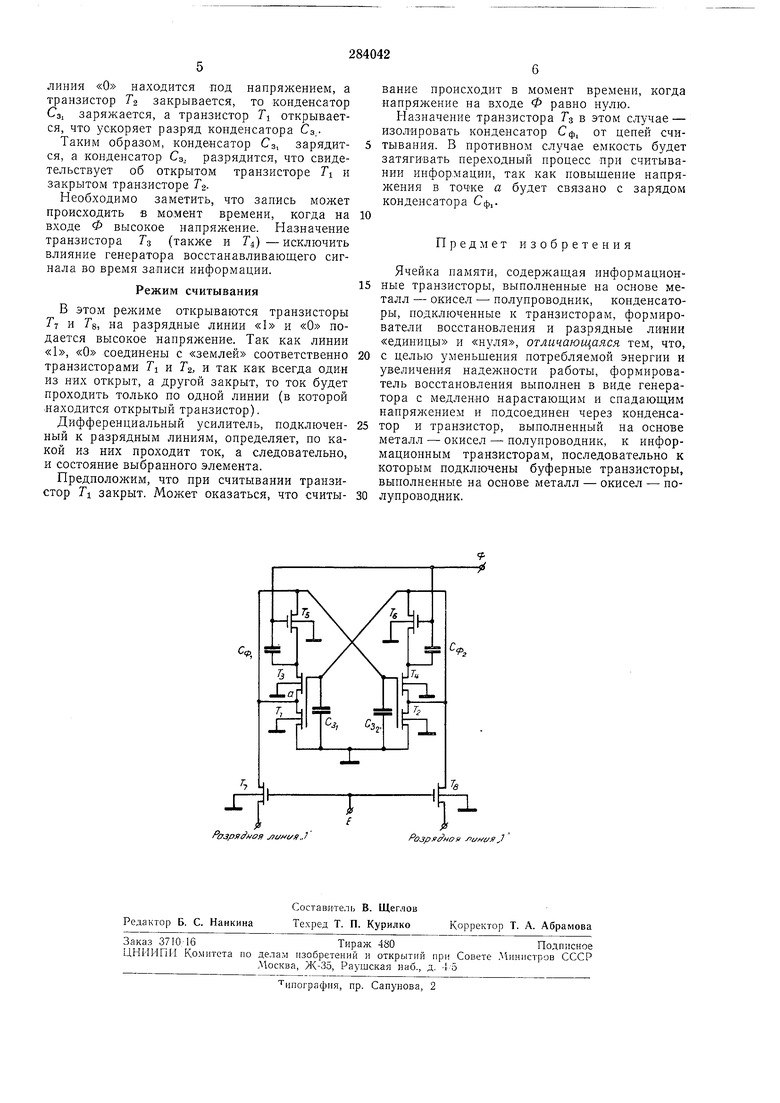

На чертеже изображена схема описываемой ячейки, где TI-TS - МОП-транзисторы; С з, , Сзг, Сф„ Сф., - конденсаторы; Ф, Е - источники (входы); разрядная линия «1, разрядная линия «О - шины управления.

2 Режим храисчшя информации

Транзисторы T и TS, обеспечивающие связь с цепями записи и считывания, закрыты; на входе Ф генератора - медленно нарастающее и медленно спадающее напряжение.

Предпололшм для определенности, что информационный транзистор TI закрыт, а информационный транзистор TZ открыт.

В этом случае конденсатор Сз,, зарян ен до необходимого напряжения, а конденсатор Сз1 разряжен. Когда транзистор Т закрыт, конденсатор Сз медленно разрялсается током обратно смещенных р-п-переходов, образованных истоковыми областями транзисторов Гз, T и стоковыми областями транзисторов TI и Гд.

Периодическое открывание транзистора TS, создает цепь подзаряда конденсатора Сз, а именно: вход Ф, Сф,, Гз, Сз,. Одновременно открывается и транзистор Тц, однако это не приводит к заряду конденсатора Сз,, так как конденсатор оказывается зашунтированным открытым транзистором Т. Таким образом, периодически медленно изменяющееся напряжение на входе Ф дает возможность поддерживать заряд конденсатора Сз, на необходимом уровне, а так как отсутствует делитель сопротивлений, подключенный к источнику 1питания, то и отсутствует связанное с ним рассеяние энергии. В известных вариантах минимальная длительность им пульса определяется временем восстановления напряжения -на запоминающей ем1кости до первоначального уровня. Время заряда емкости до устанавливающегося значения олределяется «ак ,2т, где т - постоянная С-цени. Следовательно, минимальная длительность восстанавливающего имнульса равна „ 2,,(1) где R - сопротивление транзистора Tз(T), а Сз -запоминающая емкость С )Вычислим рассеиваемую энергию за 1 период в возникающем делителе сопротивлений тра«зисторов TI, Тз (Tz, Ti). Так как сопротивление транзистора Rt, RT, (Rr Rr,), то основная часть энергии рассеивается буферным транзистором Тз (Т), поэтому: ,-i-dt о Подставляя вместо „ выражение из формулы (1), получим: Я 2,2Сз-;Уо,(2) где UD - напряжение источника питания Е. Предположим, что период следования восстанавливающих сигналов равен периоду еледования восстанавливающих импульсов.Данвое предположение основано на том, что в обоих случаях частота подзаряда определяется разрядом конденсатора Сэ, (Сз,) то.ком обратно смещенных /э-л-переходов. Предположим далее, что сигнал на входе Ф нарастает и спадает экспоненциально и время нарастания и спада равно 7/2. Тогда постоянная нарастания и спада определится как . 2,2 Если на вход / С-цепи подавать экспоненциально нарастающее (спадающее) напряжеLJ,riClbliJllV liCtL/Cl -I CilV..4 iw-ll t,i., i. n 1.1 J i. л i.ние, TO энергия, рассеиваемая на сопротивлеНИИ R при заряде (разряде) емкости, определится следующим образом: где: t/o - максимальное напряжение источника; п - соотношение постоянных нарастающего сигнала и / С-цепи. В этом нетрудно убедиться, записав энергию рассеяния цепи следующим образом: где VR U-U(c), UR -напряжение на сопротивлении; U - напряжение на входе С-цепи; 1}(с) -напряжение на емкости. Напряжение U(c) как функцию времени найдем, рещая линейное дифференциальное уравнение заряда dU(C) и -и (С) dt R С начальным условием L (. (6а) Напряжение на входе / С-цепи меняется экспоненциально, т. е. Применяя формулу для общего решения линейного уравнения (2), получим: и(С) и,Х t. t р к-с Нодставив выражение формулы (7) в (5) я проинтегрировав, получим формулу для энергии, рассеиваемой сопротивлением R при заряде конденсатора С. Для предлагаемой, ячейки памяти, следовательно: 2 п + 1 где Сф - одна из емкостей Сф, или Сф,. Для работы ячейки памяти достаточно чтобы Сф л;(3-4)Сз, а поэтому сравнивая выражения (2) и (4) видим, что мощность,. рассеиваемая новым вариантом ячейки, в; rt-f-1 раз меньще, чем в известной схеме. Так как период следования восстанавливающих сигналов определяется разрядом одной из запоминающих емкостей обратными токами /5-/г-переходов, а постоянная RCцепи - зарядом одного из конденсаторов (Сф, или С ф,) через два последовательно соединенных и открытых транзистора Т и Гз (или Г2 и Ti), то величина п обычно составляет сотни единиц и более. ЕСли в известных схемах ячейка памяти рассеивает около 30 мквт, то реализация ячейки памяти по описанному принципу позволит уменьшить рассеиваемую мощность на два порядка и более, т. е. позволит перейти по величине рассенваемоп мощности в нано1ваттный диапазон. Режим записи информации Предположим, что ячейка хранила информацию, согласно которой транзистор TZ был открыт, а TI - закрыт. Необходимо изменить состояние ячейки на противоположное, т. е., транзистор TI должен открываться, а закрываться транзистор Гг. Для этого на разрядную линию «О подается напряжение, а разрядная линия «1 соединяется с «землей. Одновременно открываются транзисторы T и Т. Конденсатор С,,. через транзистор T соединен с землей и, следовательно, разряжается. Умепьщение напряжения на конденсаторе Сз, приводит к за

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU326641A1 |

| УСТРОЙСТВО для ЗАРЯДА АККУМУЛЯТОРНОЙ БАТАРЕИ | 1973 |

|

SU369757A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО ИЗМЕНЕНИЯ РЕЖИМА | 1969 |

|

SU257911A1 |

| УСТРОЙСТВО для ФОРМИРОВАНИЯ БИПОЛЯРНЫХ ИМПУЛЬСОВ УПРАВЛЕНИЯ | 1972 |

|

SU343349A1 |

| УСТРОЙСТВО СВЕТОВОЙ СИГНАЛИЗАЦИЙ | 1972 |

|

SU331414A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ СТАБИЛИЗАЦИИ | 1970 |

|

SU284099A1 |

| МНОГОРАЗРЯДНЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК ИМПУЛЬСОВ | 1968 |

|

SU206904A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ДЛИТЕЛЬНОСТЬ ИМПУЛЬСОВ | 1970 |

|

SU271918A1 |

| Преобразователь постоянного напряжения | 1986 |

|

SU1410233A1 |

| Линейный импульсный модулятор | 1976 |

|

SU769727A1 |

Даты

1970-01-01—Публикация