Изобретение относится к вычислительной технике.

Известны ячейки памяти на МОП-транзисторах, содержащие запоминающие и нагрузочные транзисторы, между затвором и стоком каждого нагрузочного транзистора включен конденсатор.

Недостатками известной схемы являются относительно большая величина рассеиваемой мощности и большое время обращения к ячейке.

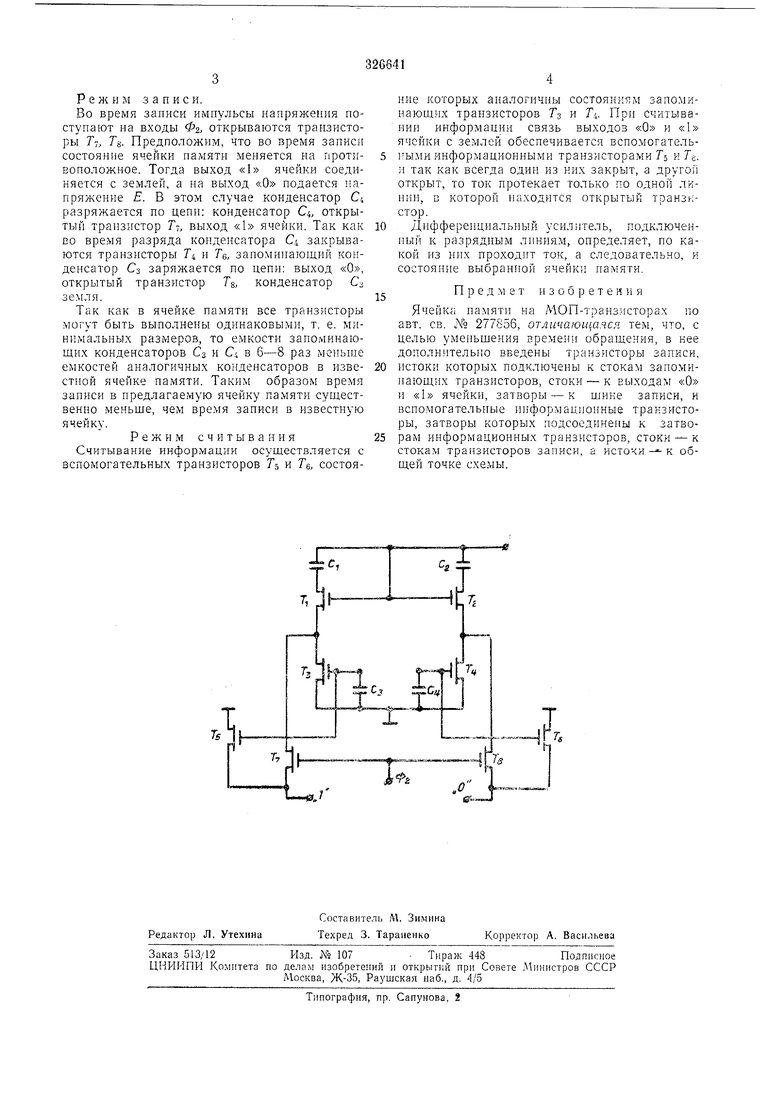

Предлагаемая ячейка памяти отличается тем, что в нее дополнительно введены транзисторы заииси, истоки которы.х подключены к стокам запоминающих транзисторов, стоки - к выходам «О «1 ячейки, затворы - к шине записи, и вспомогательные информационные транзисторы, затворы которых нодсоединены к затворам информационных Tjjaiiзисторов, стоки - к стокам транзисторов заппси, а истоки - к общей точке схемы.

Это позволяет увеличить быстродействие устройства и уменьшить иотребляемую мощность.

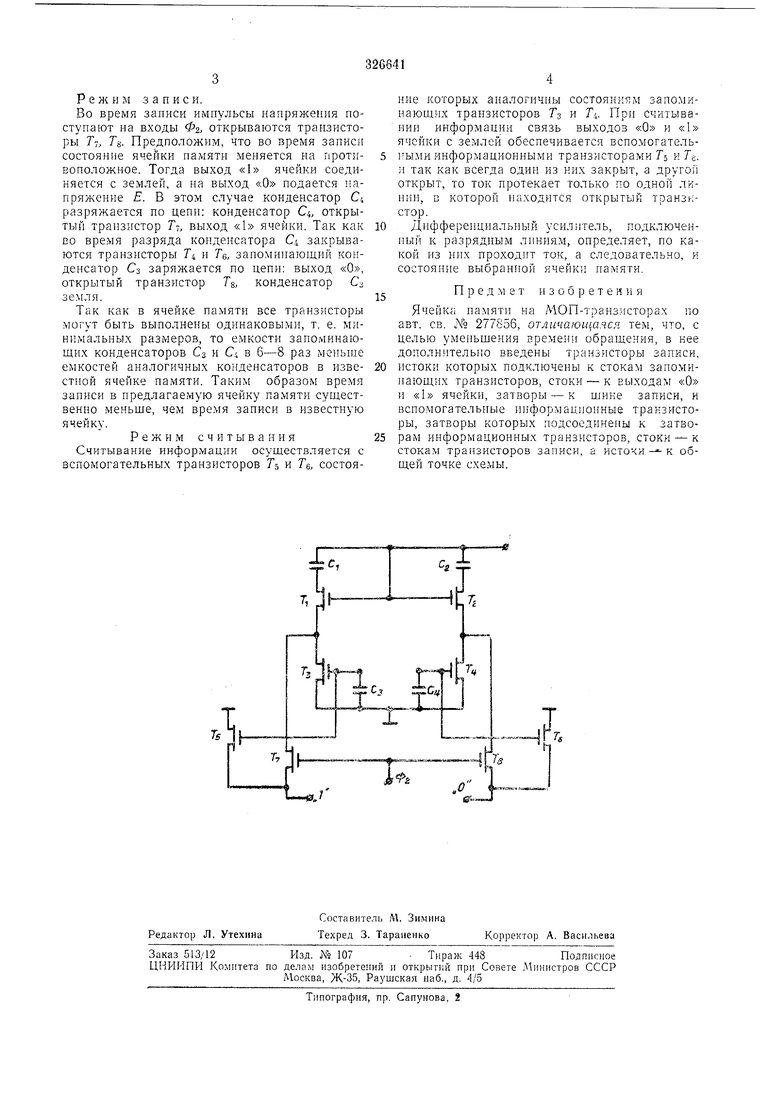

Схема предлагаемой ячейки показана на чертеже.

Гб, транзистооы записи Тч, Т& и конденсаторы Ci-CV

Ячейка памяти работает в режимах хранения, записи и считывания.

Р еж и м хранения.

Транзисторы Г:-Гз закрыты, на вход Ф подается периодически медленно изменяющееся иапряжен.е. Предположим, что транзистор Гз закрыт, а транзистор Т:, открыт. В этом случае конденсатор Сз разряжгн, а конденсатор C.i заряжен. Когда транзистор Гз закрыт, конденсатор d медлепно разряжается током обратно смещеп :ых р переходов, образованных нстсковыми областями транзисторов Т. Т-; и стоковой областью транзистора TS, с подложкой.

Периодическое открывание транзистора 7i создает цепь иод аряда конденсатора Ci,, вход 01, конденсатор Ci транзистор Гь конденсатор С.; земля. Одновременно открывается транзистор TZ. Однако конденсатор Сз зарядиться не .может, так как он защунтирован открытым транзистором Ti.

Таким образом, периодическ медленно из.мепяющееся напряжение на входе Ф, дает возможность поддерживать заряд конденсатора С4 па необходимом уровне, а так как отсутствует делитель сопротивлений, подключенный к источнику питания, то отсутствует связанное с ним рассеяние энергии.

Режим 3 а п и с и.

Во время записи импульсы напряжения поступают на входы Ф, открываются транзисторы TI, TS. Предположим, что во время записи состояние ячейки памяти меняется на претиЕоположное. Тогда выход «1 ячейки соединяется с землей, а на выход «О подается папряжение Е. В этом случае конденсатор С/, разряжается по цепи: конденсатор Ci,, открытый транзистор Гт, выход «1 ячейки. Так как во время разряда конденсатора C.i закрываются транзисторы Ti и Тц, запоминающий конденсатор Сз заряжается по цепи: выход «О, открытый транзистор TS, конденсатор Сз земля.

Так как в ячейке памяти все транзисторы могут быть выполнены одинаковыми, т. е. минимальных размеров, то емкости запоминающих конденсаторов Сз и C в 6-8 раз меньще емкостей аналогичных конденсаторов в известной ячейке памяти. Таким образом время записи в иредлагаемую ячейку памяти существенно меньще, чем время записи в известную ячейку.

Режим считывания

Считывание информации осуществляется с вспомогательных транзисторов Т- и TS, состояние которых аналогичны состояниям запоминающих транзисторов Тз и П. При считывании информации связь выходов «О и «1 ячейки с землей обеспечивается вспомогательными информационными транзисторами Tj и 7е. и так как всегда один из них закрыт, а другой открыт, то ток протекает только по одной линии, в которой находится открытый транзистор.

Дифференциальный усилитель, подключенный к разрядным линиям, определяет, по какой из них проходит ток, а следовательно, и состояние выбранной ячейки памяти.

П р е д :vi е т и з о б р е т е и ii я

Ячейка памяти на МОП-транзисторах по авт. св. ЛЬ 277856, отличающаяся тем, что, с целью уменьщения времени обращения, в нее дополнительно введены транзисторы записи, истоки которых подключены к стокам запоминающих транзисторов, стоки - к выходам «О и «1 ячейки, затворы - к щине записи, и вспомогательные И1;формацнонные транзисторы, затворы которых подсоединены к затворам информационных транзисторов, стоки - к стокам транзисторов записи, а истоки - к общей точке схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 1970 |

|

SU284042A1 |

| СПОСОБ ЗАПИСИ ДАННЫХ ПРИ ТЕСТИРОВАНИИ УСТРОЙСТВА ПАМЯТИ И УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ПАМЯТИ | 1990 |

|

RU2084972C1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| ИНТЕГРАЛЬНАЯ МИКРОСХЕМА РАДИОЧАСТОТНОГО ИДЕНТИФИКАТОРА | 2011 |

|

RU2465645C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Способ сравнения данных в ячейке ассоциативного запоминающего устройства и модуль сравнения данных в ячейке ассоциативного запоминающего устройства | 2018 |

|

RU2680870C1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

Даты

1972-01-01—Публикация