Предложенное устройство относится к вычислительной технике и автоматике.

Пороговые суммирующие устройства, содержащие п блоков, каждый из которых состоит из 2п независимых источников тока, управляемых 2п переключающимися диодами, и туннельного диода, известны. К недостаткам известных устройств относится их малое быстродействие.

Предложенное пороговое суммирующее устройство отличается от известных тем, что к выходу туннельного диода каждого блока через проводящие диоды подключены инвертор тока, выполненный на туннельном диоде и резисторах, и транзистор с общей базой, параллельно базово-эмиттериому переходу которого включен другой туннельный диод, причем к эмиттеру транзистора лодключены через проводящие диоды два источника тока, управляемые диодами, и выход схемы инвертора тока предыдущего разряда.

Это повышает быстродействие при суммировании «-разрядных чисел за один такт питающего напряжения.

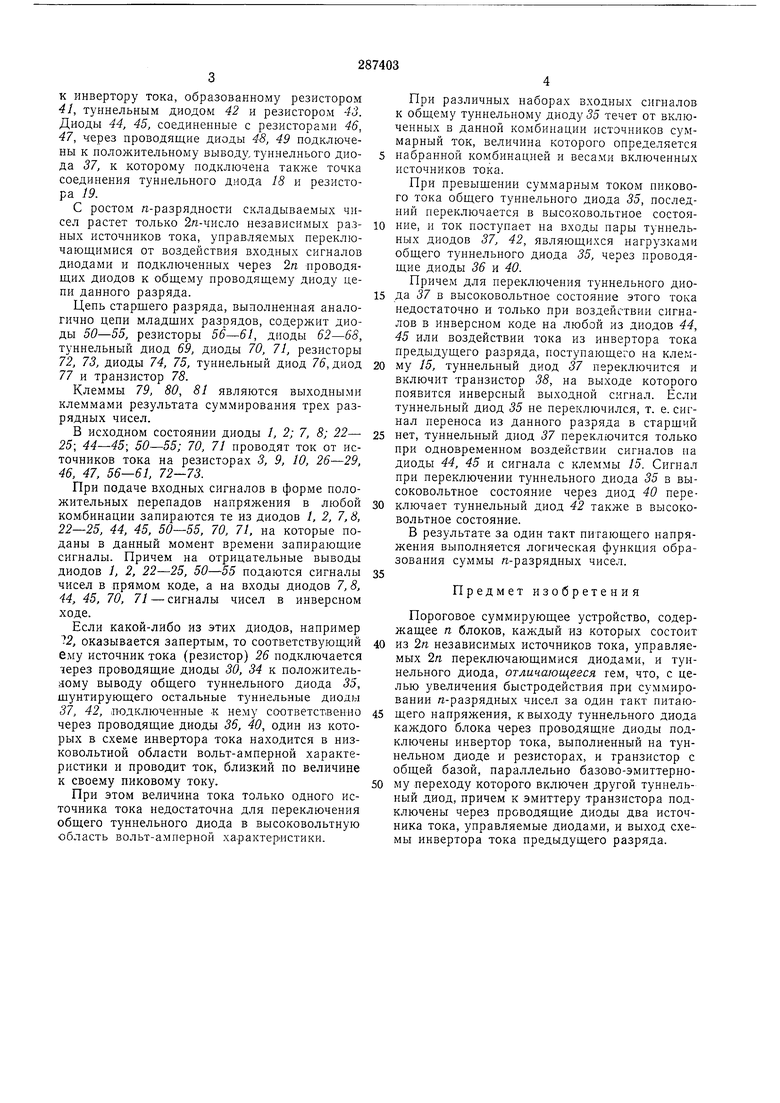

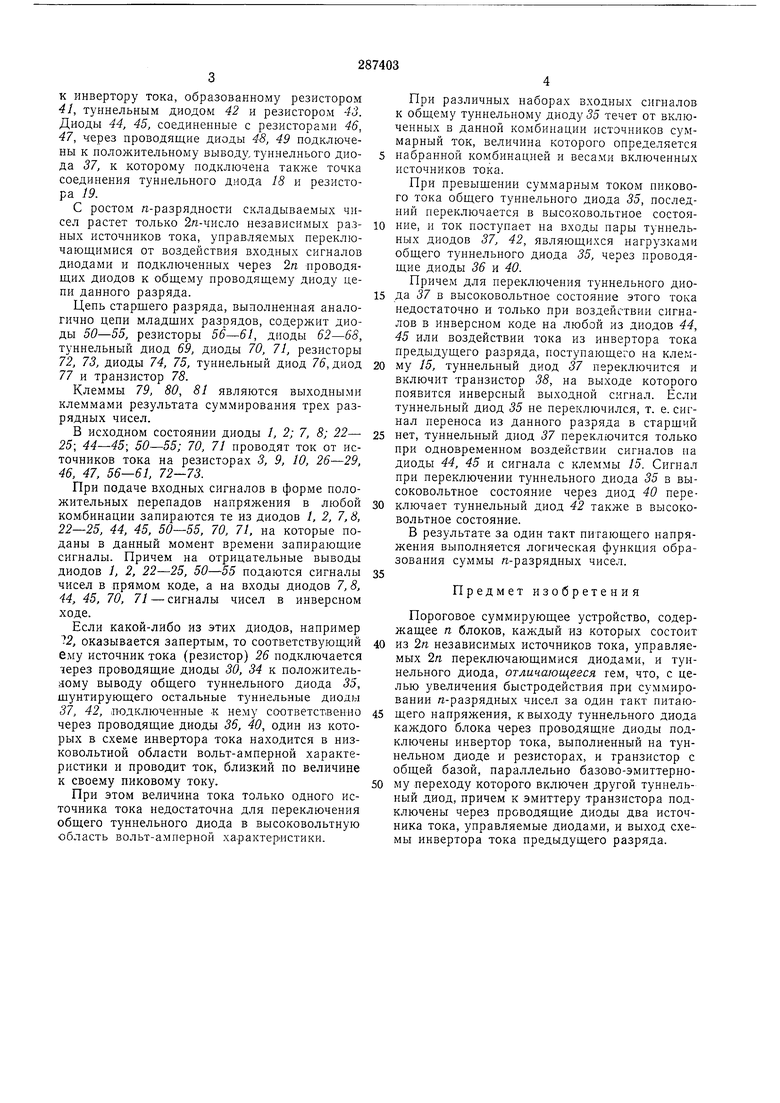

Принципиальная схема порогового суммирующего устройства приведена на чертеже.

Диоды 1, 2 положительными выводами подключены к резистору 5 и к положительному выводу диода 4, подключенного через проводящий диод 5 к положительному выводу туннельного диода 6. Диоды 7, 8 положительными выводамн подключены к резисторам 9, 10 и к положительиым выводам диодов 11, 12, отринательные выводы которых подключены к положительиому выводу туннельного диода 13. К положительному выводу туннельного днода 13 подключены также отрицательный вывод диода 14 и выход клеммы 15. Отрицательный вывод проводящего диода 16 подсоединен к

инвертору тока, образованному резистором 17, туннельным диодом 18 и резистором 19.

Положительный вывод туннельного диода 13 подключен к эмиттеру транзистора 20, с коллекторной нагрузкой - резистором 21. Резисторы 3, 9, 10 другими концами подключены к общей шине источника питания с положительной полярностью.

Аналогично, в цепи образования суммы старшего разряда положительные выводы диодов

22-25 подсоединены соответственно к резисторам 26-29 и к положительным выводам диодов 30-33, которые отрицательными выводами иодключены через проводящий диод.к положительному выводу туннельного диода 35. Положительный вывод туннельного диода 55 подсоединен через проводящий диод 36 к положительному выводу туннельного диода 37, соединенному с эмиттером транзистора 38, имеющего своей нагрузкой резистор 39, и

к инвертору тока, образованному резистором 41, туннельным диодом 42 и резистором 43. Диоды 44, 45, соединенные с резисторами 46, 47, через проводящие диоды 48, 49 подключены к положительному выводу, туннелнього диода 37, к которому подключена также точка соединения туннельного диода 18 и резистора 19.

С ростом п-разрядности складываемых чисел растет только 2я-число независимых разных источников тока, управляемых переключающимися от воздействия входных сигналов диодами и подключенных через 2п проводящих диодов к общему проводящему диоду цепи данного разряда.

Цепь старшего разряда, выполненная аналогично цепи младщих разрядов, содержит диоды 50-55, резисторы 56-61, диоды 62-68, туннельный диод 69, диоды 70, 71, резисторы 72, 73, диоды 74, 75, туннельный диод 76, диод 77 и транзистор 78.

Клеммы 79, ВО, 81 являются выходными клеммами результата суммирования трех разрядных чисел.

В исходном состоянии диоды /, 2; 7, 8; 22- 25; 44-45; 50-55; 70, 71 проводят ток от источников тока на резисторах 3, 9, 10, 26-29, 46, 47, 56-61, 72-73.

При подаче входных сигналов в форме положительных перепадов напряжения в любой комбинации запираются те из диодов 1, 2, 7,8, 22-25, 44, 45, 50-55, 70, 71, на которые поданы в данный момент времени запирающие сигналы. Причем на отрицательные выводы диодов 1, 2, 22-25, 50-55 подаются сигналы чисел в прямом коде, а на входы диодов 7, 8, 44, 45, 70, 71 - сигналы чисел в инверсном ходе.

Если какой-либо из этих диодов, например 2, оказывается запертым, то соответствующий ему источник тока (резистор) 26 подключается через проводящие диоды 30, 34 к положительному выводу общего туннельного диода 35, щунтирующего остальные туннельные диоды 37, 42, подключенные к нему соответственно через проводящие диоды 36, 40, один из которых в схеме инвертора тока находится в низковольтной области вольт-амперной характеристики и проводит ток, близкий по величине к своему пиковому току.

При этом величина тока только одного источника тока недостаточна для переключения общего туннельного диода в высоковольтную область вольт-амперной характеристики.

При различных наборах входных сигналов к общему туннельному диоду 55 течет от включенных в данной комбинации источников суммарный ток, величина которого определяется

набранной комбинацией и весами включенных источников тока.

При превыщении суммарным током пикового тока общего туннельного диода 35, последпий переключается в высоковольтное состояние, и ток поступает на входы пары туннельных диодов 37, 42, являющихся нагрузками общего туннельного диода 35, через проводящие диоды 36 и 40.

Причем для переключения туннельного диода 37 в высоковольтное состояние этого тока недостаточно и только при воздействии сигналов в инверсном коде на любой из диодов 44, 45 или воздействии тока из инвертора тока предыдущего разряда, поступающего на клемму 15, туннельный диод 37 переключится и включит транзистор 38, на выходе которого появится инверсный выходной сигнал. Если туннельный диод 35 не переключился, т. е. сигнал переноса из данного разряда в старший

нет, туннельный диод 37 переключится только при одновременном воздействии сигналов па диоды 44, 45 и сигнала с клеммы 15. Сигнал при переключении туннельного диода 35 в высоковольтное состояние через диод 40 переключает туннельный диод 42 также в высоковольтное состояние.

В результате за один такт питающего напряжения выполняется логическая функция образования суммы п-разрядных чисел.

Предмет изобретения

Пороговое суммирующее устройство, содержащее п блоков, каждый из которых состоит

из 2rt независимых источников тока, управляемых 2/1 переключающимися диодами, и туннельного диода, отличающееся тем, что, с целью увеличения быстродействия при суммировании «-разрядных чисел за один такт питающего напряжения, к выходу туннельного диода каждого блока через проводящие диоды подключены инвертор тока, выполненный на туннельном диоде и резисторах, и транзистор с общей базой, параллельно базово-эмиттерному переходу которого включен другой туннельный диод, причем к эмиттеру транзистора подключены через проводящие диоды два источника тока, управляемые диодами, и выход схемы инвертора тока предыдущего разряда.

етгаг;;

f

5

57

о-к

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1970 |

|

SU269201A1 |

| ПОРОГОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU399823A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Устройство для управления высоковольтным силовым транзистором | 1991 |

|

SU1835118A3 |

| Устройство подсвета луча электронно-лучевой трубки | 1981 |

|

SU1002971A2 |

| Способ восстановления слабосульфатированной аккумуляторной батареи и система для его осуществления | 1988 |

|

SU1727179A1 |

| СПОСОБ УПРАВЛЕНИЯ ПРОЦЕССОМ СВАРКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 2003 |

|

RU2239526C1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1444921A1 |

Даты

1970-01-01—Публикация