1

Изобретение относится к области автоматики и вычислительной техники.

Известны пороговые логические устройства, содержащие суммирующую пятивходовую схему, выполненную на входных и промежуточных диодах, аноды входных и промежуточных диодов соединены соответственно и подключены через резисторы к одному из источников питания, а катоды промежуточных диодов соединены с выходом суммирующей схемы, который подключен через последовательную диодно-резйстпвную цепь соответственно ко входам трех дискриминаторов.

Предложенное устройство отличается от известных тем, что в него введены два выходных усилителя, выполненных на транзисторах Шоттки с заземленным эмиттером, база каждого из которых присоединена соответственно к выходу первого и второго дискриминатора, а их входы соединены через дополнительные диоды, включенные в обратном направлении, с выходом третьего дискриминатора. Выходы дискриминаторов и коллекторы выходных усилителей через соответствующие резисторы соединены с другим источником питания. Каждый дискриминатор выполнен на транзисторе с заземленным эмиттером и туннельном диоде, включенном параллельно базово-эмиттерному переходу транзистора, база и коллектор которого соединены соответственно со входом и выходом дискриминатора.

Это позволяет увеличить быстродействие устройства.

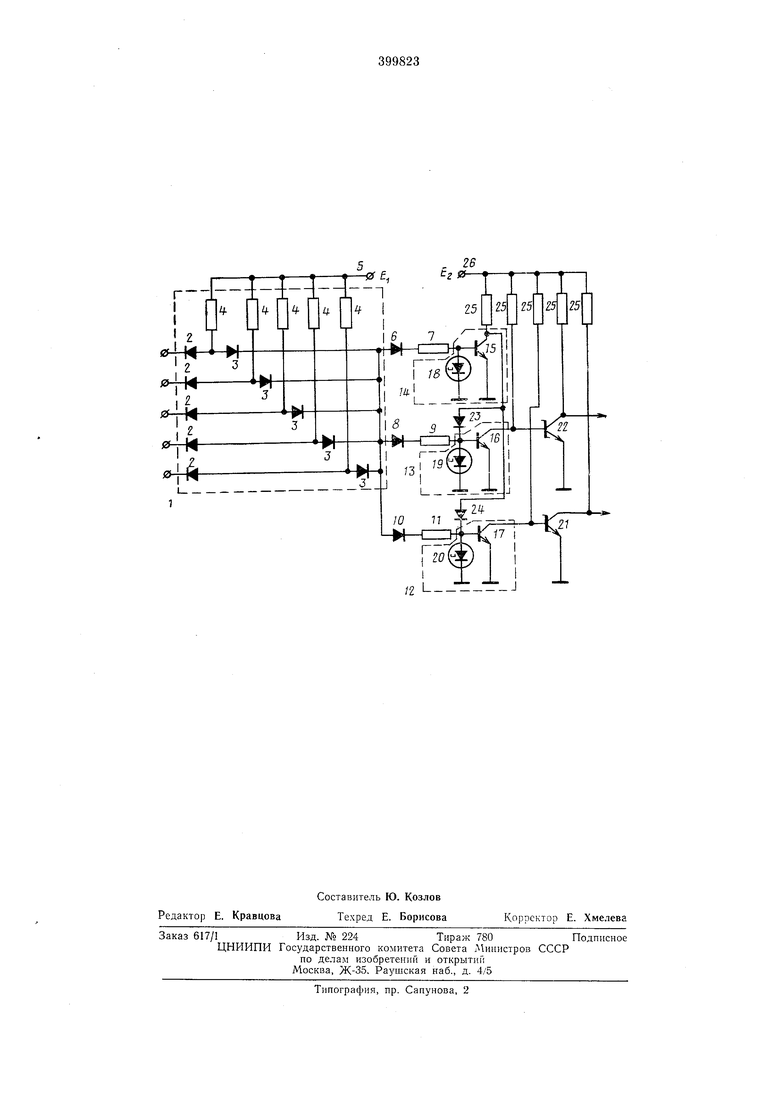

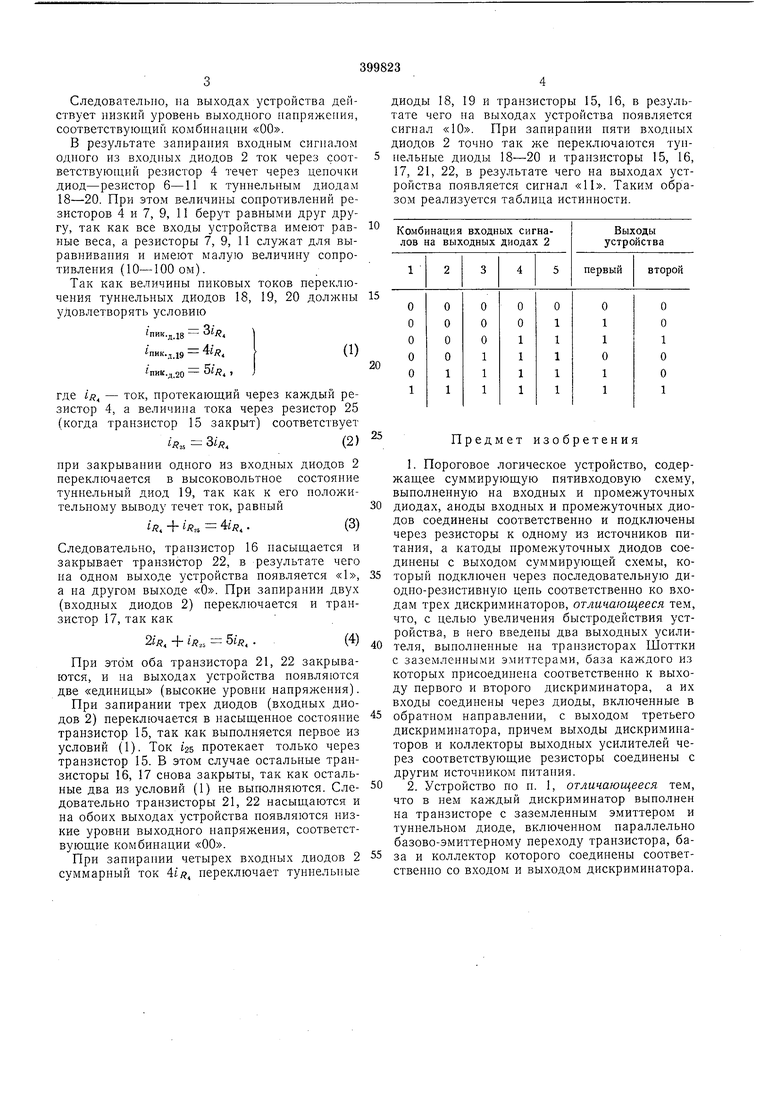

Блок-схема предложенного устройства приведена на чертеже.

Устройство содержит суммирующую пятивходовую схему 1, выполненную на входных 2 и промежуточных 3 диодах, аноды которых соединены и подключены через соответствующие резисторы 4 к одному из источников питания 5. Катоды нромежуточных диодов 3 соединены с выходом суммирующей схемы 1, которая подключена через соответствующую последовательную диодно-резистивную цепь 6 - 11 ко входам дискриминаторов 12-14, каждый из которых выполнен па транзисторе 15-17 с заземленным эмиттером и туннельном диоде 18-20.

Кроме того, устройство содержит два выходных усилителя 21, 22, база каждого из которых соответственно присоединена к выходу дискриминаторов 12, 13, а их входы соединены через дополнительные диоды 23, 24, включенные в обратном направлении, с выходом дискриминатора 14. Выходы дискриминаторов 12-14 и коллекторы выходных усилителей 21, 22 через соответствующие резисторы 25 соединены с другим источником питания 26. В исходном состоянии входные диоды 2 являются проводящими и через резисторы 4 токи протекают. Транзисторы 16, 17 закрыты, а выходные усилители 21, 22 открыты.

Следовательно, на выходах устройства действует низкий уровень выходного напряжения, соответствующий комбинации «00.

В результате занирания входным сигналом одного из входных диодов 2 ток через соответствующий резистор 4 течет через цепочки диод-резистор 6-И к туннельным диодам 18-20. При этом величины сопротивлений резисторов 4 и 7, 9, 11 берут равными друг другу, так как все входы устройства имеют равные веса, а резисторы 7, 9, 11 служат для выравнивания и имеют малую величину сопротивления (10-100 ом).

Так как величины пиковых токов переключения туннельных диодов 18, 19, 20 должны удовлетворять условию

Зг,

(1)

R K

где i, - ток, протекающий через каждый резистор 4, а величина тока через резистор 25 (когда транзистор 15 закрыт) соответствует

;.-З/д,(2)

при закрывании одного из входных диодов 2 переключается в высоковольтное состояние туннельный диод 19, так как к его положительному выводу течет ток, равный

г. + IK,, 4г..(3)

Следовательно, транзистор 16 насыщается и закрывает транзистор 22, в результате чего на одном выходе устройства появляется «1, а на другом выходе «О. При запирании двух (входных диодов 2) переключается и транзистор 17,так как

2г, + гл.з 5iK. (4)

При этом оба транзистора 21, 22 закрываются, и на выходах устройства появляются две «единицы (высокие уровни напряжения).

При запирании трех диодов (входных диодов 2) переключается в насыщенное состояние транзистор 15, так как выполняется нервов из условий (1). Ток t25 протекает только через транзистор 15. В этом случае остальные транзисторы 16, 17 снова закрыты, так как остальные два из условий (1) не выполняются. Следовательно транзисторы 21, 22 насыщаются и на обоих выходах устройства появляются низкие уровни выходного напряжения, соответствующие комбинации «00.

При запирапии четырех входных диодов 2 суммарный ток 4i, переключает туннельные

диоды 18, 19 и транзисторы 15, 16, в результате чего на в з1ходах устройства появляется сигнал «10. При запирании пяти входных диодов 2 точно так же переключаются тупнельные диоды 18-20 и транзисторы 15, 16, 17, 21, 22, в результате чего на выходах устройства появляется сигнал «11. Таким образом реализуется таблица истинности.

Предмет изобретения

1. Пороговое логическое устройство, содержащее суммирующую пятивходовую схему, выполненную на входных и промежуточных

диодах, аноды входных и промежуточных диодов соединены соответственно и подключены через резисторы к одному из источников питания, а катоды промежуточных диодов соединены с выходом суммирующей схемы, который нодключен через последовательную диодно-резистивную цень соответственно ко входам трех дискриминаторов, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены два выходных усилителя, выполненные на транзисторах Шоттки с заземленными эмиттерами, база каждого из которых присоединена соответственно к выходу первого и второго дискриминатора, а их входы соединены через диоды, включенные в

обратном направлепии, с выходом третьего дискриминатора, причем выходы дискриминаторов и коллекторы выходных усилителей через соответствующие резисторы соединены с другим источником питапия.

2. Устройство по п. 1, отличающееся тем, что в нем каждый дискриминатор выполнен на транзисторе с заземленным эмиттером и туннельном диоде, включенном параллельно базово-эмиттерному переходу транзистора, база и коллектор которого соединены соответственно со входом и выходом дискриминатора.

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ЗАПРЕТ» | 1972 |

|

SU423251A1 |

| ДИСКРИМИНАТОР НУЛЕВОГО УРОВНЯ ИМПУЛЬСНОГО СИГНАЛА | 1967 |

|

SU224571A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU429517A1 |

| АМПЛИТУДНЫЙ ДИСКРИМИНАТОР | 1971 |

|

SU302826A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU370728A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1970 |

|

SU269201A1 |

| Пороговое устройство | 1975 |

|

SU598016A1 |

| Логический элемент | 1974 |

|

SU572930A2 |

Авторы

Даты

1973-01-01—Публикация