Изобретение относится к технике связи и может быть применено в дискретных электронных установках, в частности в блоках управления телефонных станций.

Известный мажоритарный логический элемент представляет собой сочетание пороговой схемы на «п входов и нерезервированного усилителя на полупроводниковых триодах.

Известный мажоритарный логический элемент не отвечает условиям резервирования, т. е. при наличии неисправностей внутри мажоритарного логического элемента он теряет свои свойства. Резервирование мажоритарного логического элемента представляет определенные трудности и требует значительного увеличения числа элементов.

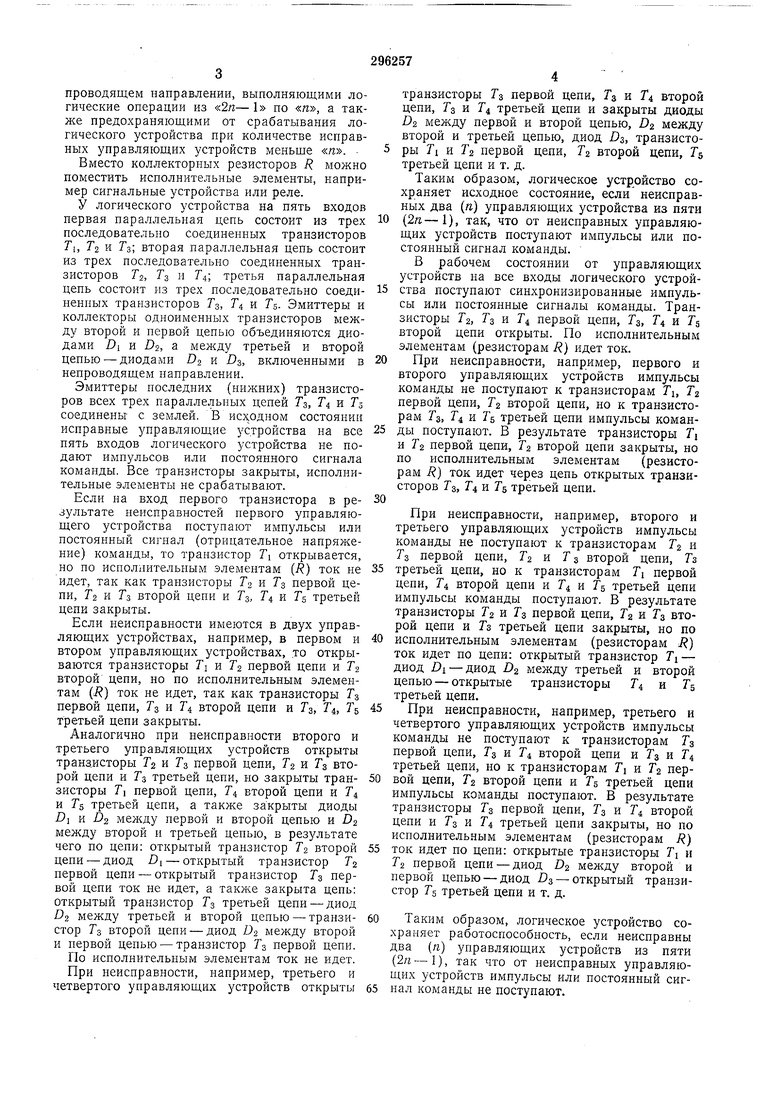

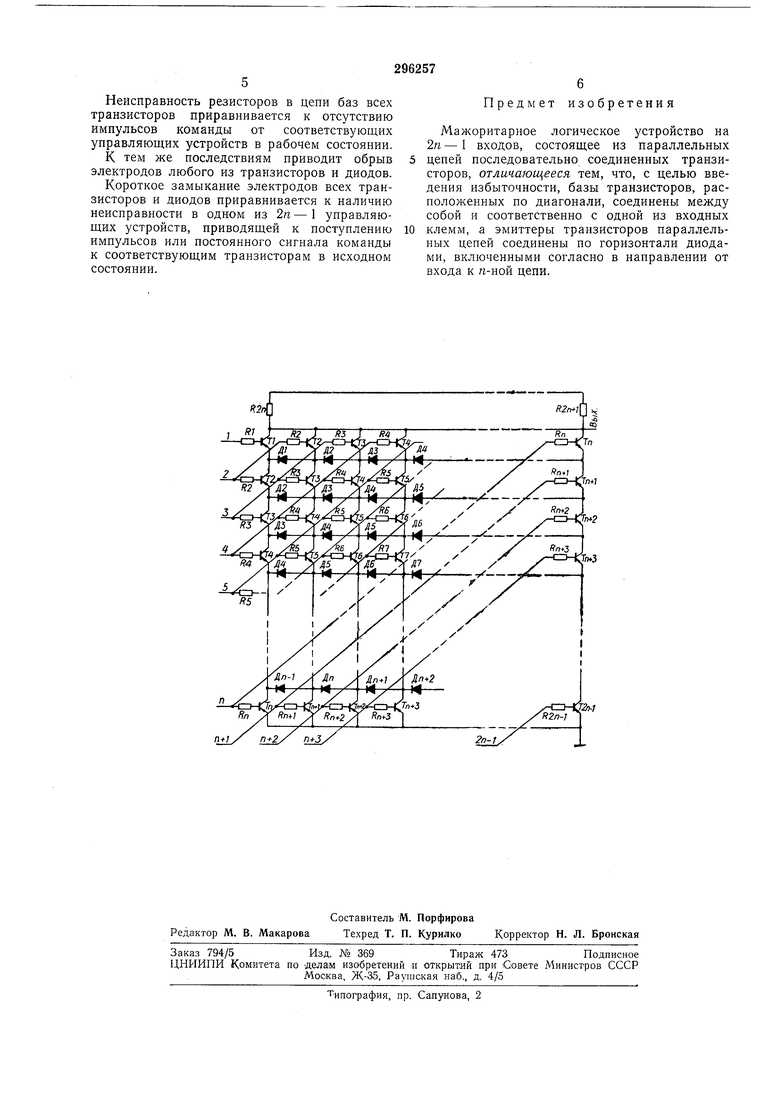

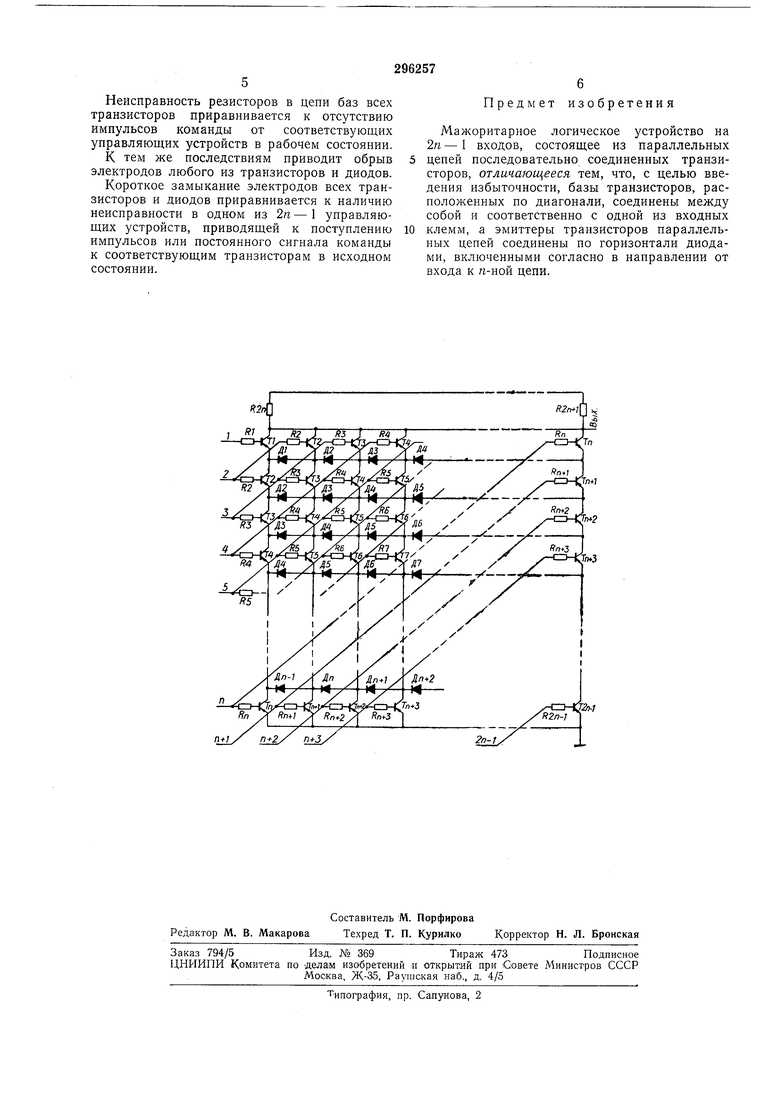

С целью введения избыточности в предлагаемом мажоритарном логическом устройстве базы транзисторов, расположенных по диагонали, соединены между собой и соответственно с одной из входных клемм. Эмиттеры транзисторов параллельных цепей соединены по горизонтали диодами, включенными согласно в направлении от входа к п-ной цепи.

Первая цепь состоит из «д последова тельно соединенных транзисторов TI, TZ, TZ, -, Тп, вторая цепь соответственно из транзисторов Гг, Тз, T,.., Тп+, третья цепь из транзисторов Гз, Т4, TS, .., Тп+г, четвертая цепь из транзисторов Г4, Т, Те,..., Тп+з, пятая цепь из транзисторов ГБ, Ге, Гу, ..., и т. д. Последняя цепь состоит из транзисторов Тп, Тп+1, Tn+z, , Tzn-iТаким образом, номер начального транзи стора каждой параллельной цепи соответ ствует номеру параллельной цепи, считая слева, и является началом для отсчета «п последовательно соединенных транзисторов.

Разные параллельные цепи содержат тран зисторы с одинаковыми номерами.

Одноименные транзисторы TI, TZ, Тз,.., Tzn разных параллельных цепей оказываются расположенными по диагонали и параллельным ей линиям. Базы одноименных транзисторов, расположенных по диагонали и параллельным ей линиям, объединены между собой через входные клеммы 1, 2, 3,..,2п-1 с управляющими устройствами (на чертеже

не показаны), например с одноименными выходами резервируемых счетчиков.

проводящем направлении, выполняющими логические операции из «2я- 1 по «л, а также предохраняющими от срабатывания логического устройства при количестве исправных управляющих устройств меньще «я.

Вместо коллекторных резисторов R можно поместить исполнительные элементы, например сигнальные устройства или реле.

У логического устройства на пять входов первая параллельная цепь состоит из трех последовательно соединенных транзисторов TI, TZ и Гз; вторая параллельная цепь состоит из трех последовательно соединенных транзисторов Гг, Тз и третья параллельная цепь состоит из трех последовательно соедипенпых транзисторов Гз, Т и ГБ- Эмиттеры и коллекторы одноименных транзисторов между второй и первой цепью объединяются диодами DI и DZ, а между третьей и второй цепью - диодами D и з, включенными в непроводящем направлении.

Эмиттеры последних (нилших) транзисторов всех трех параллельных цепей Гз, Т и Гз соединены с землей. В исходном состоянии исправные управляющие устройства на все пять входов логического устройства не подают импульсов или постоянного сигнала команды. Все транзисторы закрыты, исполнительные элементы не срабатывают.

Если на вход первого транзистора в результате неисправностей первого управляющего устройства поступают импульсы или постоянный сигнал (отрицательное напряжение) команды, то транзистор TI открывается, но по исполнительным элементам (R) ток не идет, так как транзисторы TZ и TS первой цепи, TZ и Гз второй цепи и Гз, Т и Гд третьей цени закрыты.

Если неисправности имеются в двух управляющих устройствах, например, в первом и втором управляющих устройствах, то открываются транзисторы TI и TZ нервой цепи и Га второй цепи, но по исполнительным элементам (J) ток не идет, так как транзисторы Гз первой цепи, Гз и Т второй цепи и Га, Т, ГБ третьей цепи закрыты.

Аналогично при неисправности второго и третьего управляющих устройств открыты транзисторы Га и Гз первой цепи, TZ и Гз второй цепи и Гз третьей цепи, но закрыты транзисторы TI первой цепи, Г4 второй цепи и Г4 и Гз третьей цепи, а таклсе закрыты диоды DI и DZ меледу первой и второй цепью и DZ между второй и третьей цепью, в результате чего по цепи: открытый транзистор TZ второй цепи - диод DI - открытый транзистор TZ первой цепи - открытый транзистор Гз первой цепи ток не идет, а также закрыта цепь: открытый транзистор Гз третьей цепи - диод DZ между третьей и второй цепью - транзистор Гз второй цепи - диод DZ между второй и первой цепью - транзистор Гз нервой цени.

транзисторы Гз первой цепи, Гз и Т второй цепи, Гз и Т третьей цепи и закрыты диоды DZ между первой и второй цепью, DZ между второй и третьей цепью, диод DZ, транзисторы TI и Гг первой цепи, TZ второй цепи, Т третьей цепи и т. д.

Таким образом, логическое устройство сохраняет исходное состояние, если неисправных два (п) управляющих устройства из пяти

(2п-1), так, что от неисправных управляющих устройств поступают импульсы или постоянный сигнал команды.

В рабочем состоянии от управляющих устройств на все входы логического устройства поступают синхронизированные импульсы или постоянные сигналы команды. Транзисторы TZ, Гз и Ti первой цепи, Гз, Tt и Гз второй цепи открыты. По исполнительным элементам (резисторам R) идет ток.

При неисправности, например, первого и второго управляющих устройств импульсы команды не поступают к транзисторам Г Гг первой цепи, TZ второй цепи, но к транзисторам Гз, Г4 и ГБ третьей цепи импульсы команды поступают. В результате транзисторы TI и TZ первой цепи. Га второй цепи закрыты, но по исполнительным элементам (резисторам -/) ток идет через цепь открытых транзисторов Гз, Г4 и Гб третьей цепи.

При неисправности, например, второго и третьего управляющих устройств импульсы команды не поступают к транзисторам TZ и Гз первой цепи, Га и Г з второй цепи, Гз

третьей цепи, но к транзисторам TI первой цепи, Г4 второй цепи и Г и TS третьей цепи импульсы команды поступают. В результате транзисторы TZ и Гз первой цепи. Га и Гз второй цепи и Гз третьей цепи закрыты, но по

исполнительным элементам (резисторам J) ток идет по цепи: открытый транзистор TI - диод DI - диод DZ между третьей и второй цепью - открытые транзисторы Т и Тг, третьей цепи.

При неисправности, например, третьего и четвертого управляющих устройств импульсы команды не поступают к транзисторам Гз первой цепи, Гз и Г второй цепи и Гз и Г4 третьей цепи, но к транзисторам Г и Га первой цепи, TZ второй цепи и TS третьей цепи импульсы команды поступают. В результате транзисторы Гз первой цепи, Гз и Г4 второй цепи и Гз и Г4 третьей цепи закрыты, но по исполнительным элементам (резисторам R)

ток идет по цепи: открытые транзисторы TI и TZ первой цепи - диод DZ между второй и нервой цепью - диод -открытый трапзистор Гд третьей цепи и т. д.

Таким образом, логическое устройство сохраняет работоспособность, если неисправны два (п) управляющих устройств из пяти (2/г - 1), так что от неисправных управляющих устройств импульсы или постоянный сигНеисправность резисторов в цепи баз всех транзисторов приравнивается к отсутствию импульсов команды от соответствующих управляющих устройств в рабочем состоянии.

К тем же последствиям приводит обрыв электродов любого из транзисторов и диодов.

Короткое замыкание электродов всех транзисторов и диодов приравнивается к наличию неисправности в одном из 2п-1 управляющих устройств, приводящей к поступлению импульсов или постоянного сигнала команды к соответствующим транзисторам в исходном состоянии.

Предмет изобретения

Мажоритарное логическое устройство на 2га - 1 входов, состоящее из параллельных цепей последовательно соединенных транзисторов, отличающееся тем, что, с целью введения избыточности, базы транзисторов, располол енных по диагонали, соединены между собой и соответственно с одной из входных клемм, а эмиттеры транзисторов параллельных цепей соединены по горизонтали диодами, включенными согласно в направлении от входа к «-ной цепи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковый силовой выключатель | 1961 |

|

SU150159A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ХОДАМИ ПРЕССА | 1972 |

|

SU341154A1 |

| УСТРОЙСТВО для ФОРМИРОВАНИЯ БИПОЛЯРНЫХ ИМПУЛЬСОВ УПРАВЛЕНИЯ | 1972 |

|

SU343349A1 |

| УСТРОЙСТВО для ЗАРЯДА АККУМУЛЯТОРНОЙ БАТАРЕИ | 1973 |

|

SU369757A1 |

| Устройство для автоматического вождения мобильного агрегата по светоконтрастной программе | 1974 |

|

SU683662A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРИЧЕСКИМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1965 |

|

SU176000A1 |

| ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 1968 |

|

SU217447A1 |

| УСТРОЙСТВО СРАВНЕНИЯBv^:: ШШt~ 1 еC-J'-i | 1973 |

|

SU374575A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ СТАБИЛИЗАЦИИ | 1970 |

|

SU284099A1 |

| РЕЛЕЙНЫЙ РАСПРЕДЕЛИТЕЛЬ | 1972 |

|

SU330564A1 |

/

R4

RS

3

Даты

1971-01-01—Публикация