Изобретение относится к области радиотехники и связи и может быть использовано в качестве входных и промежуточных каскадов аналоговых микросхем различного функционального назначения (высокочастотных и сверхвысокочастотных усилителях, драйверах линий связи, фильтрах и т.д.).

Известны высокочастотные усилители на основе дифференциальных каскадов с токовым (эмиттерным) входом [1-20], которые стали основой построения многих аналоговых узлов современных систем связи. Проблема улучшения их параметров относится к числу одной из актуальных проблем современной аналоговой микросхемотехники.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы

(Uкэ.max=2,9 B или напряжение двуполярного питания ±1,5В). Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем. Предлагаемое изобретение относится к данному направлению развития микроэлектроники.

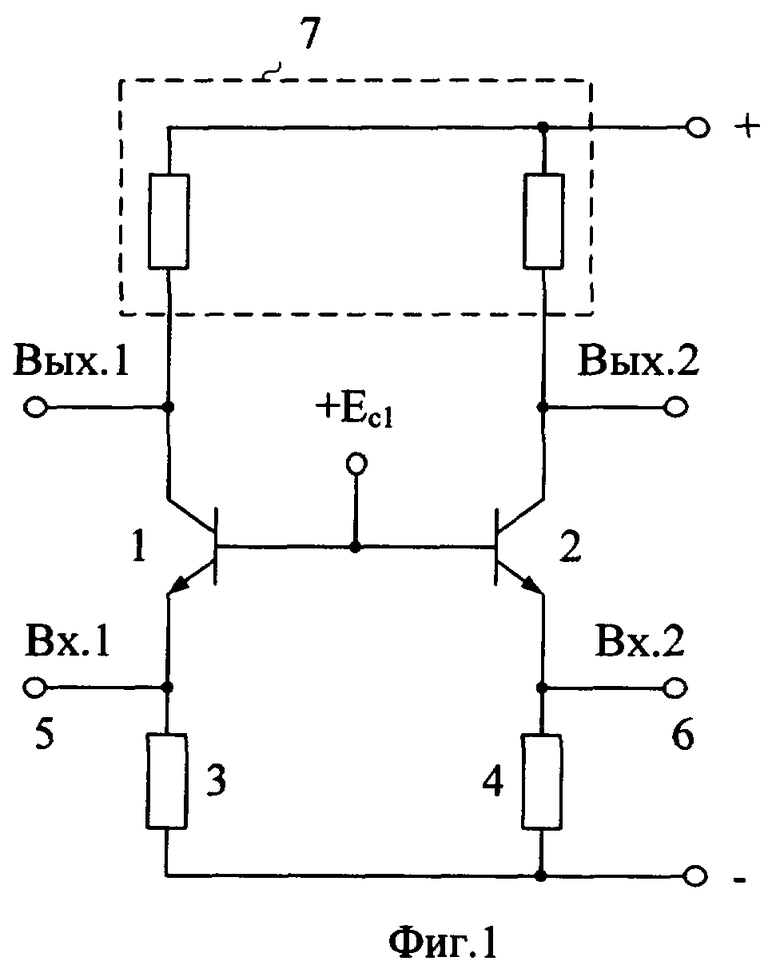

Ближайшим прототипом заявляемого устройства является классический высокочастотный дифференциальный каскад (фиг.1), рассмотренный в патенте США №4065724 (фиг.1а), который содержит первый 1 и второй 2 входные транзисторы с объединенными базами, первый 3 и второй 4 токостабилизирующие двухполюсники, соединенные с эмиттерами соответствующих первого 1 и второго 2 входных транзисторов и первым 5 и вторым 6 токовыми входами дифференциального усилителя, цепь нагрузки 7, связанную с коллекторами первого 1 и второго 2 входных транзисторов.

Существенный недостаток известного высокочастотного дифференциального усилителя (ВДУ) состоит в том, что он неработоспособен при изменении входного синфазного сигнала более чем на 50÷100 мВ. Этот недостаток наиболее существенно проявляется при использовании заявляемого устройства в качестве входной подсхемы различных аналоговых устройств с дифференциальным входом и непосредственной связью каскадов.

Основная цель предлагаемого изобретения состоит в расширении диапазона изменения входных синфазных сигналов ВДУ при сохранении его свойств как усилителя с токовым (низкоомным) дифференциальным входом. Дополнительная цель - построение структуры ВДУ с потенциальным (высокоомным) входом, работоспособной при ее выполнении в рамках техпроцесса SGB25VD.

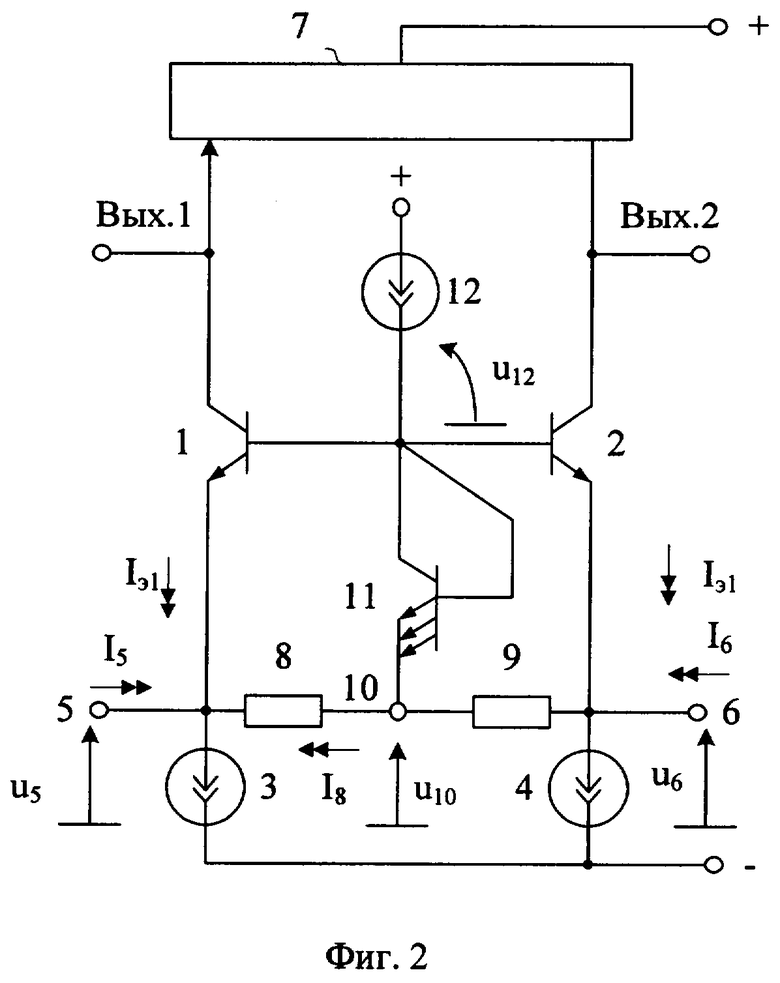

Поставленная цель достигается тем, что в известном устройстве фиг.1, содержащем первый 1 и второй 2 входные транзисторы с объединенными базами, первый 3 и второй 4 токостабилизирующие двухполюсники, соединенные с эмиттерами соответствующих первого 1 и второго 2 входных транзисторов и первым 5 и вторым 6 токовыми входами дифференциального усилителя, цепь нагрузки 7, связанную с коллекторами первого 1 и второго 2 входных транзисторов, предусмотрены новые элементы и связи - между эмиттерами первого 1 и второго 2 входных транзисторов включены два последовательно соединенных дополнительных резистора 8 и 9, общий узел 10 которых через дополнительный р-n переход 11 соединен с базами первого 1 и второго 2 входных транзисторов и дополнительным токостабилизирующим двухполюсником 12.

Предлагаемый высокочастотный дифференциальный усилитель (фиг.2), в соответствии с п.1, п.3 формулы изобретения, содержит первый 1 и второй 2 входные транзисторы с объединенными базами, первый 3 и второй 4 токостабилизирующие двухполюсники, соединенные с эмиттерами соответствующих первого 1 и второго 2 входных транзисторов и первым 5 и вторым 6 токовыми входами дифференциального усилителя, цепь нагрузки 7, связанную с коллекторами первого 1 и второго 2 входных транзисторов. Между эмиттерами первого 1 и второго 2 входных транзисторов включены два последовательно соединенных дополнительных резистора 8 и 9, общий узел 10 которых через дополнительный р-n переход 11 соединен с базами первого 1 и второго 2 входных транзисторов и дополнительным токостабилизирующим двухполюсником 12.

В устройстве по п.2 формулы изобретения (фиг.2) дифференциальный усилитель имеет первый 13 и второй 14 потенциальные входы, причем между первым 13 потенциальным входом и первым 5 токовым входом включен первый 15 эмиттерный повторитель, а между вторым 14 потенциальным входом и вторым 6 токовым входом включен второй 16 эмиттерный повторитель.

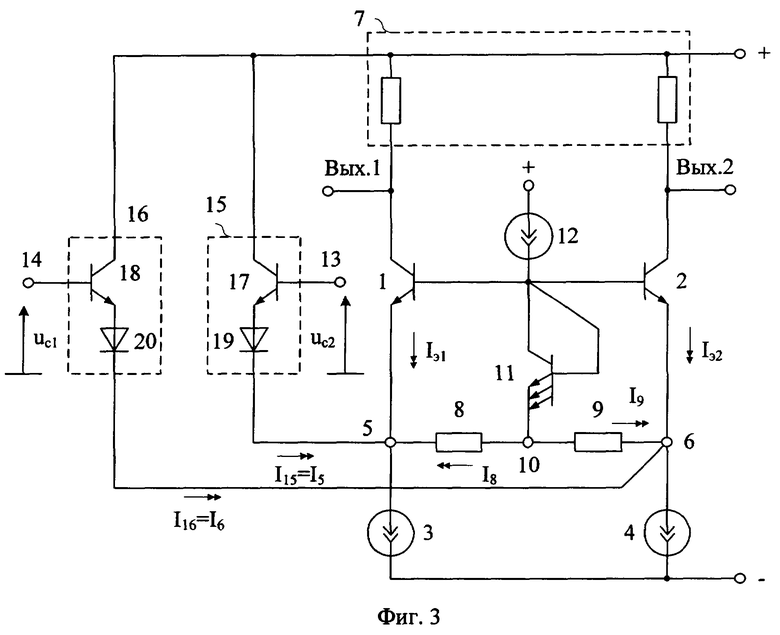

В устройстве фиг.3, соответствующем п.3 формулы изобретения, первый 15 и второй 16 эмиттерные повторители выполнены на основе первого 17 и второго 18 дополнительных транзисторов и первой 19 и второй 20 цепи согласования потенциалов.

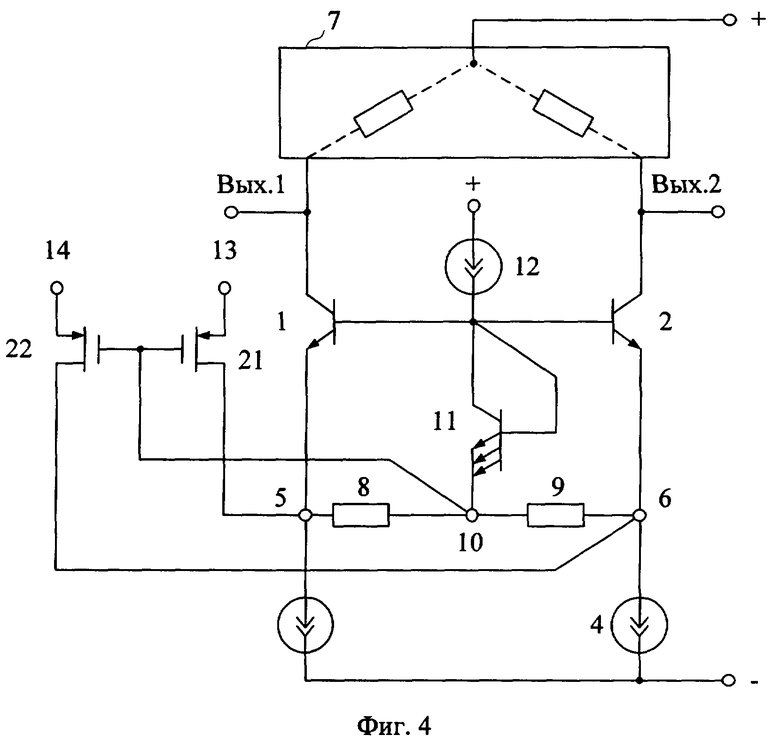

В усилителе фиг.4, соответствующем п.4 формулы изобретения, в схему введены первый 21 и второй 22 вспомогательные транзисторы, истоки (эмиттеры) которых подключены к соответствующим потенциальным входам 13 и 14 дифференциального усилителя, стоки (коллекторы) связаны с соответствующими первым 5 и вторым 6 токовыми входами дифференциального усилителя, а затворы объединены и соединены с общим узлом 10 дополнительных резисторов 8 и 9.

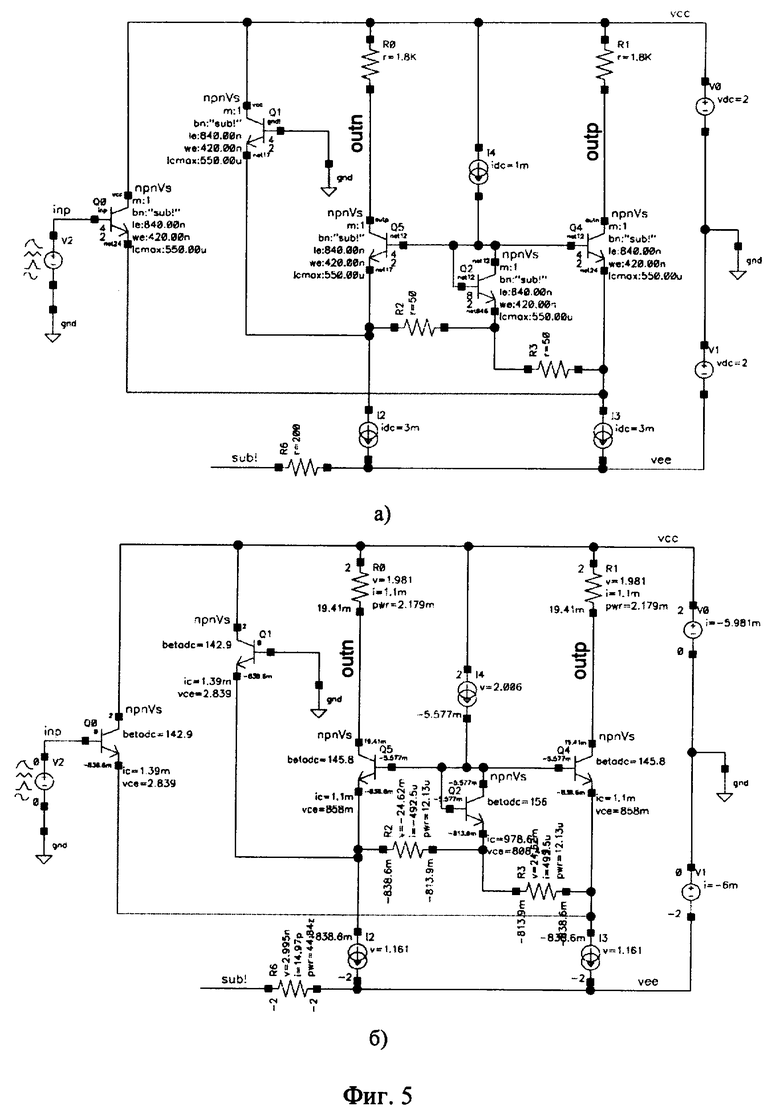

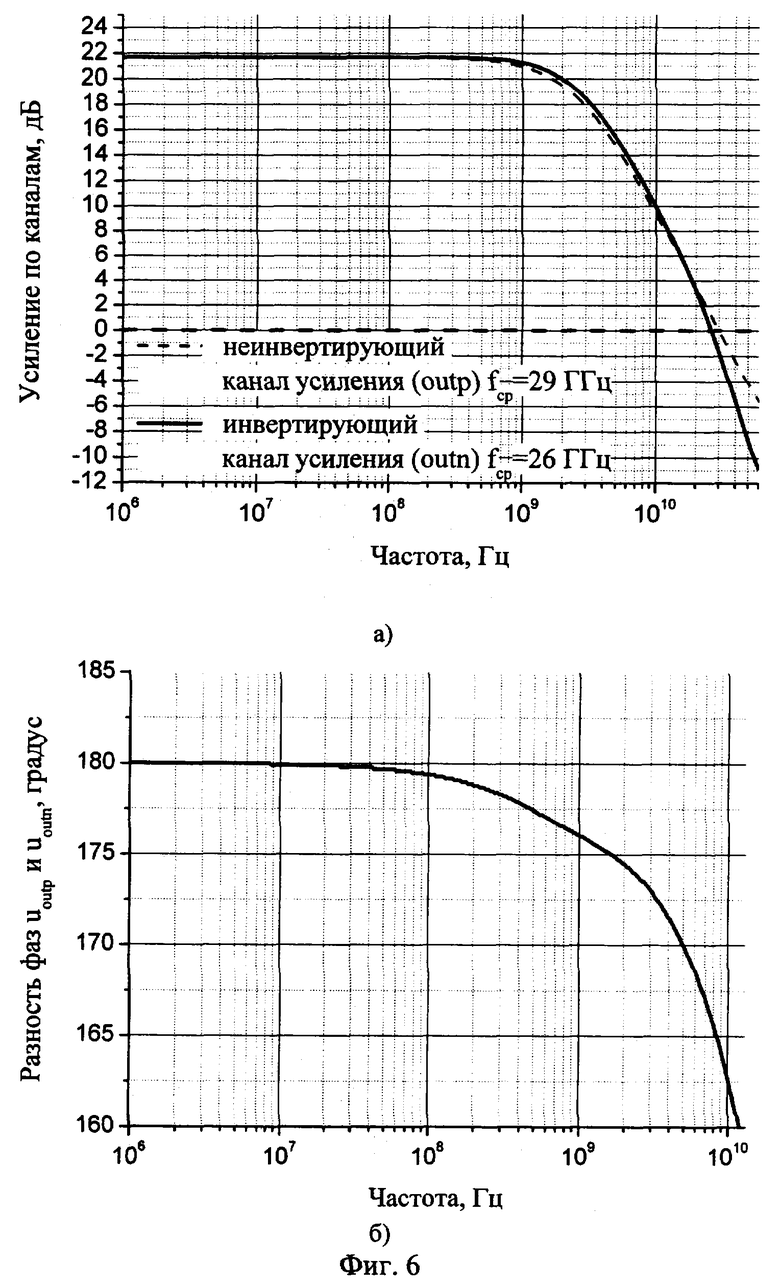

На чертеже фиг.5 показана схема заявляемого устройства фиг.2 и ее статический режим (фиг.5б) в среде Cadance на моделях SiGe интегральных транзисторов IHP, а на чертеже фиг.6а - зависимость его коэффициента усиления по напряжению от частоты для инвертирующего и неинвертирующего выходов, а также фазочастотная характеристика разомкнутого усилителя (фиг.6б).

Рассмотрим работу схемы фиг.2.

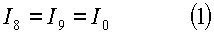

В статическом режиме ток источника опорного тока 12 I12=2I0 поступает в узел 10 и делится пополам между резисторами 8 (R8) и 9 (R9):

За счет выбора отношения площадей эмиттеров транзисторов 11 и

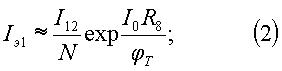

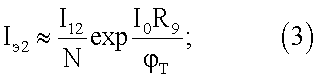

1 (2) N=S11/S1=S11/S2>>1 этим током I12=2I0 устанавливаются токи эмиттера транзисторов 1 и 2:

где φT≈25 мВ - температурный потенциал.

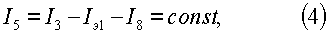

Таким образом, при входных потенциальных сигналах u5=u6 входной ток узла 5 (6) в схеме фиг.2 (в отличие от ВДУ-прототипа) остается постоянным в широком диапазоне их изменения u5=u6=uc.

Поэтому синфазное изменение u5=u6=uc не изменяет токи в схеме фиг.2. Здесь входной синфазный сигнал uc передается в узел 10 и далее, в цепь базы транзистора 1 (2) с единичной передачей:

Следовательно, амплитуда синфазного напряжения ДУ фиг.2 не изменяет токи в схеме, которые определяются источником I12, резистором 8 (9), р-n переходами транзисторов 1, 2, 11, двухполюсником I3 (I4). Поэтому ВДУ остается работоспособным при uc>>2φT.

Дифференциальный сигнал uBX=u56=u5-u6 прикладывается к резисторам 8 и 9 и делится ими пополам

вызывая увеличение напряжения на резисторе 8 и уменьшение на резисторе 9. Это приводит к увеличению напряжения эмиттер-база транзистора 1 и уменьшению напряжения эмиттер-база транзистора 2. Поэтому эмиттерный ток транзистора 11 возрастает, а транзистора 2 уменьшается. Эти приращения передаются в нагрузку 7, с которой снимается усиленный сигнал. При этом входное дифференциальное сопротивление ВДУ остается низкоомным.

В схеме фиг.3 токи I5=I6 протекают по эмиттерной цепи транзисторов 17, 18 эмиттерных повторителей напряжения 15 и 16. Изменения напряжений на входах 13 и 14 uc1≠uc2 управляют величиной токов Iэ1, Iэ2 и далее токами коллекторов транзисторов 1 и 2. Схема фиг.3 имеет высокоомные дифференциальные входы 13 и 14.

Особенность схемы фиг.4 в отличие от схемы фиг.3 - наличие полевых транзисторов 21 и 22, потенциал затвора которых устанавливается резисторами 8 и 9. Полевые транзисторы изготавливаются также в рамках техпроцесса SGB25VD.

Компьютерное моделирование фиг.6 показывает, что предлагаемый дифференциальный усилитель обеспечивает усиление по напряжению Ку>1 до частоты 26 ГГц по инвертирующему и неинвертирующему выходам.

Таким образом, предлагаемое схемотехническое решение позволяет использовать СВЧ SiGe-транзисторы техпроцесса SGB25VD с относительно низким напряжением питания 2,9 В в структуре не только различных аналоговых устройств, но и СФ блоков систем на кристалле. Этот важный результат расширяет область практического использования SGB25VD технологии и, следовательно, повышает технико-экономические показатели микроэлектронных изделий. Так, например, создание новой (под указанную технологию) схемотехники широкодиапазонных операционных усилителей позволит не только повысить качественные показатели СВЧ фильтров, квадратурных модуляторов, демодуляторов и других устройств нового поколения, образующих СФ блоки СВЧ РЭА, но и создать новую номенклатуру ИС широкого функционального применения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6621308.

2. Патент США №6639473 (фиг.2).

3. Патент США №5900779.

4. Патент США №5973562.

5. Патент США №4887047.

6. Патент США №3972003.

7. Патент США №4521739.

8. Патент США №4277756.

9. Патент США №6181207.

10. Патент США №4065724.

11. Патент RE 30587.

12. Патент США №6882224.

13. Патент США №4232271.

14. Патент США №5345073.

15. Патентная заявка США №2005/0140443.

16. Патентная заявка США №2005/0140444.

17. Патент Франции №2337969.

18. Патент Японии № 2001308658.

19. Авт. св. СССР №711665.

20. Авт. св. СССР №1084961.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2419191C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| ФАЗОРАСЩЕПИТЕЛЬ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 2011 |

|

RU2439782C1 |

| ВЫСОКОЧАСТОТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2396697C2 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382483C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441314C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве входных и промежуточных каскадов аналоговых микросхем различного функционального назначения (высокочастотных и сверхвысокочастотных усилителях, драйверах линий связи, фильтрах и т.д.). Технический результат - расширение диапазона изменения входных синфазных сигналов. Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы с объединенными базами, первый (3) и второй (4) токостабилизирующие двухполюсники, соединенные с эмиттерами соответствующих первого (1) и второго (2) входных транзисторов и первым (5) и вторым (6) токовыми входами дифференциального усилителя, цепь нагрузки (7), связанную с коллекторами первого (1) и второго (2) входных транзисторов. Между эмиттерами первого (1) и второго (2) входных транзисторов включены два последовательно соединенных дополнительных резистора (8) и (9), общий узел (10) которых через дополнительный р-n переход (11) соединен с базами первого (1) и второго (2) входных транзисторов и дополнительным токостабилизирующим двухполюсником (12). 3 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы с объединенными базами, первый (3) и второй (4) токостабилизирующие двухполюсники, соединенные с эмиттерами соответствующих первого (1) и второго (2) входных транзисторов и первым (5) и вторым (6) токовыми входами дифференциального усилителя, цепь нагрузки (7), связанную с коллекторами первого (1) и второго (2) входных транзисторов, отличающийся тем, что между эмиттерами первого (1) и второго (2) входных транзисторов включены два последовательно соединенных дополнительных резистора (8) и (9), общий узел (10) которых через дополнительный р-n-переход (11) соединен с базами первого (1) и второго (2) входных транзисторов и дополнительным токостабилизирующим двухполюсником (12).

2. Устройство по п.1, отличающееся тем, что дифференциальный усилитель имеет первый (13) и второй (14) потенциальные входы, причем между первым (13) потенциальным входом и первым (5) токовым входом включен первый (15) эмиттерный повторитель, а между вторым (14) потенциальным входом и вторым (6) токовым входом включен второй (16) эмиттерный повторитель.

3. Устройство по п.2, отличающееся тем, что первый (15) и второй (16) эмиттерные повторители выполнены на основе первого (17) и второго (18) дополнительных транзисторов и первой (19) и второй (20) цепи согласования потенциалов.

4. Устройство по п.1, отличающееся тем, что в схему введены первый (21) и второй (22) вспомогательные транзисторы, истоки (эмиттеры) которых подключены к соответствующим потенциальным входам (13) и (14) дифференциального усилителя, стоки (коллекторы) связаны с соответствующими первым (5) и вторым (6) токовыми входами дифференциального усилителя, а затворы объединены и соединены с общим узлом (10) дополнительных резисторов (8) и (9).

| US 4065724 A, 27.12.1977 | |||

| Повторитель тока | 1987 |

|

SU1529410A1 |

| US 4105942 A, 08.08.1978 | |||

| US 3482177, 02.12.1969. | |||

Авторы

Даты

2009-11-27—Публикация

2008-03-07—Подача