Изобретение относится к импульсной технике и касается усовершенствования преобразователей частоты, предназначенных для деления частоты следования импульсов на большие простые числа.

Известен делитель частоты импульсов, содержащий источник входных сигналов, релаксационные неавтономные делители частоты, выполненные, например, на двух транзисторах разного типа проводимости с времязадающей / С-цепочкой, подключенной к эмиттеру входного транзистора, и распределитель напряжения, выполненный на ячейках с ключевыми элементами, соединенными по кольцевой схеме, и имеющий раздельные входы управления.

Однако такой делитель частоты сложен и вследствие этого недостаточно надежен в работе.

Цель изобретения--упрощение устройства и повышение его надежности.

Для этого в предлагаемом устройстве резисторы, определяющие кратность деления, включены между эмиттерами транзисторов неавтономных делителей частоты и одной из шин питающего напряжения с блокировкой через распределитель напряжения, управляющие входы которого подключены к выходам делителей.

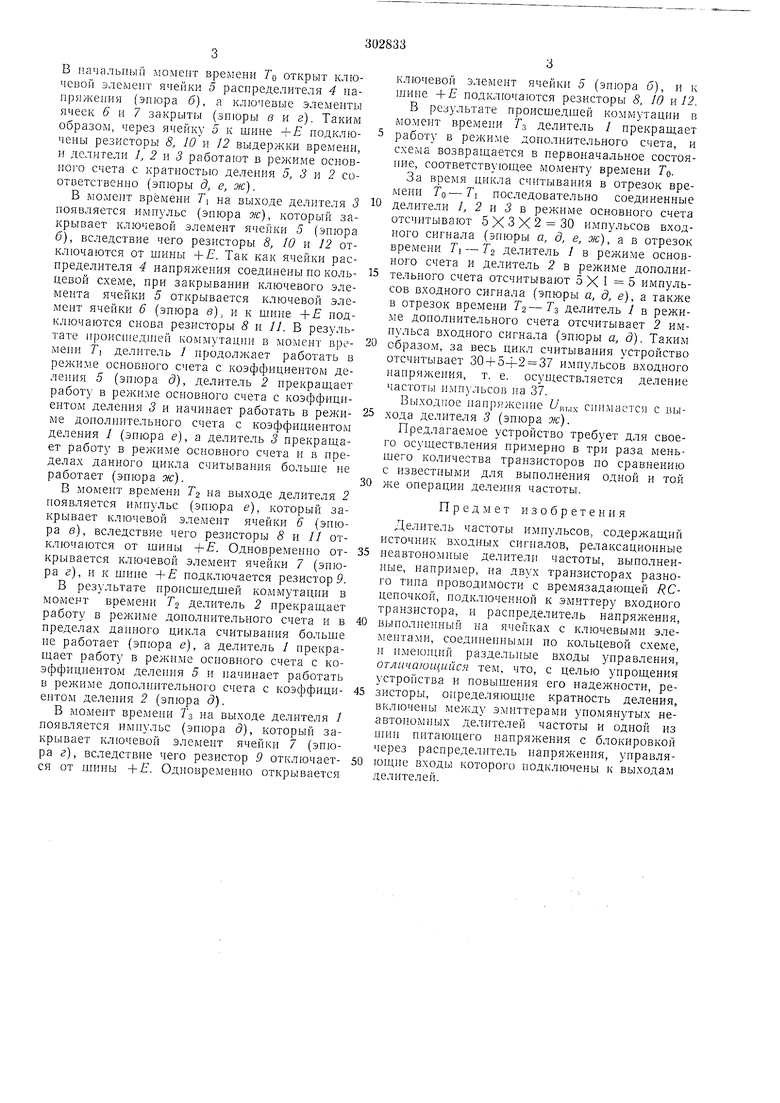

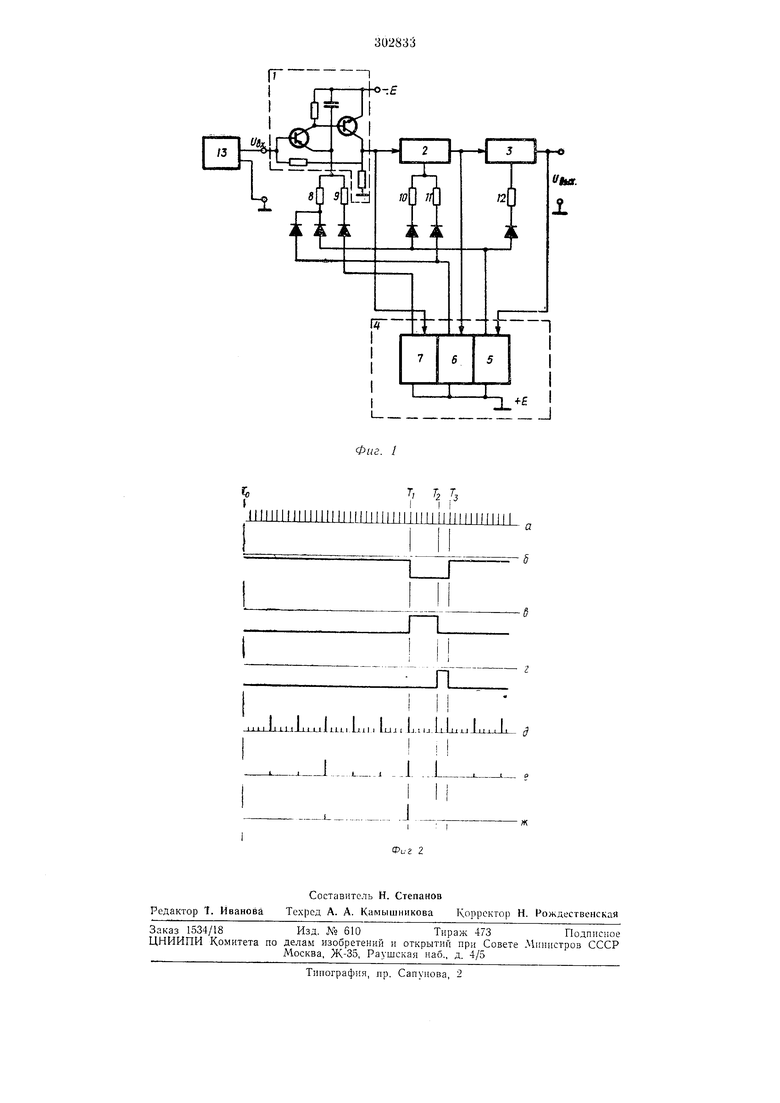

На фиг. 1 приведена принципиальная схема делителя частоты импульсов; на фиг. 2-эпюры соответствующих напряжений. Предлагаемое устройство может быть показано на примере трехкаскадного делителя, который выполнен на трех релаксационных неавтономных делителях 1, 2 3 частоты, и распределителе 4 напряжения, содержащем три ячейки 5, 6 и 7 с ключевыми элементами.

Ячейки распределителя 4 напряжения соединены по кольцевой схеме и имеют раздельные входы управления. Выход делителя / подключен к входам делителя 2 и ячейки 7, выход делителя 2 соединен с входами делителя

3 и ячейки 6, а выход делителя 3 связан с входом ячейки 5.

Резисторы 8-12 выдержки времени делителей частоты, с помощью которых делители настраиваются на соответствующие коэффициенты деления, подключены к положительной шине +Е питающего напряжения через ключевые элементы ячеек распределителя 4 напряжения следующим образом: резисторы 8, 10 и 12 через ячейку 5, резисторы 8 11 через ячейку 6, резистор 9 через ячейку 7.

Работа предлагаемого делителя частоты рассматривается на примере деления на 37 при помощи трехкаскадного делителя.

В начальный момент времени TQ открыт ключевой элемент ячейки 5 распределителя 4 нанряжеиия (эпюра б, а ключевые элементы ячеек 6 и 7 закрыты (эпюры виг). Таким образом, через ячейку 5 к шине +Е подключены резиеторы 8, 10 и 12 выдерл ки времени, и делители 1, 2 ii 3 работают в режиме основного ечета с кратностью деления 5, 3 и 2 соответственно (эпюры д, в, ж).

В MOAieiiT времени TI на выходе делителя 3 появляется имнульс (эпюра ж), который закрывает ключевой элемент ячейки 5 (эпюра б), вследствие чего резисторы 8, 10 и 12 отключаются от шины +Е. Так как ячейки распределителя 4 нанряжения соединены по кольцевой схеме, при закрывании ключевого элемента ячейки 5 открывается ключевой элемент ячейки 6 (эпюра в, и к +Е подключаются снова резисторы 8 и //. В результате происп1едн1ей коммутации в момент времени Г делитель / продолжает работать в режиме основного счета с коэффициентом деления 5 (эпюра д), делитель 2 прекращает работу в режиме основного счета с коэффициентом деления 3 и начинает работать в режиме дополнительного счета с коэффициентом деления / (эпюра е), а делитель 3 прекращает работу в режиме основного счета и в пределах данного цикла считывания больше не работает (эпюра ж.

В момент времени Т на выходе делителя 2 ноявляется имнульс (эпюра е), который закрывает ключевой элемент ячейки б (энюра в), вследствие чего резисторы 8 и // отключаются от щины +Е. Одновременно открывается ключевой элемент ячейки 7 (энюра г, и к щипе +Е подключается резистор Р.

В результате происшедшей коммутации в момент времени Т- делитель 2 прекращает работу в режиме донолнительного счета и в пределах данного цикла считывания больше не работает (энюра е, а делитель / прекращает работу в режиме основного счета с коэффициентом деления 5 и начииает работать в режиме донолнительного счета с коэффициентом деления 2 (эпюра д).

В момент времени 7з на выходе делителя / ноявляется имнульс (эпюра д), который закрывает ключевой элемент ячейки 7 (эпюра г, вследствие чего резистор 9 отключается от щины +Е. Одновременно открывается

ключевой элемент ячейки 5 (энюра б), и к шине +Е нодключаются резисторы 8, 10 и 12. В результате происшедшей коммутации в момент времени Тз делитель / прекращает 5 работу в режиме донолнительного счета, и схема возвращается в первоначальное состояние, соответствующее моменту времени Го.

За время цикла считывания в отрезок времени TO-TI последовательно соединенные

0 делители J, 2 и 3 в режиме основного счета отсчитывают 5 X 3 X 2 30 импульсов входного сигнала (энюры а, д, е, ж), а в отрезок времени 7j - TZ делитель 1 в режиме основного счета и делитель 2 в режиме донолни5 тельного счета отсчитывают импульсов входного сигнала (эпюры а, д, е), а также в отрезок времени Га-УЗ делитель / в режиме дополнительного счета отсчитывает 2 импульса входного сигнала (эпюры а, д). Таким

0 образом, за весь цикл считывания устройство отсчитывает 30-f 5-4-2 37 нмнульсов входного нанряжения, т. е. осун ествляется деление частоты импульсов на 37.

Выходное напр5 женне /7,,,,,,; снимается с вы5 хода делителя 3 (эпюра ж).

Предлагаемое устройство требует для своего осуществления примерно в три раза меньшего количества транзисторов по сравнению с известными для выполнения одной и той

0 же операции деления частоты.

Предмет изобретения

Делитель частоты имнульсов, содержащий источник входных сигналов, релаксационные

5 неавтономные делители частоты, выполненные, например, на двух транзисторах разного типа проводимости с времязадающей У Сцепочкой, подключенной к эмиттеру входного транзистора, и распределитель напряжения,

0 выполненный на ячейках с ключевыми элементами, соединенными но кольцевой схеме, и имеюн(ий раздельные входы управления, отличающийся тем, что, с целью упрощения устройства и новыщения его надежности, резисторы, определяющие кратность деления, включены между эмиттерами упомянутых неавтономных делителей частоты и одной из шин нитающего напряжения с блокировкой через распределитель нанряжения, унравля0 ющне входы которого подключены к выходам делителей.

ГГ

Фиг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1972 |

|

SU330444A1 |

| УДК 681.118.1 (088.8) | 1974 |

|

SU380187A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| Преобразователь-стабилизатор постоянного напряжения | 1972 |

|

SU491941A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1972 |

|

SU354539A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| Генератор прямоугольных импульсов | 1972 |

|

SU604137A1 |

| ВПТБ Ш14Ш11Жу1 | 1973 |

|

SU409292A1 |

| РЕЛАКСАЦИОННЫЙ НЕАВТОНОМНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1969 |

|

SU233745A1 |

| Каскодный формирователь высоковольтных импульсов на емкостной нагрузке | 1972 |

|

SU492033A1 |

ни 111ijJLu-i..iliLii.Lii 11ид L.iij-u-Lui-j .J, .„.. Л .Ll..

, j

Даты

1971-01-01—Публикация