1

Изобретение относится к вычислительной технике.

Известны тирнсторно-транзисторные ячейки памяти, содержащие тиристор и транзисторы заниси и считывания.

Цель изобретения - снижение потребления энергии.

Для этого в нредлагаемой ячейке памяти /з-база тиристора соединена с коллектором транзистора записи «О, /г-база - с коллектором транзистора записи «1 и через диод с выходной разрядной шиной, один из катодов тиристора соединен с эмиттерами транзисторов заниси «О и «1 и адресной шиной, а другой - с положительной шиной источника опорного напряжения, причем базы транзисторов заииси «О и «1 нодсоединены к соответствуюшим входным разрядным шинам.

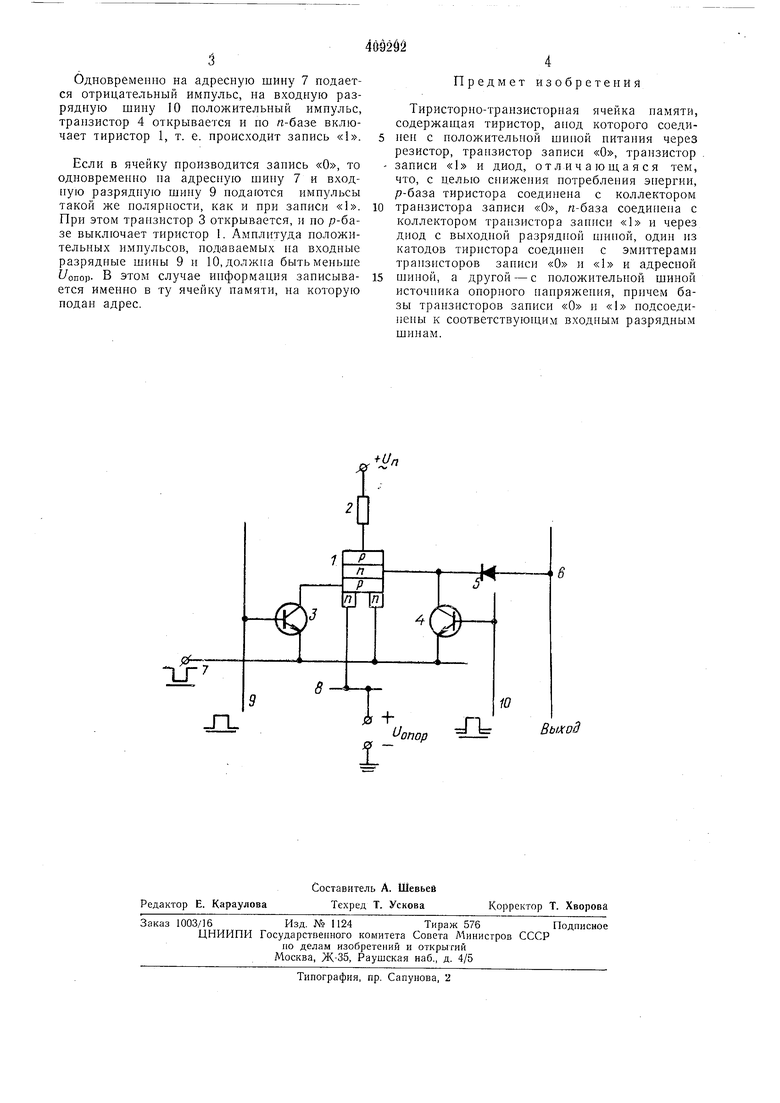

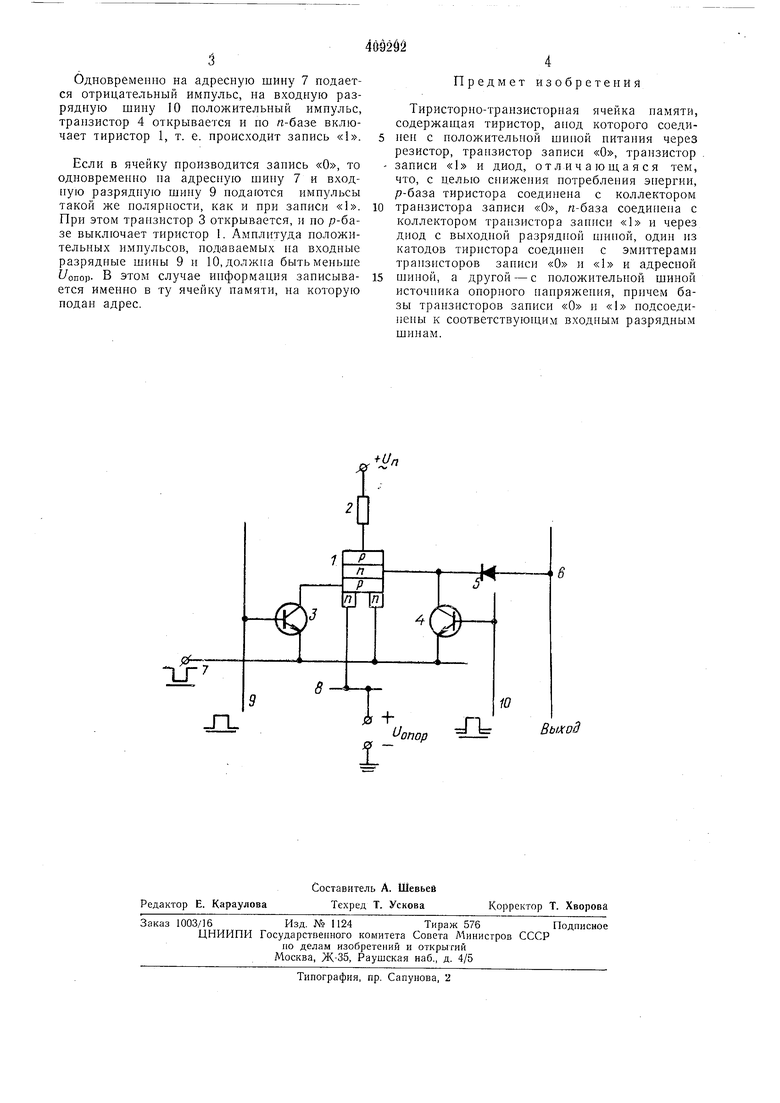

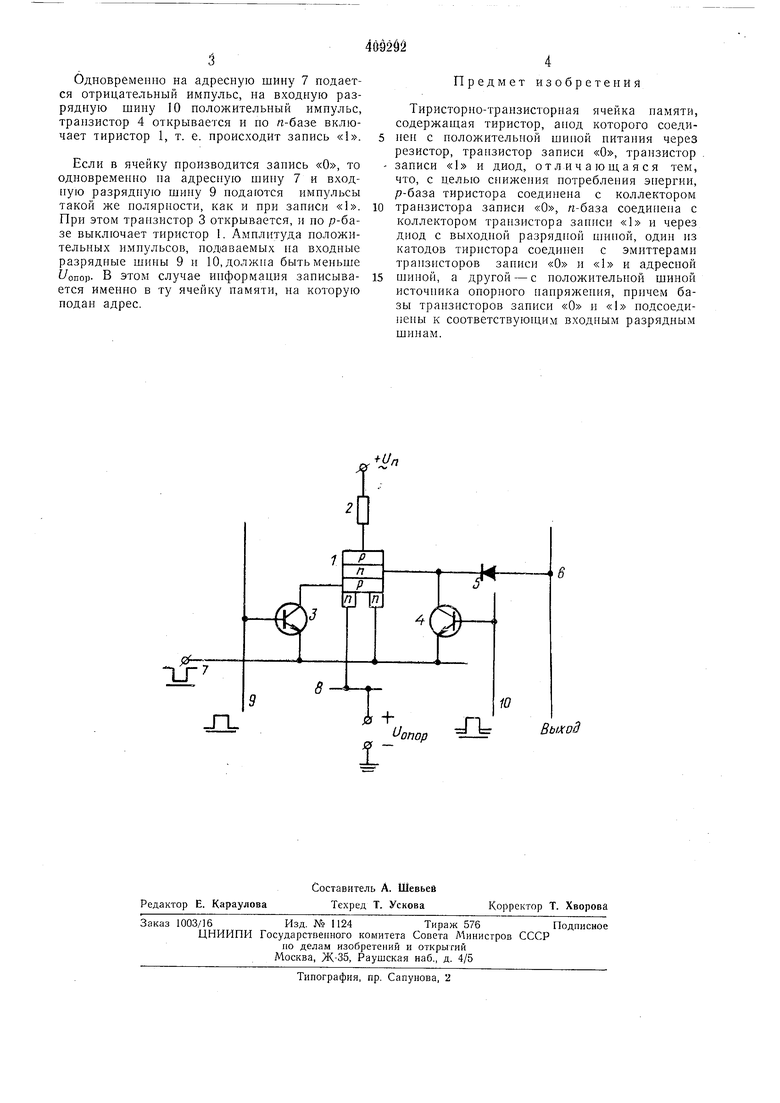

На чертеже приведена схема предлагаемой тиристорно-транзисторной ячейки намяти.

Она содержит тиристор I, анод которого через резистор 2 соединен с положительной шиной питания, р-база тиристора соединена с коллектором транзистора 3 записи «О, я-база - с коллектором транзистора 4 заниси «1 и через диод 5 с выходной разрядной шиной 6. Один из катодов тиристора соединен с эмиттерами транзисторов заниси 3 и 4 и адресной шнной 7, а другой катод тиристора - с положительной шиной 8 источника опорного напряжения, причем базы транзисторов 3 и 4 заниси подсоединены соофетственно к входным разрядным шинам 9 иЁЮ.

Предлагаемая ячейка намяти может быть изготовлена в интегральном исполнении.

В режиме хранения информации входные

разрядные шины 9 и 10 имеют низкий уровень

сигнала, адресная шина 7 имеет потенциал

больший, чем напряжение Uonop- Напряжение

на выходной разрядной шине 6 равно UonopПредположим, что «1 информации соответствует включенное состояние тиристора, а «О - выключенное. Если в ячейке запнсана «1, то через тиристор 1, резистор 2 нротекает ток. Транзисторы 3 н 4 заперты. Диод 5 также заперт, так как его аиод и катод имеют одинаковые потенциалы. В режиме считывания информации на адресную шину 7 нодается низкий нотеициал. Наиряжение на катоде тиристора ноннжается до потенциала земли, диод 5 отнирается, и на выходной шине 6 напряжение понижается до уровня прямого падения наиряжения на диоде.

При этом на выходной разрядной шиие 6 формируется импульс отрицательной полярности, длительность которого равна длительности импульса на адресной шине 7. Занись информации производится следующим образом. Одновременно на адресную шину 7 подается отрицательный имнульс, на входную разрядную шину 10 ноложительный имнульс, транзистор 4 открывается н но п-базе включает тиристор 1, т. е. нронсходнт занись «1. Если в ячейку нроизводится занись «О, то одновременно на адресную шину 7 и входную разрядную шину 9 подаются имнульсы такой же нолярностн, как и нри записи «1. Прн этом транзистор 3 открывается, и но р-базе выключает тнристор 1. Амплитуда ноложительных имнульсов, подаваемых на входные разрядные шины 9 и 10, должна быть меньше опор. В этом случае информация занисывается именно в ту ячейку памяти, на которую подан адрес. Предмет изобретения Тиристорно-транзисторная ячейка намяти, содержащая тиристор, анод которого соединен с ноложительной шиной нитання через резистор, транзистор записи «О, транзистор записи «1 и диод, отличающаяся тем, что, с целью снижения потребления энергии, р-база тиристора соединена с коллектором транзистора записи «О, п-база соединена с коллектором транзистора заннси «1 и через диод с выходной разрядной щиной, один пз катодов тиристора соединен с эмиттерами транзисторов записи «О и «1 и адресной шиной, а другой - с ноложительной шиной источника опорного нанряження, нрнчем базы транзисторов записн «О н «1 нодсоединены к соответствующим входным разрядным шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| Формирователь импульсов с удвоением напряжения | 1976 |

|

SU613492A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ | 1971 |

|

SU304705A1 |

| Адресный формирователь для интегрального постоянного запоминающего устройства | 1975 |

|

SU593250A1 |

| СТАТИЧЕСКИЙ НЕСИММЕТРИЧНЫЙ ТРИГГЕР | 1971 |

|

SU320931A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК НА ФЕРРИТ-ТРАНЗИСТОРНЫХ | 1971 |

|

SU290458A1 |

| ЭЛЕМЕНТ ПАМЯТИ12 | 1973 |

|

SU399011A1 |

| ТРАНЗИСТОРНЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1972 |

|

SU327576A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

-TL

Выход

Авторы

Даты

1973-01-01—Публикация