Изобретение относится к области автоматики и вычислительной техники.

В аппаратуре автоматики нередко необходимо такое устройство (синхронизатор импульсов, пусковое устройство), которое позволило бы получить на выходе полноценные тактовые импульсы, независимо от момента включения устройства (например, нажатие кнопки пуска, приход синхронизируемого импульса) .

Известен, например, синхронизатор импульсов, выполненный на ферротранзисторных элементах и содержащий элементы - входной, выходной, задержки и запрета.

В элементе запрета тактовых импульсов выход соединен с обмоткой запрета входного элемента, а в элементе задержки тактового импульса выход соединен с обмоткой считывания элемента запрета. Импульс с выходного элемента появится, если соблюдены условия отсутствия частичного или полного совпадения синхронизируемого и второго тактового импульсов.

Так как рассмотренный прототип собран на импульсных элементах, то в схеме, собранной на потенциальных элементах, он не пригоден.

С целью повышения помехозащищенности и надежной работы в режимах «одиночного импульса и «серии импульсов, в предлагаемом изобретении установлено четыре триггера, которые логически объединены последовательно и обратной связью логическими элементами «И, «ИЛИ, «НЕ.

При этом выполняются следующие условия:

устройство должно запускаться только в момент нажатия кнопки «Пуск или прихода синхронизирующего импульса;

независимо от момента пуска на выходе должны формироваться полноценные импульсы, совпадающие во времени с входными тактовыми импульсами;

в присутствии сигнала «Останов на выходе формируется одиночный импульс; в отсутствии сигнала «Останов на выходе формируется серия импульсов до прихода сигнала «Останов ;

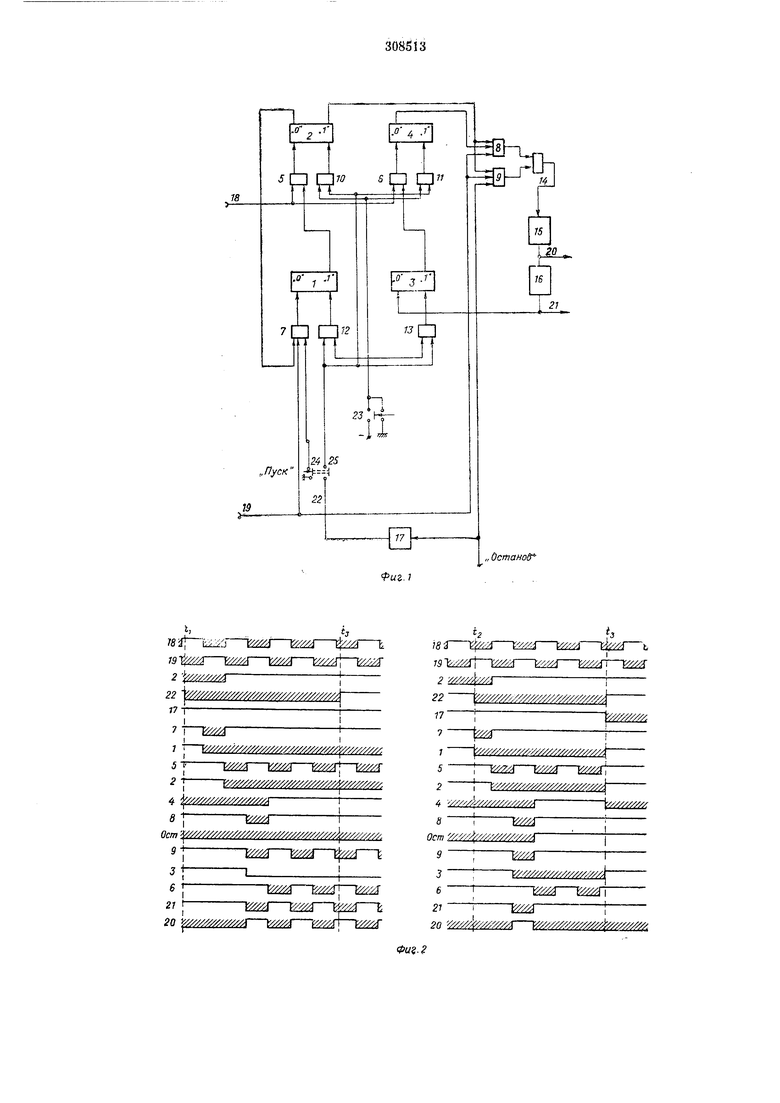

независимо от момента отпускания кнопки «Пуск работа синхронизатора не нарушается. На фиг. 1 изображена функциональная схема синхронизатора; на фиг. 2 - временная диаграмма работы синхронизатора. (Сигналы, обозначенные цифрами на временной диаграмме, в функциональной схеме соответствуют номерам соответствующих элементов схемы).

Синхронизатор тактовых импульсов с парафазным входом и выходом реализован на потенциальных элементах и содержит типовые ячейки триггеров: памяти /, ключа 2, обратной связи 3 и одиночных и.мпульсоБ 4, котоа I :ч.

рые логически включены последовательно, а также содержит логические элементы «И 5-9, «ИЛИ 10-14 и «НЕ 15-17.

Тактовые имнульсы, поступающие на входы 18, 19, проходят через синхронизатор на выходы 20 и 21 полноценными, независимо от момента нажатия кнопки «пуск (или прихода синхронизирующего импульса). Временная диаграмма подробно поясняет работу устройства при разных моментах нажатия кнопки «Пуск 22.

Ячейка памяти / запоминает приход первого импульса по выходу 18 в момент нажатия кнопки «Пуск. С приходом импульса по входу 19 включается ячейка ключа 2, которая блокирует ячейку памяти по входу, а также дает разрешение на формирование импульсов на выходах схем «И 8, 9. С приходом второго импульса по входу 18 на выходе элемента «И 8 одиночных импульсов и элемента «И 9 «серии импульсов формируются полноценные импульсы.

Одновременно ячейка обратной связи 3 изменяет свое состояние, а с приходом второго импульса по входу 19 ячейка одиночных импульсов 4 выдает запрет выходу одиночных импульсов.

С приходом следующих импульсов по входу 18 на выходе элемента «И 9 формируются импульсы, если нет сигнала «Останов.

При наличии сигнала «Останов на выходах 20 и 21 синхронизатора формируется одиночный импульс.

Сигнал «Останов изменяет свое состояние только в момент прохождения импульса по входу 19 (по условию). Триггерные ячейки 1-4 устанавливаются в первоначальное состояние при отпускании кнопки «Пуск (если присутствует сигнал «Останов) или при нажатии кнопки установки «О 23.

Моменты размыкания и замыкания контактов 24 опережают моменты размыкания или замыкания контактов 25 кнопки «Пуск 22.

Предмет изобретения

Синхронизатор импульсов, содержащий

триггеры и логические элементы «И, «ИЛР1, «НЕ, отличающийся тем, что, с целью повышения помехозащищенности и надежности работы в режимах «одиночного импульса и «серии импульсов, в нем нулевой вход первого триггера через первый элемент «И соединен с нулевым выходом второго триггера, к нулевому входу которого через второй элемент «И подключен единичный выход первого триггера, единичный выход третьего триггера через третий элемент «И соединен с нулевым входом четвертого триггера, нулевой выход которого подключен ко входу четвертого элемента «И, выход которого через схему «ИЛИ объединен с выходом пятого элемента «И и через два последовательно соединенных элемента «НЕ подключен к нулевому входу третьего триггера, причем, входы четвертого и пятого элемента «И соединены с единичным выходом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1977 |

|

SU790225A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для обучения | 1987 |

|

SU1580423A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для программного управления объектами | 1985 |

|

SU1287107A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Устройство для формирования частотно-импульсных последовательностей | 1980 |

|

SU930621A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU924840A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Устройство для синхронизации многомашинных комплексов | 1989 |

|

SU1700552A1 |

Даты

1971-01-01—Публикация