3

торов 6 по модулю два, элемент И-Н 17, элемент И 18 и элемент НЕ 19.

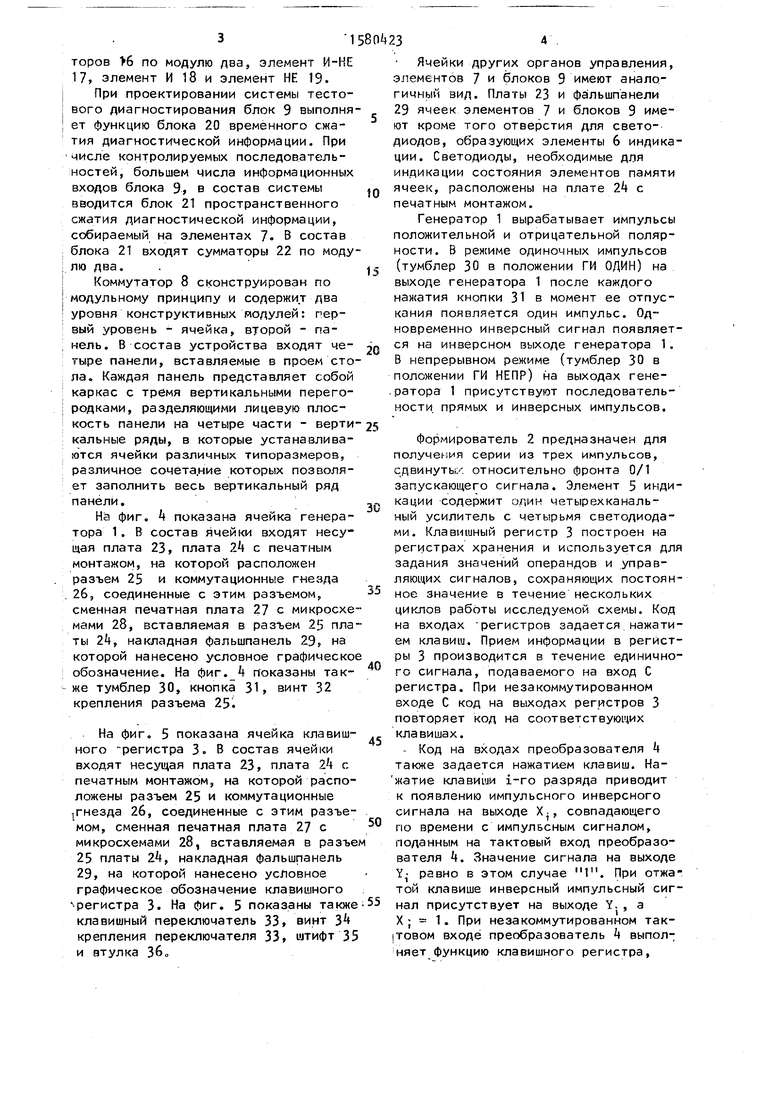

При проектировании системы тестового диагностирования блок 9 выполнет функцию блока 20 временного сжатия диагностической информации. При числе контролируемых последовательностей, большем числа информационны входов блока 9, в состав системы вводится блок 21 пространственного сжатия диагностической информации, собираемый на элементах 7« В состав блока 21 входят сумматоры 22 по мод

лю два. .

Коммутатор 8 сконструирован по модульному принципу и содержит два уровня конструктивных модулей: первый уровень - ячейка, второй - панель. В состав устройства входят че- тыре панели, вставляемые в проем стола. Каждая панель представляет собой каркас с тремя вертикальными перегородками, разделяющими лицевую плоскость панели на четыре части - вертикальные ряды, в которые устанавливаются ячейки различных типоразмеров, различное сочета.ние которых позволяет заполнить весь вертикальный ряд панели.

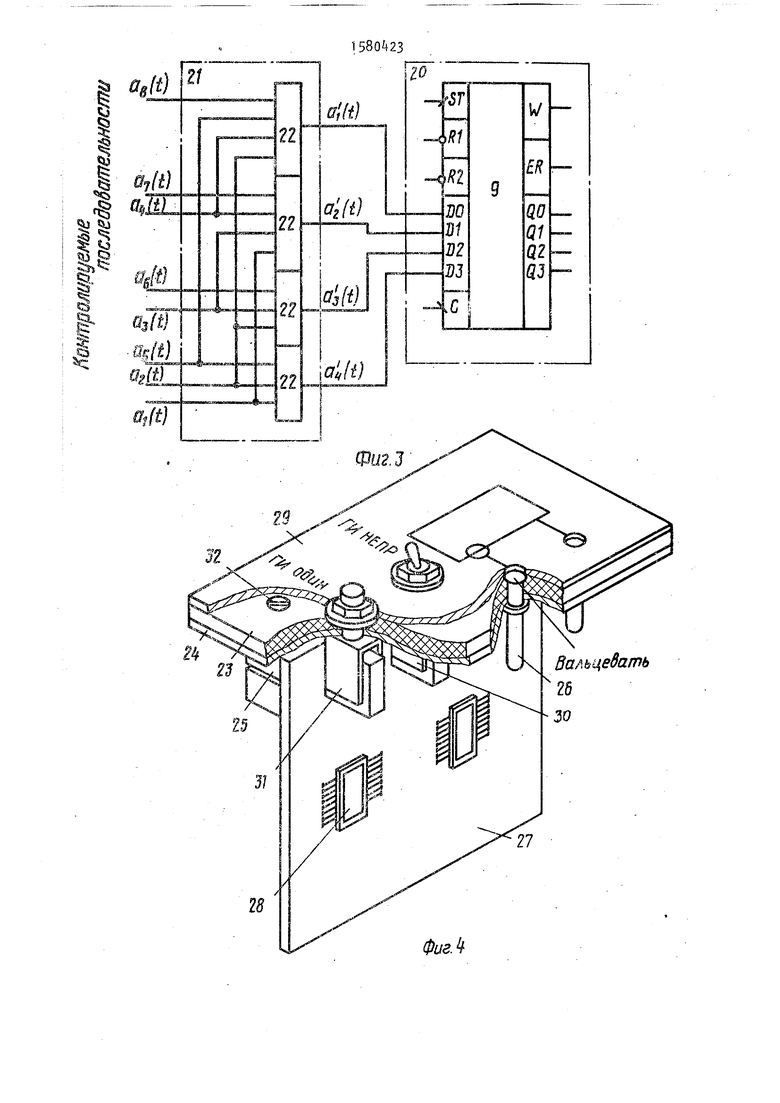

На фиг. k показана ячейка генератора 1. В состав ячейки входят несущая плата 23, плата 2k с печатным монтажом, на которой расположен разъем 25 и коммутационные гнезда 26, соединенные с этим разъемом,, сменная печатная плата 27 с микросхемами 28, вставляемая в разъем 25 платы 24, накладная фалыипанель 29, на которой нанесено условное графическое обозначение. На фиг.4 показаны также тумблер 30, кнопка 31, винт 32 крепления разъема 25.

На фиг. 5 показана ячейка клавишного -регистра 3. В состав ячейки входят несущая плата 23, плата 2k с печатным монтажом, на которой расположены разъем 25 и коммутационные

,гнезда 26, соединенные с этим разъемом, сменная печатная плата 27 с микросхемами 28, вставляемая в разъе 25 платы 2k, накладная фальшпанель 29, на которой нанесено условное графическое обозначение клавишного

регистра 3. На фиг. 5 показаны также клавишный переключатель 33, винт 3 крепления переключателя 33, штифт 35 и атулка 36°

o

5

0 5

0

5

0

45

0

5

Ячейки других органов управления, элементов 7 и блоков 9 имеют аналогичный вид. Платы 23 и фальшпанели 29 ячеек элементов 7 и блоков 9 имеют кроме того отверстия для свето- диодов, образующих элементы 6 индикации. Светодиоды, необходимые для индикации состояния элементов памяти ячеек, расположены на плате 2k с печатным монтажом.

Генератор 1 вырабатывает импульсы положительной и отрицательной полярности. В режиме одиночных импульсов (тумблер 30 в положении ГИ ОДИН) на выходе генератора 1 после каждого нажатия кнопки 31 в момент ее отпускания появляется один импульс. Одновременно инверсный сигнал появляется на инверсном выходе генератора 1. В непрерывном режиме (тумблер 30 в положении ГИ НЕПР) на выходах генератора 1 присутствуют последовательности прямых и инверсных импульсов.

Формирователь 2 предназначен для получеьия серии из трех импульсов, сдвинуть, - относительно фронта 0/1 запускающего сигнала. Элемент 5 индикации содержит один четырехканаль- ный усилитель с четырьмя светодиода- ми. Клавишный регистр 3 построен на регистрах хранения и используется для задания значений операндов и управляющих сигналов, сохраняющих постоянное значение в течение нескольких циклов работы исследуемой схемы. Код на входах регистров задается нажатием клавиш. Прием информации в регистры 3 производится в течение единичного сигнала, подаваемого на вход С регистра. При незакоммутированном входе С код на выходах регистров 3 повторяет код на соответствующих клавишах.

Код на входах преобразователя k также задается нажатием клавиш. На- жатие клавиши 1-го разряда приводит к появлению импульсного инверсного сигнала на выходе Xt, совпадающего по времени с импульсным сигналом, поданным на тактовый вход преобразователя k. Значение сигнала на выходе Y- равно в этом случае 1. При отжатой клавише инверсный импульсный сигнал присутствует на выходе Y. , a X ; 1. При незакоммутированном так- ITOBOM входе преобразователь k выполняет функцию клавишного регистра,

когда код на выходах Y повторяет код на соответствующих клавишах.

Библиотека изучаемых элементов 7 может состоять из одного элемента, например из элемента И-НЕ 3, может быть определена из личного опыта разработчика, состоять из схем, соответствующих какой-либо серии или сериям микросхем, может состоять из постоянной части, определенной каким либо способом, и переменной, зависящей от специфических свойств проектируемых устройств,, Коммутация узлов устройства на панелях производится при помощи соединительных шнуров, вставляемых в коммутационные гнезда 26 ячеек.

Устройство работает следующим образом.

На этапе подготовки к работе производится разработка логических схем исследуемого устройства и системы его тестового диагностирования. Определяется состав необходимых ячеек органов управления и излучаемых элементов 7. Путем моделирования определяется эталонный контрольный код.

Генераторы 1, формирователи 2, преобразователи А используются для построения схем синхронизации и начальной установки. При необходимости для этих же целей могут быть использованы некоторые из элементов JРегистры 3 применяются для задания значений операндов, а также управляющих сигналов, сохраняющих постоянное значение в течение нескольки циклов диагностирования исследуемой схемы.

Элементы 5 индикации служат для наблюдения за состояниями отдельных точек исследуемого устройства.

Исследуемое устройство (объект диагностирования) собирается на основе ячеек элементов 7, состояние элементов памяти которых отображается на светодиодах элементов 6.

Тестовое диагностирование предполагает подачу на объект специальных тестовых воздействий. По реакциям на них принимается решение о техническом состоянии объекта диагностирования (ОД), так как наличие неисправностей проявляется в виде искажений его выходных последовательностей. Формирователь контрольных кодов (сумматоры 16.1, 16.2, 16.3, 16.k и регистр 11) преобразует длинные дзоии8о 4;.

10

15

20

25

30

35

40

45

50

55

3«

ные последовательности, реакции ОД на входные воздействия, в четырехразрядный контрольный код, который затем сравнивается с кодовым эталоном, полученным заранее на этапе моделирования. На основе результате сравнения делается вывод о наличии или отсутствии искажений в выходных последовательностях ОД.

Основу формирователя контрольных кодов составляет генератор двоичных М-последовательностей (последовательностей максимальной длины).

Блок 9 имеет контролируемые входы, на которые подаются анализируемые последовательности, либо сигналы с выхода блока 20 (фиг. 3) вход cm- нала Пуск/Останов, определяющего интервал обработки выходных последовательностей ОД, иначе называемый Окном измерений (ОИ), вход сигнала сброса триггера 10, вход сигнала сброса триггера 15 и вход синхроимпульсов ОД. Выходами блока 9 являются выходы разрядов регистра 11 и выходы триггеров 10 и 15. На элементах б выводятся содержимое регистра 12, а также состояние триггеров 10 и 15.

Приход сигнала Пуск/Останов приводит к установке в 1 триггера 10, единичное состояние которого определяет интервал обработки анализируемых последовательностей. Переключение триггеров регистра 11 происходит по фронту 1/0 сигналов на входе С. Следующий сигнал Пуск/Останов сбрасывает в О триггер 10, прекращая тем самым процесс формирования контрольного кода. Первый после окончания интервала обработки анализируемых последовательностей импульс С в случае нестабильности контрольного кода, т.е. в случае несовпадения контрольных кодов, полученных во время двух соседних ОИ (хранящихся в регистрах 11 и 12), обеспечивает установку в 1 триггера 15 с последующим загоранием индикатора ошибки - соответствующего элемента 6. Установка в |1 триггера 15 происходит при появлении на выходе блока 14 единичного потенциала. На одну группу входов блока 14 с разрядов регистра 11 поступает код полученного контрольного кода, на другую с выходов регистра 12 - контрольный код, полученный в предыдущем ОИ. Сброс триггера 15 осуществляется сигналом по уста

71

новочному входу. По фронту 0/1 второго после окончания ОИ импульса С происходит загрузка в регистр 12 нового значения контрольного кода. В следующих четырех тактах происходит сдвиг содержимого триггеров регистра 11, таким образом через шесть тактов после окончания ОИ регистр 11 оказывается в состоянии О О О О , т.е. готов к формированию контрольного кода в следующем ОИ.

Таким образом, из описания работы 1 блока 9 видно, что установка регистра 11 в нулевое начальное состояние происходит автоматически перед началом очередного ОИ. Сброс в нулевое начальное состояние триггеров 10 и 15 происходит при подаче сигналов сброса.

Таким образом, положительный эффект от использования изобретения заключается в расширении дидактических возможностей. Предлагаемое устройство может использоваться не толь ко для обучения проектированию логических структур, но и для обучения проектированию, сборке и наладке систем тестового диагностирования сложных цифровых изделий, имеющих большое число выходов. Особенностью устройства является независимость времени диагностирования от числа одновременно контролируемых последовательностей, которая обусловливается гибкой структурой формирователя контрольных кодов, позволяющего одновременно обрабатывать произвольное число двоичных последовательностей. При любом числе контролируемых входо алгоритм формирования контрольного кода остается одним и тем же и основан на делении многочлена входных последовательностей на характеристический многочлен формирователя контрольных кодов. Указанное свойство позволяет обеспечить высокую достоверность контроля и предельно упрощает процедуру получения эталонных

контрольных кодов, что особенно важно для технических средств обучения.

Формула изобретения

Устройство для обучения, содержащее генераторы, формирователи импульс- 5 ных последовательностей, клавишные регистры и преобразователи кодов, выходы которых подключены к входам со8

ответственно первой, второй, третьей и чет Рвотой групп коммутатора, элементы индикации первой и второй групп, входы которых соединены с выходами соответственно первой и второй групп коммутатора, выходы третьей, четвертой и пятой групп которого подключены к входам формирователей импульсных последовательностей, клавишных регистров и рреобразователей кодов соответственно, а выходы шестой группы и входы пятой группы являются входами и выходами изучаемых элемен0

5

0

5

0

5

0

5

щ е е с я тем, что, с целью расширения дидактических возможностей устройства, в него введены первый и второй триггеры, элемент И, первый, второй и третий регистры, блок сравнения, сумматоры по модулю два, элемент И-НЕ и элемент НЕ, причем входы первой группы сумматоров по модулю два подключены к соответствующим выходам седьмой группы коммутатора, входы второй группы - к соответствующим выходам .первого регистра, со- ответст гсщим входам шестой группы коммутатор. первому входу блока сравнения и информационному входу второго регистра, а выходы - к соответствующим информационным входам первого регистра, V-вход которого соединен с V-входом третьего регист- па, первым входом коммутатора и единичным выходом первого триггера, первый С-вход - с первым выходом коммутатора, с первым и вторым С-входами третьего регистра и с одним входом элемента И, выход которого подключен к второму С-входу первого регистра, а другой вход - к единичному выходу третьего регистра и входу элемента НЕ, выход которого соединен с С-вхо- дом второго регистра, выходы которого подключены к второму входу блока сравнения и соответствующим входам седьмой группы коммутатора, второй вход коммутатора соединен с одним входом элемента И-HF и выходом второго триггера, второй и третий выходы - соответственно с R- и С-входами первого триггера, а четвертый выход - с другим входом элемента И-НЕ и R-вхо- дом второго триггера, S-вход которого подключен к выходу элемента И-НЕ, D-вход - к выходу блока сравнения, а С-вход - к нулевому выходу третьего регистра.

РО CvJ

ОС 1Л

ij-гпф

LI

ОС9ZqtuBgdbwog

Ј гпф

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения построению логических структур | 1986 |

|

SU1449990A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для обучения проектированию логических узлов | 1989 |

|

SU1619331A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU976469A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

Изобретение относится к техническим средствам обучения и может использоваться для обучения проектированию систем тестового диагностирования цифровых объектов. Цель изобретения - расширение дидактических возможностей устройства. Устройство содержит генераторы, формирователи импульсных последовательностей, клавишные регистры, преобразователи кодов, элементы индексации, изучаемые элементы, коммутатор, блок контроля, триггеры, регистры, блок сравнения, группу сумматоров по модулю два, элементи И-НЕ, И, НЕ. Устройство может использоваться не только для обучения проектированию логических структур, но и для обучения проектированию, сборке и наладке систем тестового диагностирования сложных цифровых изделий, имеющих большое число выходов. Особенностью устройства является независимость времени диагностирования от числа одновременно контролируемых последовательностей, которая обуславливается гибкой структурой формирователя контрольных кодов, позволяющего одновременно обрабатывать произвольное число двоичных последовательностей. 5 ил.

ег 70851

34

32

2Ъ

| Ковригин Б.Н | |||

| и др | |||

| Описание и руководство по использованию универсальной лабораторной установки по электронным вычислительным машинам | |||

| М.: МИФИ, 1982 „ ( УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ |

Авторы

Даты

1990-07-23—Публикация

1987-12-28—Подача