1

Изобретение относится к вычислительной технике и может быть использовано для технического обслуживания и ремонта цифрового оборудования и периферийных устройств ЭВМ, имеющих выход на системный интерфейс 2К (для ЭВМ типа СМ-2, СМ-2М).

Целью изобретения является сокра- щение аппаратурных затрат имитатора.

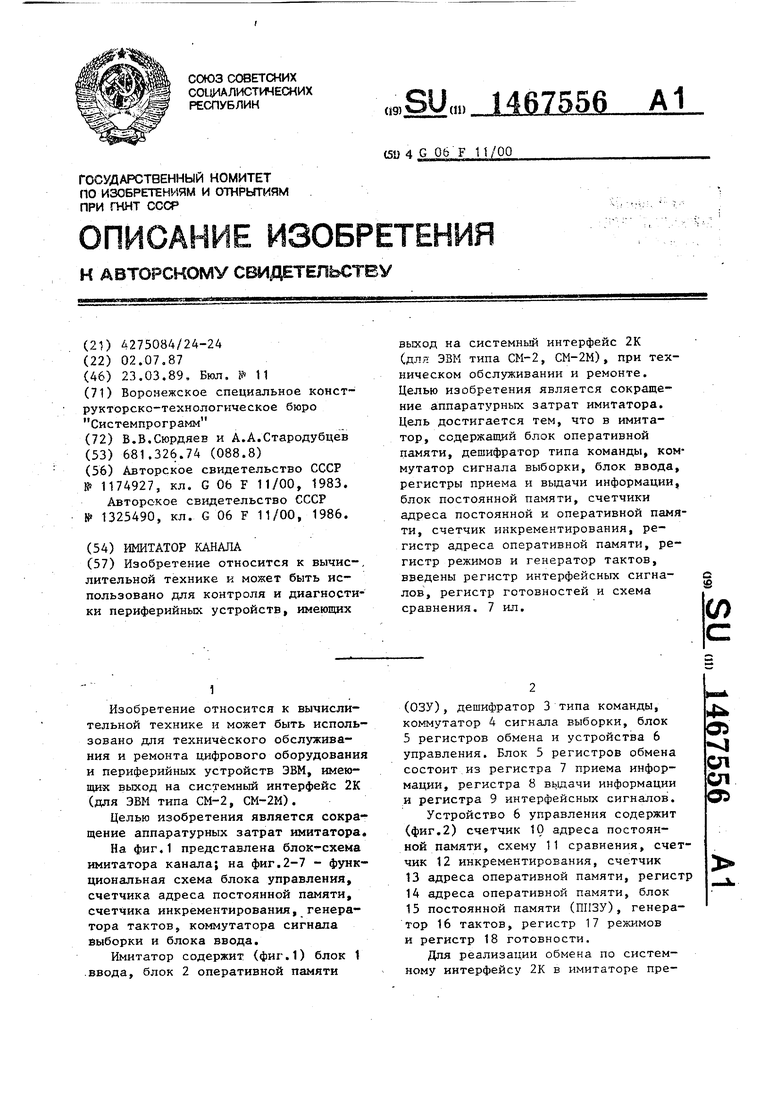

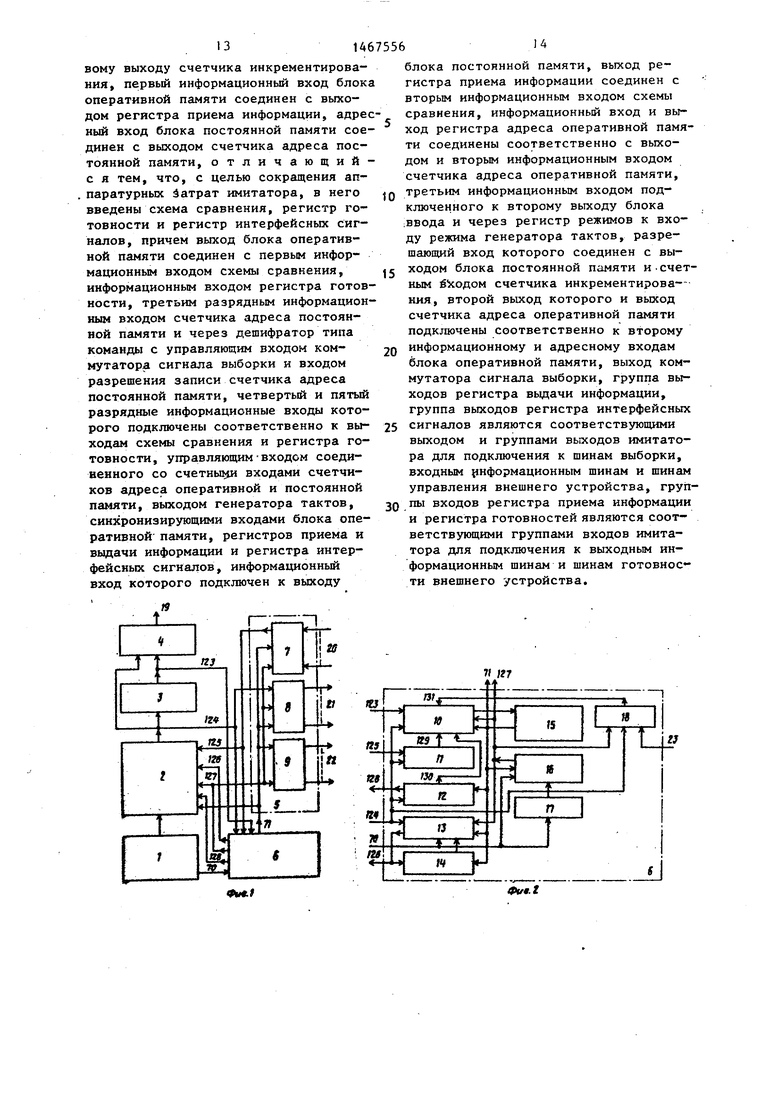

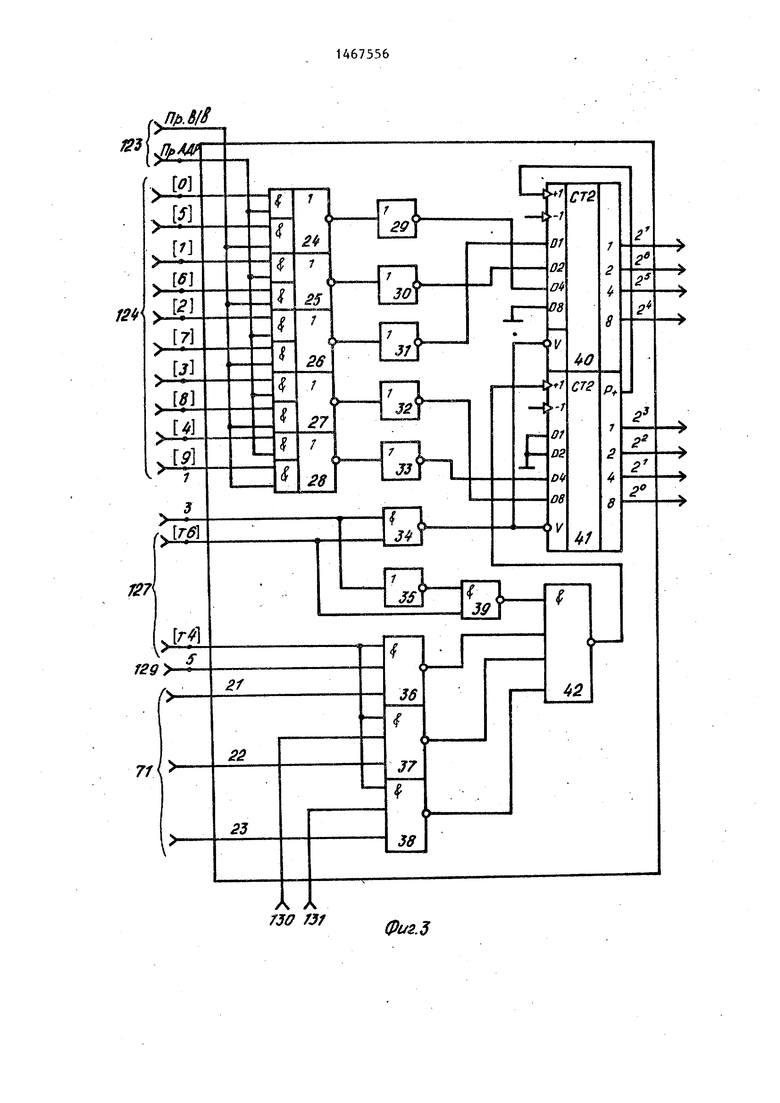

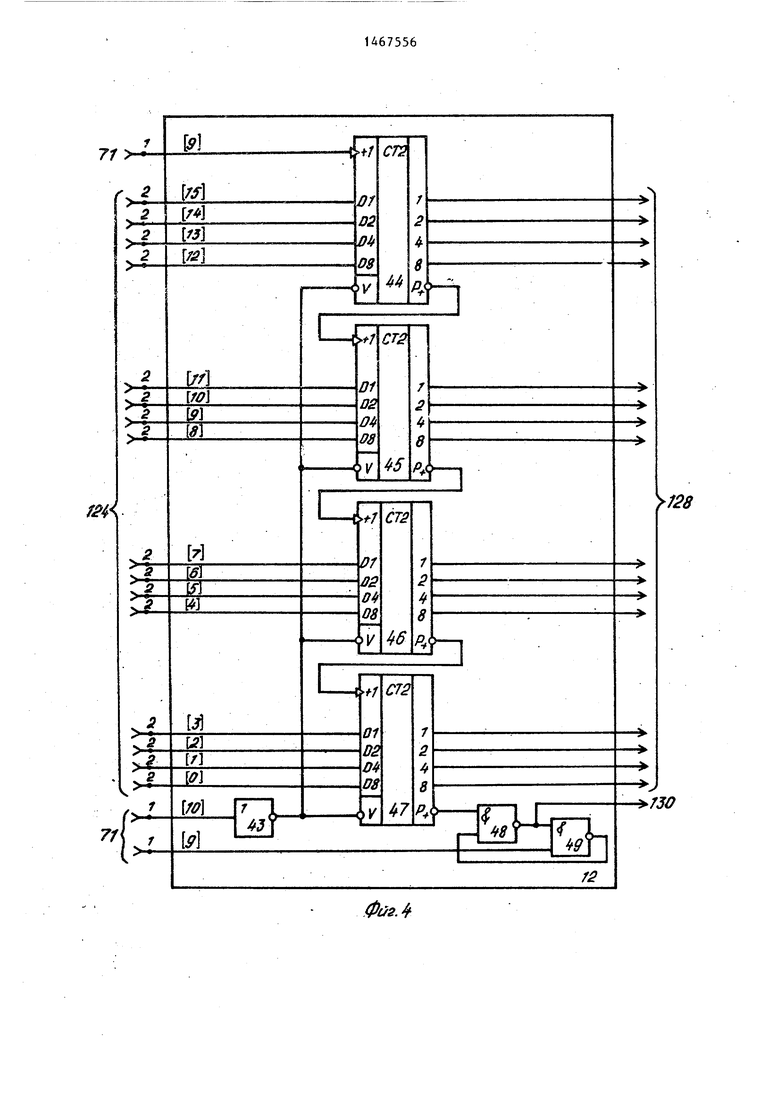

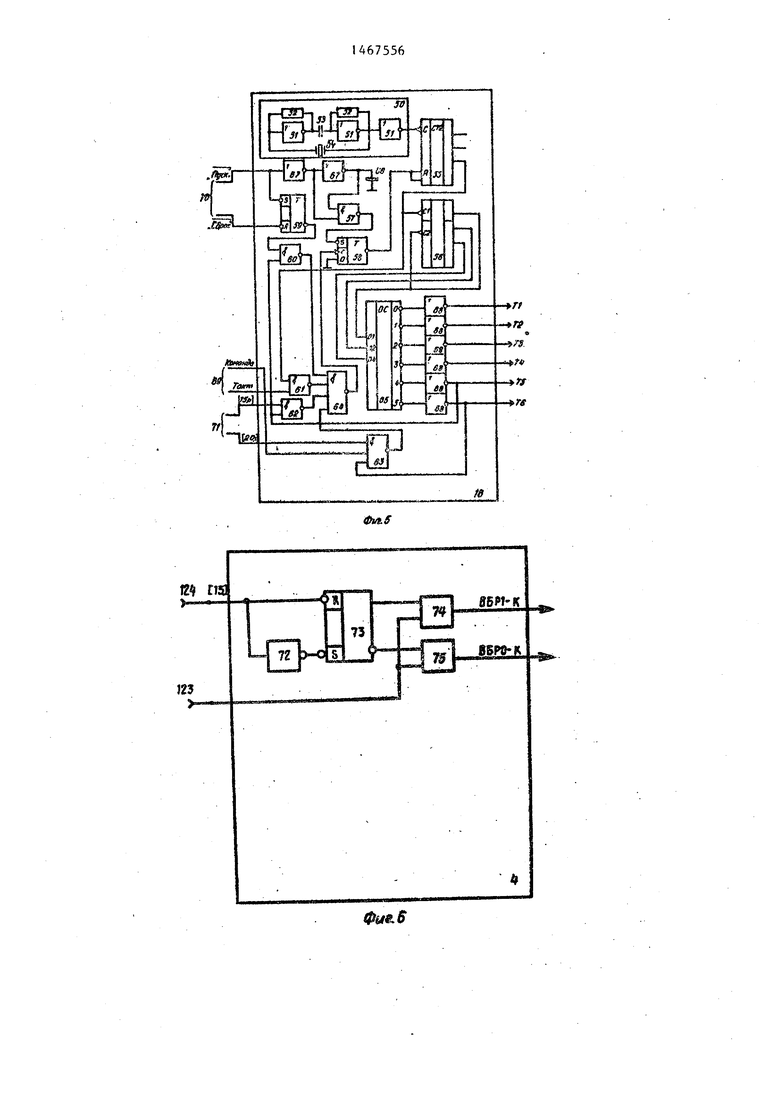

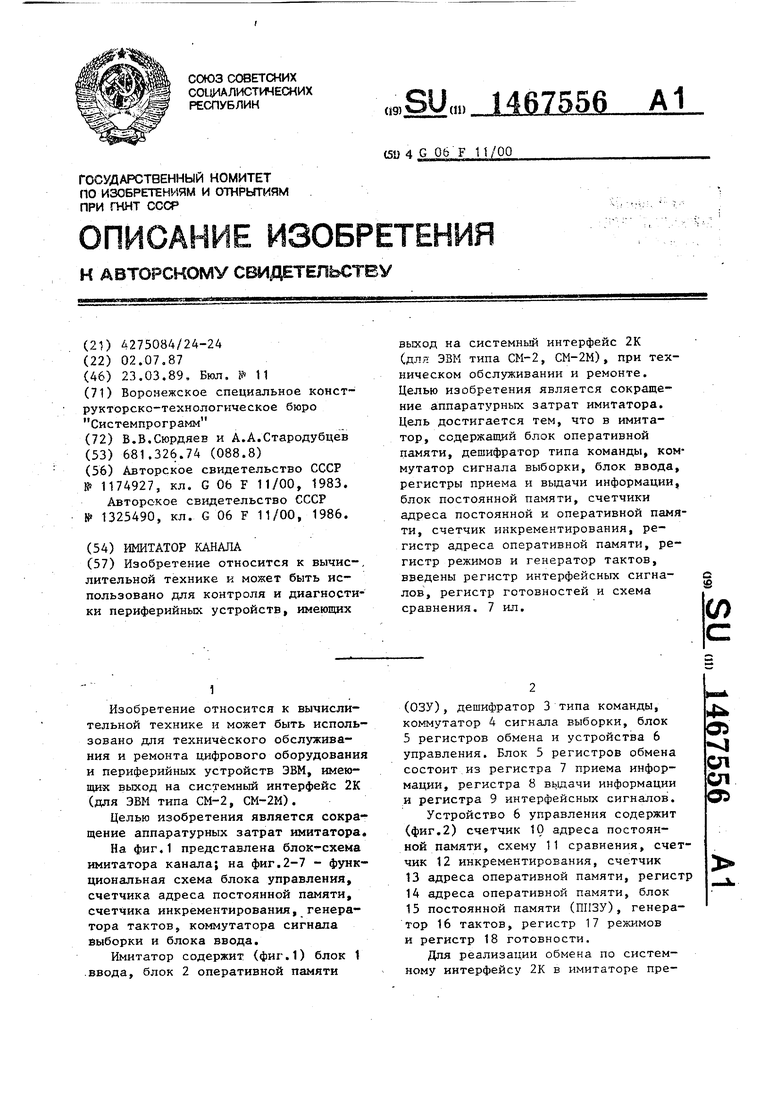

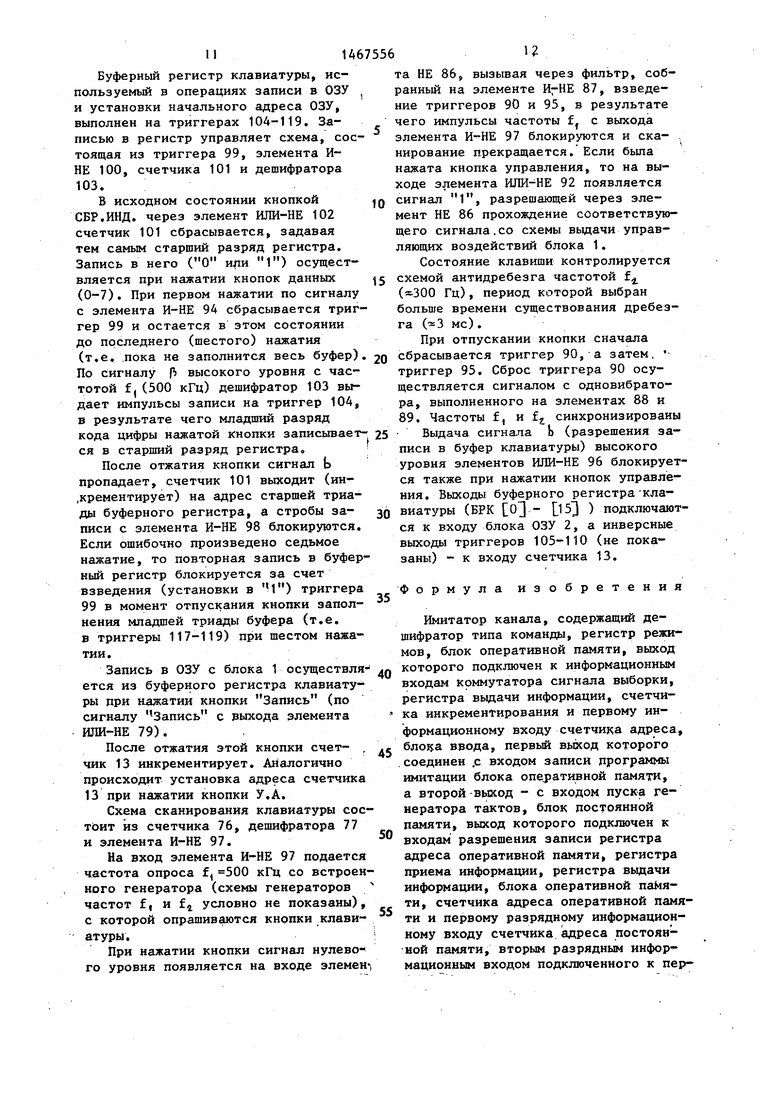

На фиг. представлена блок-схема имитатора канала; на фиг.2-7 - функциональная схема блока управления, счетчика адреса постоянной памяти, счетчика инкрементирования, генератора тактов, коммутатора сигнала выборки и блока ввода.

Имитатор содержит (фиг.1) блок 1 .ввода, блок 2 оперативной памяти

(ОЗУ), дешифратор 3 типа команды, коммутатор 4 сигнала выборки, блок 5 регистров обмена и устройства 6 управления. Блок 5 регистров обмена состоит из регистра 7 приема информации, регистра 8 вьщачи информации и регистра 9 интерфейсных сигналов. Устройство 6 управления содержит (фиг.2) счетчик 10 адреса постоянной памяти, схему 11 сравнения, счетчик 12 инкрементирования, счетчик

13адреса оперативной памяти, регистр

14адреса оперативной памяти, блок

15постоянной памяти (ПИЗУ), генератор 16 тактов, регистр 17 режимов

и регистр 18 готовности.

Для реализации обмена по системному интерфейсу 2К в имитаторе пре4

О)

р1 ел

О5

дусматриваются выводы для шин 19 выборки (ВБРО-К, ВБР1-К), шин 20 приема информации (шин 0-Т - 15-Т), шин 21 выдачи информации (шин 0-К - 15-К шин 22 интерфейсных сигналов (ВП-К, ОСТ-Кр ПСБ-К, ВД-К, ПР-К, ОСБ-К), шин 23 готовности (ГТО-Т, ГТ1-Т). Данные программы (команды операнды, константы) записываются в блок 2 (имеющего организацию 64x16 разрядов), начиная с ячейки, адресуемой счетчиком 13 Установка адреса ОЗУ в счетчик 13 осуществляется из блока 1,

Блок 3 дешифрирует выставляемое на выходе блока 2 слово по признаку типа команды (ввода-вывода или адресной) , управляет записью разрядов кода операции команд в счетчик 10 и разрешает работу коммутатора 4 по признаку команды ввода-вывода.

Прием информации от внешнего устройства по шинам 0-Т - 15-Т и хранения ее осуществляются в регистре 7, выдача содержимого ячейки блока 2 во внешнее устройство по шинам 0-К - 15-К производится через регистр 8, а формирование управляющих потенциалов .- по шинам 22 (ВП-К-, ОСТ-К, ПСБ-К, ВД-К, ПР-К, ОСБ-К) регистром 9,

Устройство 6 обеспечивает работу имитатора по принципу микропрограммного управления, организует процедуру ввода-вывода и логическую обработку вводимой информации по программе, составленной на основе принятого перечня командs команд ввода-вывода (с выдачей сигнала ВП-К и без него) и адресных команд, необходимых и достаточных для составления программы, позволяющей произвести полноценную проверку внешнего устройства по системному интерфейсу 2К

Счетчик 10 устанавливает адрес слова ППЗУ с требуемой совокупность микрокоманд.

Счетчик 12 формирует сигнал для инкрементирования счетчика 10 по условию переполнения М н- 1, где М - содержимое слова блока 2.

Счетчик 13 определяет адреса сло ва ОЗУ, по которому вводится или выводится информация.

Регистр 14 обеспечивает хранение адреса ОЗУ адресной команды программы.

Блок 15 обеспечивает хранение микрокоманд и условий для команд с анализом условий.

Генератор 16 генерирует последовательность из шести тактов, необходимых для временной привязки всех микроопераций устройства.

Регистр 17 режимов работы задает один из трех режимов работы устройства: автоматический, полуавтоматический или ручной.

Регистр 18 готовности фиксирует наличие действующих потенциалов на 5 шинах 23 готовности ГТО-Т, ГП-Т и разрешает при их наличии инкременти- рование счетчика 10.

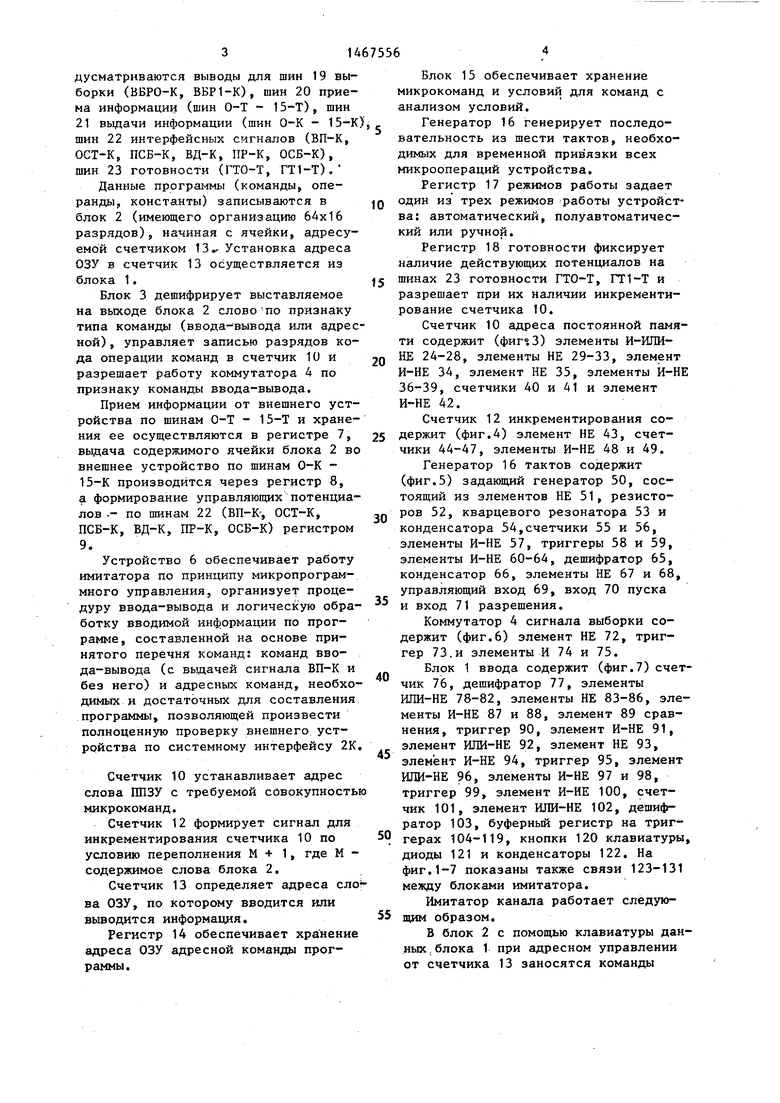

Счетчик 10 адреса постоянной памяти содержит () элементы И-ИЛИ- 0 НЕ 24-28, элементы НЕ 29-33, элемент И-НЕ 34, элемент НЕ 35, элементы Й-НЕ 36-39, счетчики 40 и 41 и элемент 42.

Счетчик 12 инкрементирования со- 5 держит (фиг.4) элемент НЕ 43, счетчики 44-47, элементы И-НЕ 48 и 49.

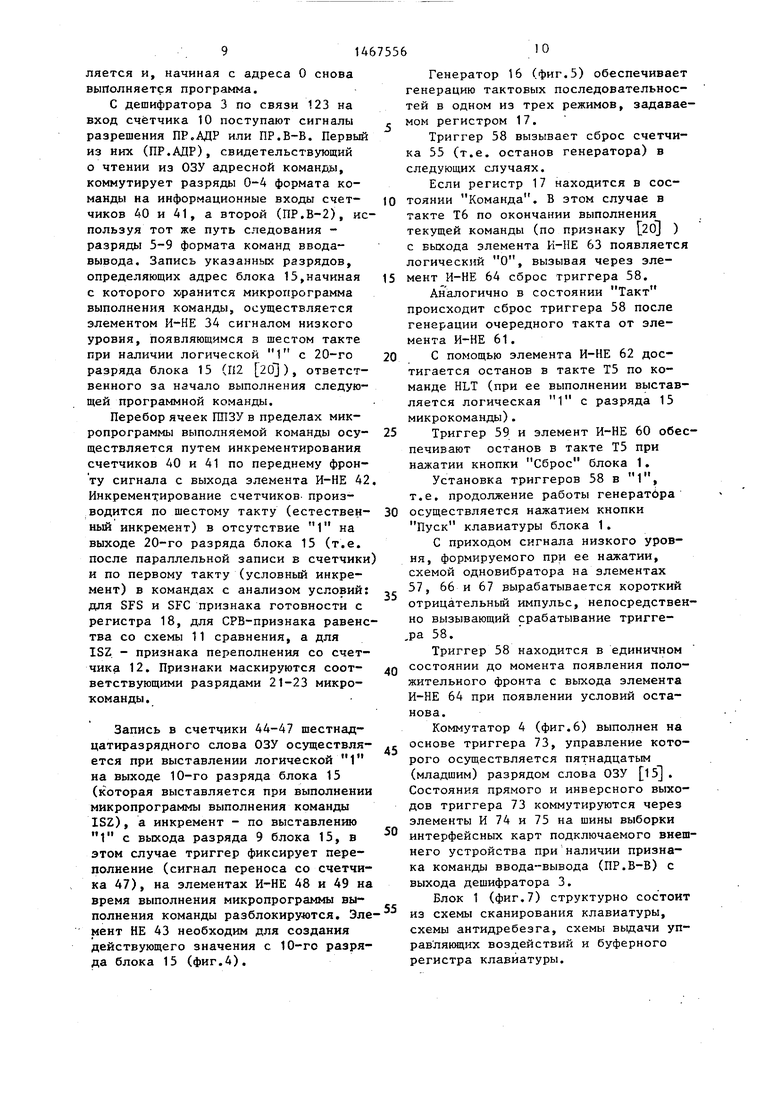

Генератор 16 тактов содержит (фиг.5) задающий генератор 50, состоящий из элементов НЕ 51, резисторов 52, кварцевого резонатора 53 и конденсатора 54,счетчики 55 и 56, элементы И-НЕ 57, триггеры 58 и 59, элементы И-НЕ 60-64, дешифратор 65, конденсатор 66, элементы НЕ 67 и 68, управляющий вход 69, вход 70 пуска и вход 71 разрешения.

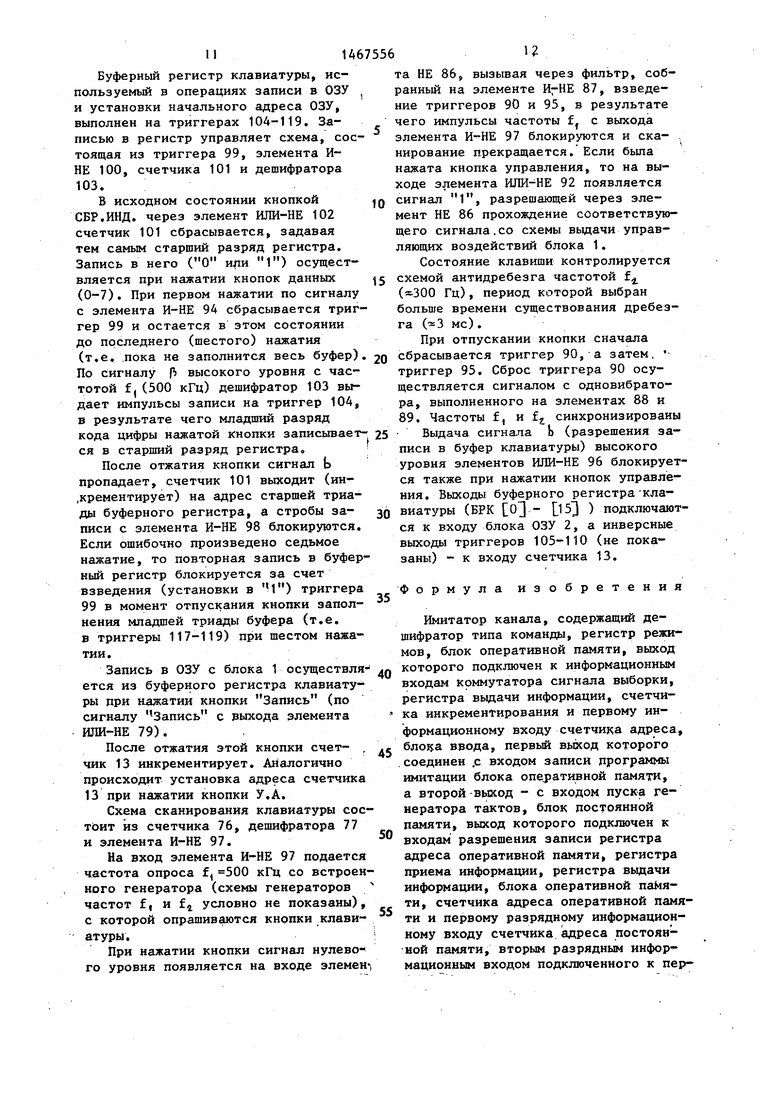

Коммутатор 4 сигнала выборки содержит (фиг.6) элемент НЕ 72, триггер 73.и элементы И 74 и 75.

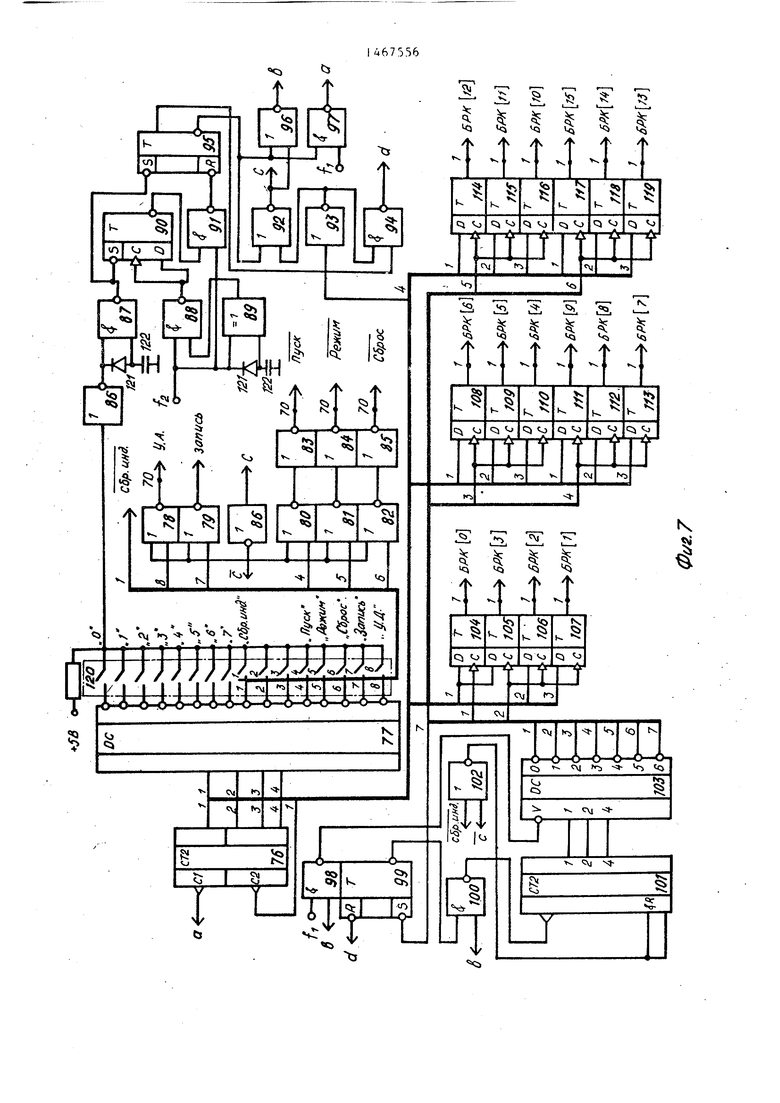

Блок 1 ввода содержит (фиг.7) счетчик 76, дешифратор 77, элементы ИЛИ-НЕ 78-82, элементы НЕ 83-86, элементы И-НЕ 87 и 88, элемент 89 сравнения, триггер 90, элемент И-НЕ 91, элемент ИЛИ-НЕ 92, элемент НЕ 93, элемент И-НЕ 94, триггер 95, элемент ИЛИ-НЕ 96, элементы И-НЕ 97 и 98, триггер 99, элемент И-НЕ 100, счетчик 101, элемент ИЛИ-НЕ 102, дешифратор 103, буферный регистр на триггерах 104-119, кнопки 120 клавиатуры, диоды 121 и конденсаторы 122. На фиг.1-7 показаны также связи 123-131 между блоками имитатора.

Имитатор канала работает следую- 5 щим образом,

В блок 2 с помощью клавиатуры данных блока 1 при адресном управлении от счетчика 13 заносятся команды

0

5

0

5

50

514

(из принятого перечня команд) и данные программы. Интерфейсньй блок контролируемого внешнего устройства подключается к выводам 19-23 устройства.

При нажатии кнопки Пуск клавиатуры управления блока t включается генератор 16, обеспечивающий, начиная с пятого такта, временную последовательность тактов и выполнение nporpat-iMbi,начиная с команды, адресуемой счетчиком 13.

Блок 3 анализирует шестнадцатиразрядное слово ОЗУ (О - старший, 15 - младший разряды слова) на признак типа команды по разрядам 0-5 и разрешает запись разрядов 0-4 блока 2 (в случае адресных команд) или разрядов 5-9 (в случае команд ввода- вывода) в пять старших разрядов семиразрядного счетчика 10 (два младших разряда счетчика 10 в этой операции обнуляются). Запись указанных разрядов в счетчик 10 производит установку блока 15 по адресу, начиная с которого, в объеме четырех соседних ячеек ППЗУ хранится совокупность и последовательность микрокоманд дл я выбираемой из ОЗУ команды

Адресация в пределах области хранения микрокоманд программной коман- . ды осуществляется двумя младшими разрядами счетчика 10.

Наличие логической 1 на выходе блока 15 в разрядах 0-16 двадцати- четьфехразрядного слова означает наличие соответствующей микрокоманды каждая из которых выполняет конкретную операцию в имитаторе.

Наличие 1 в разрядах 21-23 микрокоманды, подключенных к входу счетчика 10, означает разрешение анализа условий ветвления программы при выполнении определенных команд. При выполнении этих условий на первом такте счетчик 10 инкрементирует и, следовательно, уходит с адреса слова ППЗУ, где хранятся микрокоманды на случай невыполнения этого условия В командах SFC и.. SFS анализируется наличие сигнала готовности (ГТ-0 или ГТ-1) из регистра 18 готовности, В команде СРВ анализируется признак равенства слова ОЗУ с содержимым регистра 7 со схемы 11 сравнения, В команде I SZ анализируется признак переполнения счетчика 12.

Инкрементирование счетчика 10 при

5

о

названных ус- при наличии на

генератора 16.

0

5

вьтолнении одного из ловий осуществляется входе такта с выхода

Для остальных команд из принятого перечня разряды 21-23 не программируются.

Команды выполняются циклами, цикл работы устройства равен шести так- та4М, последовательность которых генерируется с выхода шестиразрядного дешифратора 65.

Выполнение программной команды длится не более четырех циклов, поэтому -старшие пять разрядов счетчика 10 на время ее выполнения не изменяются, а смена совокупностей микрокоманд от цикла к циклу достигается перебором его двух младших разрядов. В тактах 2-5 выполняются микрооперации, предусмотренные программной командой, в шестом такте счетчик 10 по входу инкрементирует (в первом такте он может инкрементировать дополнительно только в командах с условием) , переходит на следующий адрес и т.д. Последовательность процедур в пределах цикла определяется, номером такта.

В последнем (из 4) машинном цикле на выходе двадцатого разряда блока 15 выставляется 1, поступающая на вход счетчика 10 и обеспечивающая в шестом такте запись нового адреса, в результате чего инициируется выполнение следующей программной команды .

Коммутатор 4 (фиг.6) выдает уп- 0 равляющие потенциалы по одному из выводов ВБРО-К, ВБР1-К (для выбора соответствующей кар ты интерфейсного блока подключаемого периферийного устройства) по признаку команды вво- g да-вывода на время ее выполнения. Если разряд 15 блока 2 содержит О, то управляющий потенциал будет на шине ВБРО-К, если 1 - то на шине ВБР1-К.

Блок 5 осуществляет прием шестнадцатиразрядного слова с шин 0-Т- 15-Т от внешнего устройства при выполнении команды LIB (по микрокоманде нулевого разряда блока 15) в регистр 7 приема, выдачу на шины 0-К- 15К шестнадцатиразрядного слова из ОЗУ через регистр 8 выдачи по команде ОТА (выставляется микрокоманда первого разряда блока 15), формирует

5

0

5

1467556

интерфейсные сигналы ВП-К, ОСТ-К, ПСБ-К, ВД-К, ПР-К, ОСБ-К шестиразрядным регистром 9 (по микрокомандам второго-седьмого разрядов блока 15) при выполнении команд ввода- вывода. Временная привязка формирования интерфейсных сигналов регистром 9, приема и выдачи информации регистрами 8 и 7 осуществляется генератором 16. Запись в блок 2 также синхронизируется генератором 16.

По команде STB содержимое регистра 7 заносится в ячейку, адресуемую счетчиком 13 микрокомандой с восьмого разряда блока 15,

Схема 11 сравнения работает всег да, в отличие от счетчща 12, кото- рьй инкрементирует содержимое ячейки блока 2 девятым разрядом микрокоманды (при выполнении команды ISZ), Измененное содержимое ячейки блока 2 при наличии- десятого разряда микрокоманды заносится в блок 2 по тому же адресу, по какому происходило считывание при выполнении команды. Запись в тпестиразрядный счетчик 13 осуществляется при выполнении адресных команд Счетчик 13 в процедурах выполнения этих команд принимает значения адресов перехода или обращений, содержащихся в шести младших разрядах слова ОЗУ выполняемой KOMaiJ ды при наличии микрокома.нды разряда 11 блока 15,

Для хранения адреса слова ОЗУ выполняемой команды используется регистр 14, запись в который происходит с выхода счетчика 13 в момент обращения в блок 2 за следующей командой программы. Запись осуществляется с появлением логической 1 с выхода двенадцатого разряда блока 15

После обращений ,к ячейкам ОЗУ в процессе выполнения адресных команд адрес вьтолняемой команды переписывается из регистра 14 в счетчик 13 под управлением тринадцатого разряд микрокоманды.

При наличии логической 1 в четырнадцатом разряде микрокоманды в четвертом такте происходит инкремен тирование счетчика 13, благодаря че му обеспечивается выход на адрес слдующей команды программы.

Регистр 17 режимов работы трех- разрядный, сдвиговый, включенный по кольцевой схеме. Поочередная устанока 1 на его выходах осуществляетс

0

5

0

8,

с каждым нажатием соответствующей кнопки клавиатуры управления блока 1, Исходное состояние регистра - наличие 1 в первом разряде - соответствует автоматическому выполнению программы, в котором возможен останов генератора 16 только при выходе в программе на команду останова. Признаком останова генератора 16 в пятом такте в этом случае являе тся появление логической 1 с пятнадцатого разряда микрокоманды.

Наличие 1 во втором разряде регистра 17 соответствует полуавтоматическому режиму работы, который заключается в тон, что останов генератора 16 на пятом такте происходит по окончании выполнения очередной команды программы (при наличии лог11- ческой 1 с выхода двадцатого разряда микрокоманды),

Наличие 1 в третьем разряде регистра 17 соответствует ручному 5 режиму работы имитатора. Останов генератора 16 происходит в каждом такте цикла.

В любом случае продолжение работы устройства в выбранном режиме может быть продолжено при нажатии пусковой кнопки, сигнал с которой поступает на вход пуска генератора 16.

В двухразрядный регистр 18 готовности осуществляется запись состояний шин ГТ-0, ГТ-1 от внешнего устройства для последующего программного анализа (при выполнении команд SFC, SFS), причем при нулевом значении 15-го разряда этих команд проводится запись состояния шины ГТ-0 в первый, разряд, а при единичном значении - во второй. Запись осуществля0

5

0

5

ется при появлении логической 1 в шестнадцатом разряде микрокоманде.

Нулевое содержимое ячейки ОЗУ при обращении счетчиком 13 за командой соответствует пустой команде NOP, которая йожет использоваться как временная задержка в программе. Если программа не использует весь объем ОЗУ и не содержит команды програм- -много останова или в программе отсутствуют циклы ожидания и возврата, то по окончании программы счетчик 13 последовательно инкрементирует в каждом четвертом такте (при наличии логической 1 в четырнадцатом разряде микрокоманды), после состояния 77 (в восьмерочном коде) o6Hv0

ляется и, начиная с адреса О снова выполняется программа.

С дешифратора 3 по связи 123 на вход счётчика 10 поступают сигналы разрешения ПР.АДР или ПР.В-В. Первьй из них (ПР.АДР), свидетельствующий о чтении из ОЗУ адресной команды, коммутирует разряды 0-4 формата команды на информационные входы счетчиков 40 и 41, а второй (ПР.В-2), используя тот же путь следования - разряды 5-9 формата команд ввода- вывода. Запись указанных разрядов, определяющих адрес блока 15,начиная с которого хранится микропрограмма выполнения команды, осуществляется элементом И-НЕ 34 сигналом низкого уровня, появляющимся в шестом такте при наличии логической 1 с 20-го разряда блока 15 (П2 2d), ответственного за начало выполнения следующей программной команды.

Перебор ячеек ППЗУ в пределах микропрограммы выполняемой команды осуществляется путем инкрементирования счетчиков 40 и 41 по переднему фронту сигнала с выхода элемента И-НЕ 42 Инкрементирование счетчиков производится по шестому такту (естественный инкремент) в отсутствие 1 на выходе 20-го разряда блока 15 (т.е. после параллельной записи в счетчики и по первому такту (условный инкремент) в командах с анализом условий; для SFS и SFC признака готовности с регистра 18, для СРВ-признака равенства со схемы 11 сравнения, а для ISZ - признака переполнения со счетчика 12. Признаки маскируются соответствующими разрядами 21-23 микрокоманды .

Запись в счетчики 44-47 шестнадцатиразрядного слова ОЗУ осуществляется при выставлении логической 1 на выходе 10-го разряда блока 15 (которая выставляется при выполнении микропрограммы выполнения команды ISZ), а инкремент - по выставлению 1 с выхода разряда 9 блока 15, в этом случае триггер фиксирует переполнение (сигнал переноса со счетчика 47), на элементах И-НЕ 48 и 49 на время выполнения микропрограммы выполнения команды разблокируется. Элемент НЕ 43 необходим для создания действующего значения с 10-го разряда блока 15 (фиг.4).

5

0

Генератор 16 (фиг.5) обеспечивает генерацию тактовых последовательностей в одном из трех режимов, задавае-

мои регистром 17.

Триггер 58 вызывает сброс счетчика 55 (т.е. останов генератора) в следующих случаях.

Если регистр 17 находится в состоянии Команда. В этом случае в такте Т6 по окончании выполнения текущей команды (по признаку 20 ) с выхода элемента К-НЕ 63 появляется логический О, вызывая через эле5 мент И-НЕ 64 сброс триггера 58.

Ан алогично в состоянии Такт происходит сброс триггера 58 после генерации очередного такта от элемента И-НЕ 61.

0 С помощью элемента И-НЕ 62 достигается останов в такте Т5 по команде HLT (при ее выполнении выставляется логическая 1 с разряда 15 микрокоманды).

5 Триггер 59 и элемент И-НЕ 60 обеспечивают останов в такте Т5 при нажатии кнопки Сброс блока 1.

Установка триггеров 58 в 1 , т.е. продолжение работы генератбра

0 осуществляется нажатием кнопки Пуск клавиатуры блока 1.

С приходом сигнала низкого уровня, формируемого при ее Нс1жатии, схемой одновибратора на элементах 57, 66 и 67 вырабатывается короткий отрицательный импульс, непосредственно вызывающий срабатывание тригге- ,ра 58.

Триггер 58 находится в единичном состоянии до момента появления положительного фронта с выхода элемента И-НЕ 64 при появлении условий останова.

Коммутатор 4 (фиг.6) выполнен на основе триггера 73, управление которого осуществляется пятнадцатым (младшим) разрядом слова ОЗУ 15 . Состояния прямого и инверсного выходов триггера 73 коммутируются через элементы И 74 и 75 на шины выборки интерфейсных карт подключаемого внешнего устройства при наличии признака команды ввода-вывода (ПР.В-В) с выхода дешифратора 3.

Блок 1 (фиг.7) структурно сос тоит из схемы сканирования клавиатуры, схемы антидребезга, схемы вьщачи уп- рав ляющих воздействий и буферного регистра клавиатуры.

5

0

111А67

Буферный регистр клавиатуры, используемый в операциях записи в ОЗУ , и установки начального адреса ОЗУ, выполнен на триггерах 104-119. Записью в регистр управляет схема, состоящая из триггера 99, элемента И- НЕ 100, счетчика 101 и дешифратора 103.

В исходном состоянии кнопкой СВР.ИНД. через элемент ИЛИ-НЕ 102 счетчик 101 сбрасывается, задавая тем самым старший разряд регистра. Запись в него (О или 1) осуществляется при нажатии кнопок данных (0-7). При первом нажатии по сигналу с элемента И-НЕ 9Л сбрасывается триггер 99 и остается в этом состоянии до последнего (шестого) нажатия (т.е. пока не заполнится весь буфер). По сигналу f} высокого уровня с час

тотой f,(500 кГц) дешифратор 103 выдает импульсы записи на триггер 104, в результате чего младший разряд кода цифры нажатой кнопки записывает- ся в старший разряд регистра,

После отжатия кнопки сигнал Ь пропадает, счетчик 101 выходит (ин- .кренентирует) на адрес старшей триады буферного регистра, а стробы записи с элемента И-НЕ 98 блокируются. Если ошибочно произведено седьмое нажатие, то повторная запись в буферный регистр блокируется за счет взведения (установки в 1) триггера 99 в момент отпускания кнопки заполнения младшей триады буфера (т.е. в триггеры 117-119) при шестом нажатии.

Запись в ОЗУ с блока 1 осуществля ется из буферного регистра клавиатуры при нажатии кнопки Запись (по сигналу Запись с эыхода элемента ИЛИ-НЕ 79).

После отжатия этой кнопки счет- . чик 13 инкремеитирует. Аналогично происходит установка адреса счетчика 13 при нажатии кнопки У.А.

Схема сканирования клавиатуры состоит из счетчика 76, дешифратора 77 и элемента И-НЕ 97.

На вход элемента И-НЕ 97 подается

частота опроса f 500 кГц со встроенного генератора (схемы генераторов частот f, и 4 условно не показаны), с которой опрашиваются кнопки клавиатуры.

При нажатии кнопки сигнал нулевого уровня появляется на входе элемен

0

та НЕ 86, вызывая через фильтр, собранный на элементе К-НЕ 87, взведение триггеров 90 и 95, в результате чего импульсы частоты f с выхода элемента И-НЕ 97 блокируются и сканирование прекращается. Если была нажата кнопка управления, то на выходе элемента ИЛИ-НЕ 92 появляется сигнал 1, разрешающей через элемент НЕ 86 прохождение соответствующего сигнала.со схемы вьщачи управляющих воздействий блока 1.

Состояние клавиши контролируется 5 схемой антидребезга частотой f

20

25

( Гц), период которой выбран больше времени существования дребезга (3 мс) .

При отпускании кнопки сначала сбрасывается триггер 90, а затем. триггер 95. Сброс триггера 90 осуществляется сигналом с одновибрато- ра, выполненного на элементах 88 и 89. Частоты f, и ., синхронизированы

Бьщача сигнапа Ь (разрешения записи в буфер клавиатуры) высокого уровня элементов ИЛИ-НЕ 96 блокируется также при нажатии кнопок управления. Выходы буферного регистра кла- 30 виатуры (БРК оТ ) подключаются к входу блока ОЗУ 2, а инверсные выходы триггеров 105-110 (не показаны) - к входу счетчика 13.

формула изобретения

0

Имитатор канала, содержащий дешифратор типа команды, регистр режимов, блок оперативной памяти, выход которого подключен к информационным входам коммутатора сигнала выборки, регистра вьщачи информации, счетчи- ка инкрементирования и первому информационному входу счетчика адреса, , блоиа ввода, первый вьпсод которого соединен .с входом записи программы имитации блока опе.ративной памяти, а второй выход - с входом пуска генератора тактов, блок постоянной памяти, выход которого подключен к входам разрешения записи регистра адреса оперативной памяти, регистра приема информации, регистра вьщачи информации, блока оперативной паМя- ти, счетчика адреса оперативной памяти и первому разрядному информационному входу счетчика адреса постоянной памяти, вторым разрядным информационным входом подключенного к пер5

W К7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012035C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

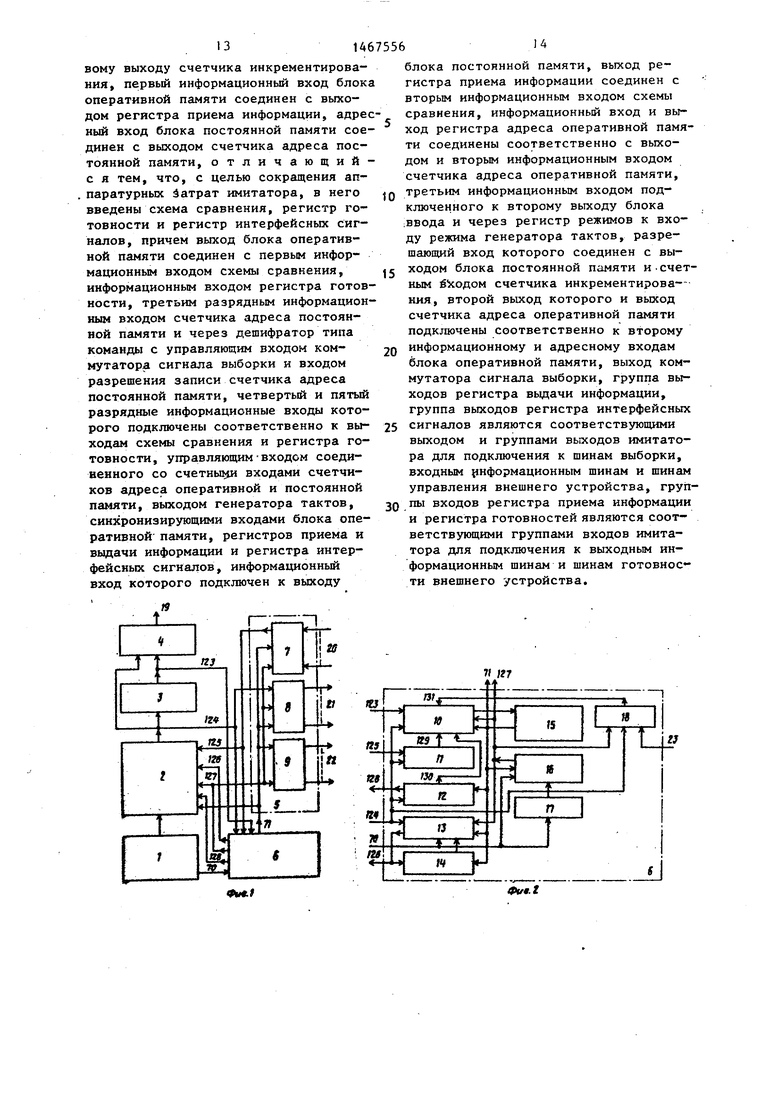

Изобретение относится к вычис-, лительной технике и может быть использовано для контроля и диагностики периферийных устройств, имеющих выход на системный интерфейс 2К (для ЭВМ типа СМ-2, СМ-2М), при техническом обслуживании и ремонте. Целью изобретения является сокращение аппаратурных затрат имитатора. Цель достигается тем, что в имитатор, содержащий блок оперативной памяти, дешифратор типа команды, коммутатор сигнала выборки, блок ввода, регистры приема и вьщачи информации, блок постоянной памяти, счетчики адреса постоянной и оперативной памяти, счетчик инкрементирования, регистр адреса оперативной памяти, регистр режимов и генератор тактов, введены регистр интерфейсных сигналов, регистр готовностей и схема сравнения. 7 ил. с (Л

.Z

730 Ш

Фи2.

.

(

W CIS

72

b-0

123

g6P1-K

eiroHL

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-23—Публикация

1987-07-02—Подача