Предлагаемое устройство относится к области автоматики и вычислительной техники, в частности линейному преобразованию сигналов во времяиэдпульсной форме.

Известны усилители различных электрических величин (напряжения, тока, мощности, частоты импульсов и т. д.), а преобразователи этих величин в интервалы времени и о-братно, содержащие генератор импульсов и делитель частоты, подключенные через ключи к реверсивному счетчику, логические элементы «И, «ИЛИ, :«НЕ, элемент задержки и формирователь, позволяющие реализовать усиление сигнала, заданного интервалом време ни, путем преобразования его, например в «апряжение, с последующим усилением при помощи усилителя напряжения и обратным преобразованием усиленного сигнала в интервал времени. Однако схемы, реализующие эту последовательность действий, громоздки, имеют ведостаточ1ную точность и невысокий коэффициент с узким диапазоном регулирования, .нестабильны из-за наличия большого числа аналоговых элементов,, подверженных дрейфу, чувствительны « различным помехам, а также вносят запаздывание выходного сигнала относительно входного и не позволяют одновременно получать результат в цифровой форме.

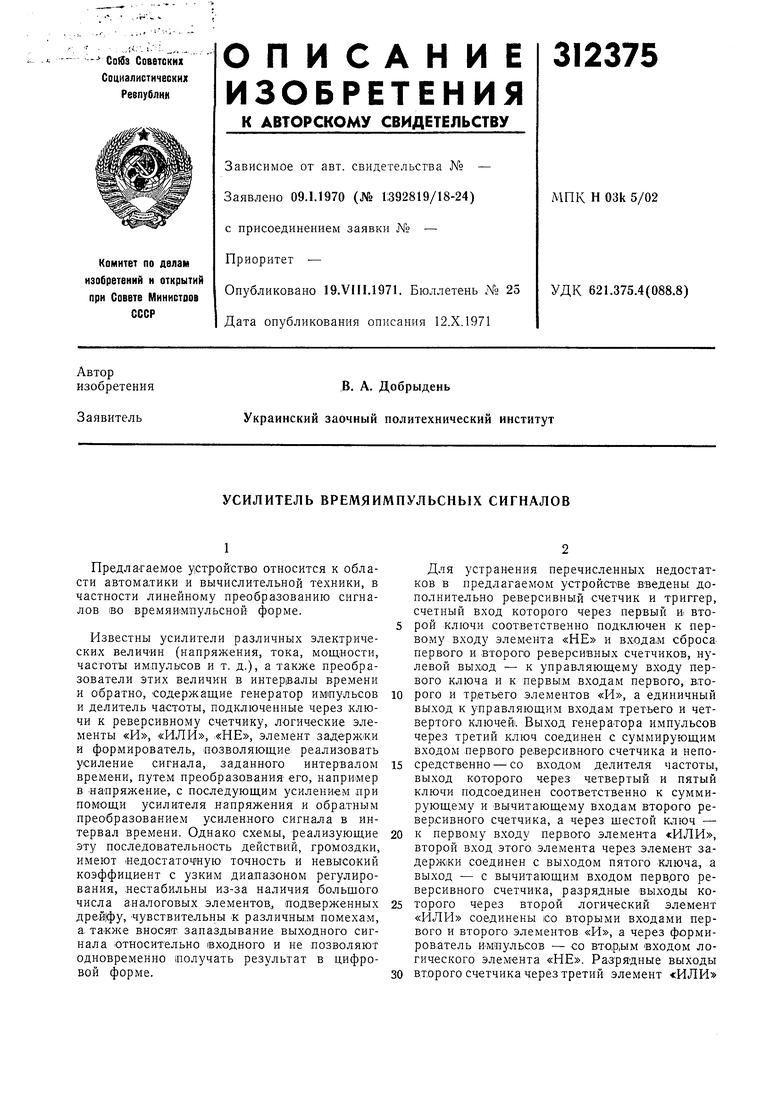

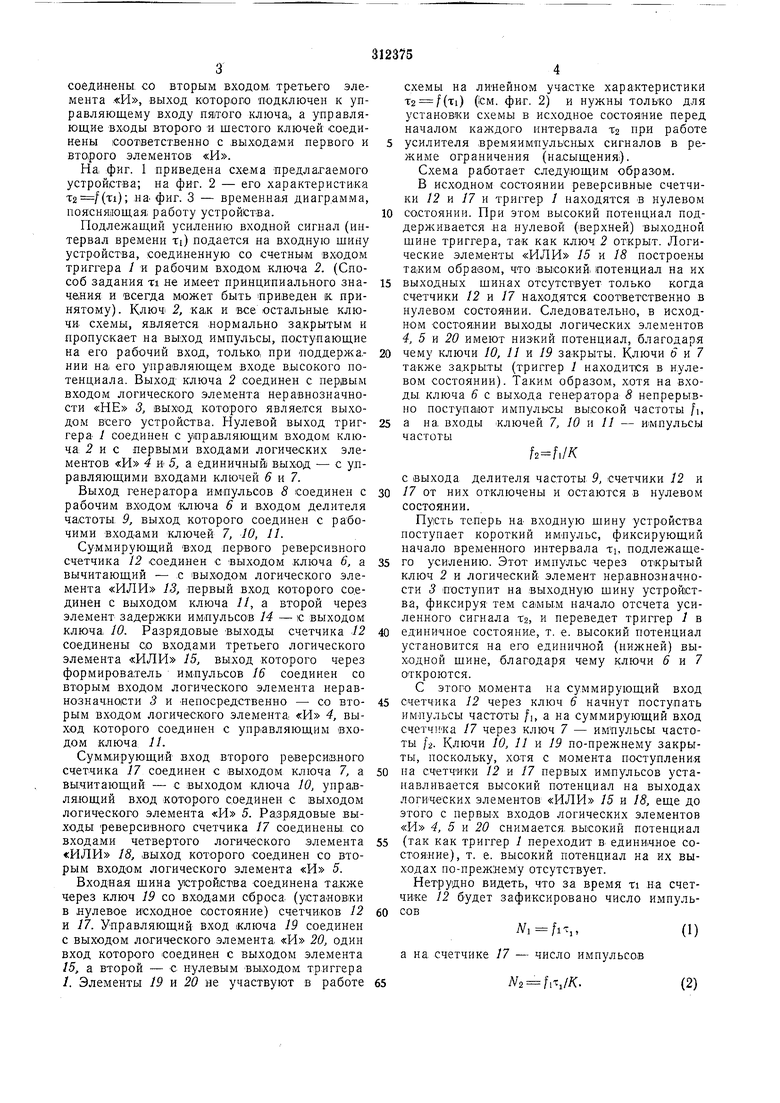

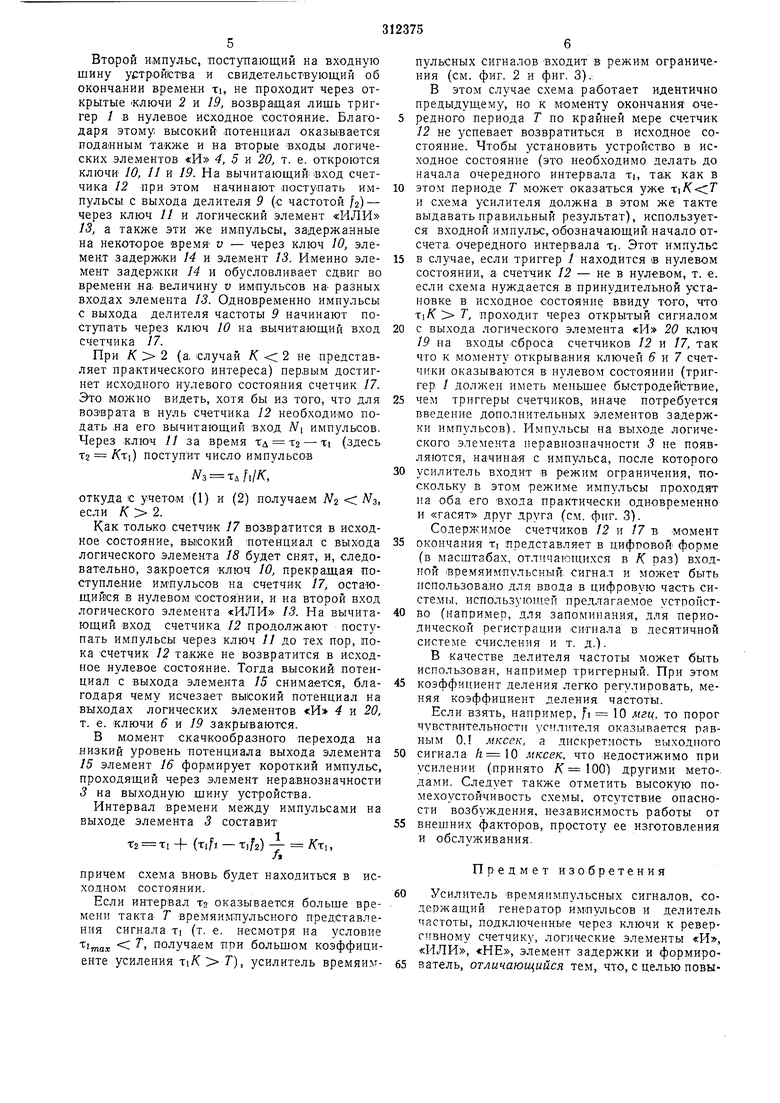

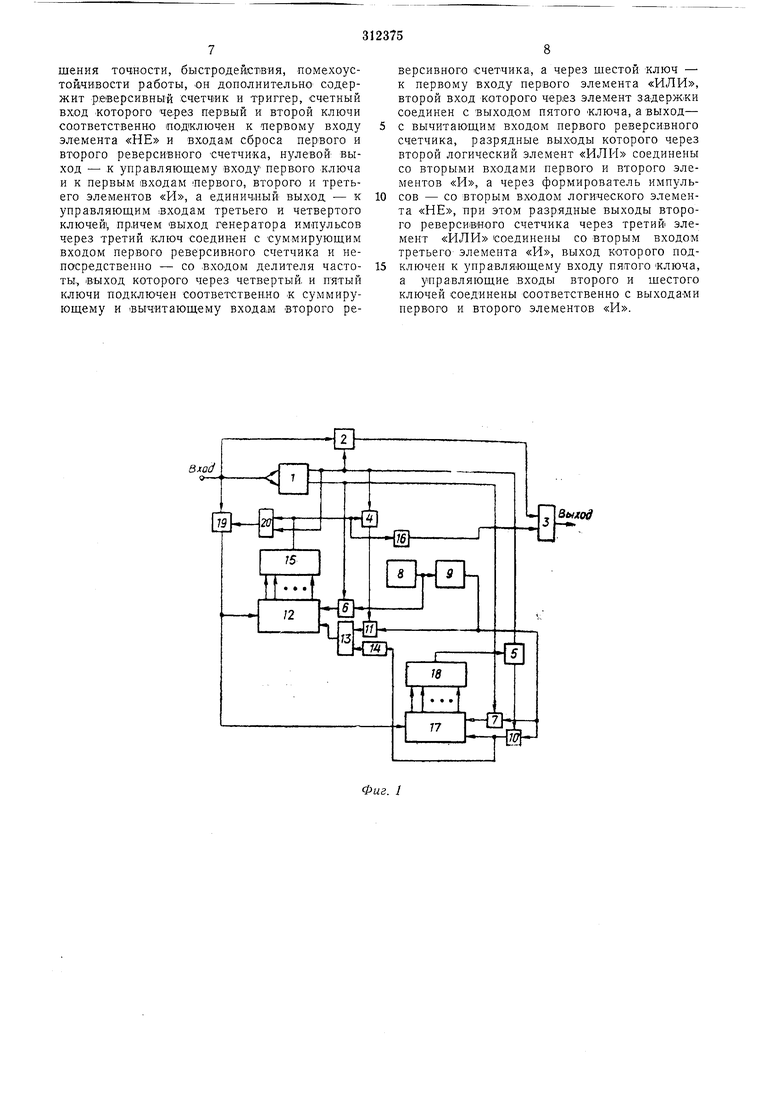

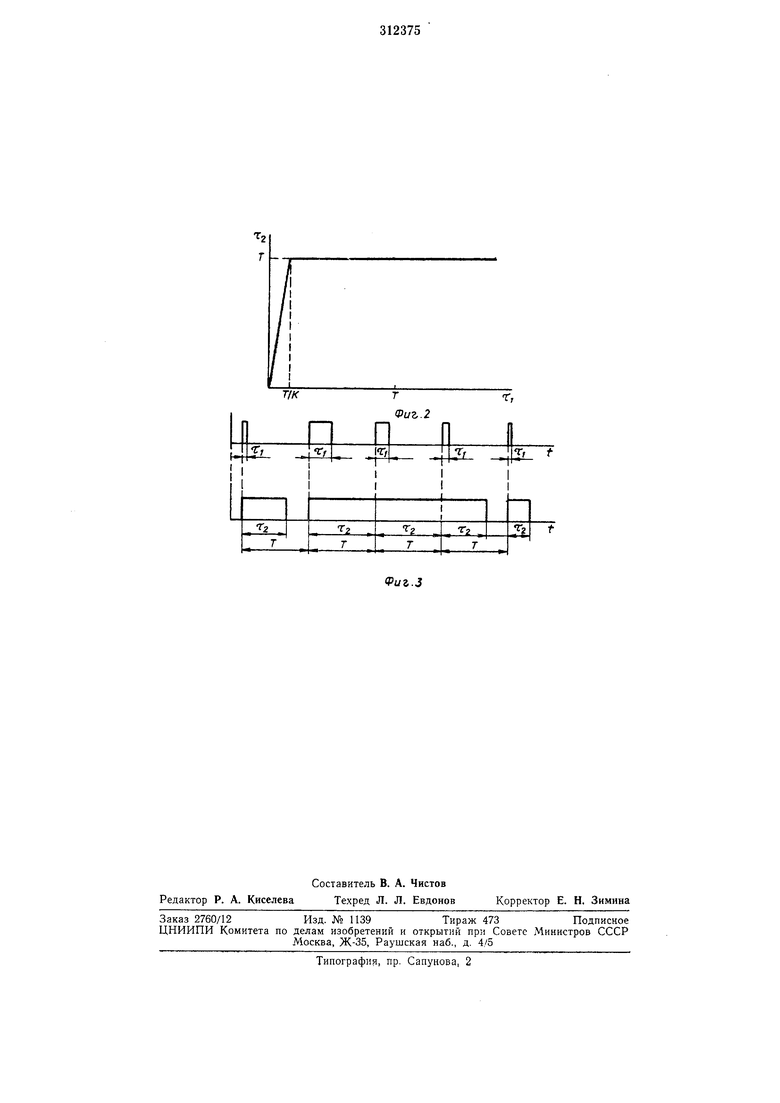

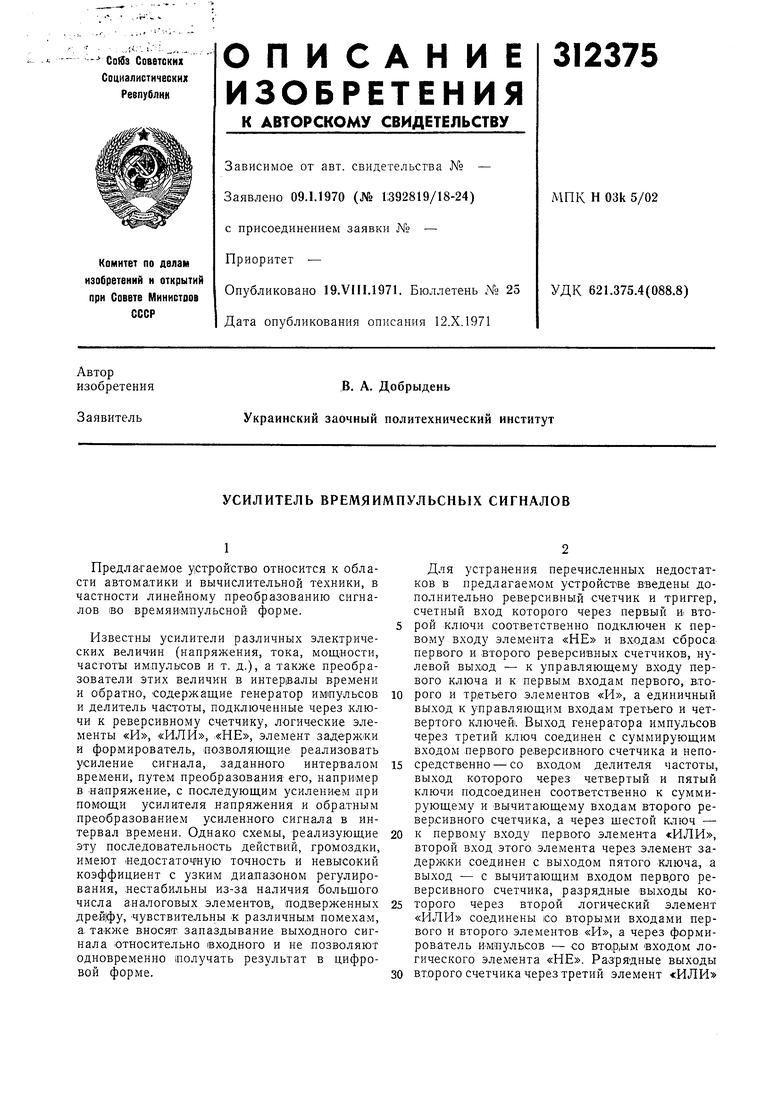

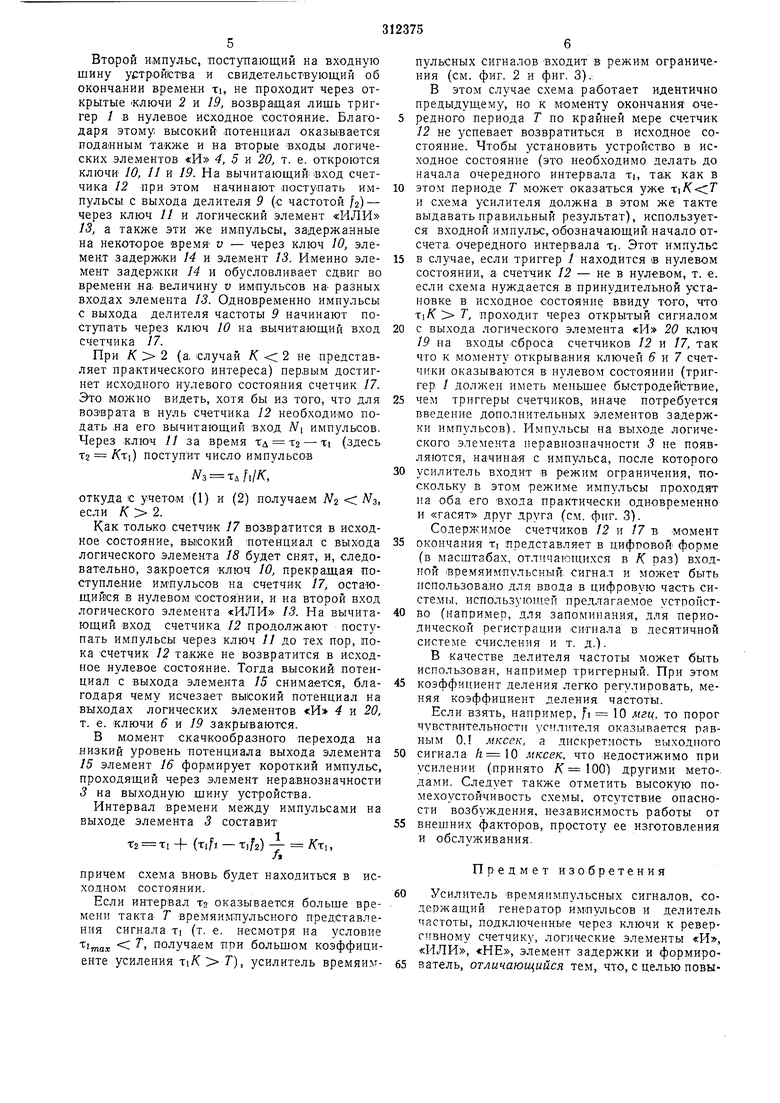

Для устранения перечисленных недостатков в предлагаемом устройстве введены дополнительно реверсивный счетчик и триггер, счетный вход которого через первый и второй ключи соответственно подключен к первому входу элемента «НЕ и входал: сброса первого и второго реверсивных счетчиков, нулевой выход - к управляющему входу первого ключа и к первым входам первого, второго и третьего элементов «И, а единичный выход к управляющим входам третьего и четвертого ключей. Выход генератора импульсов через третий ключ соединен с суммирующим входом первого реверсивного счетчика и непосредственно - со входом делителя частоты, выход которого через четвертый и пятый ключи подсоединен соответственно к суммирующе.му и вычитающему входам второго реверсивного счетчика, а через щестой ключ - к первому входу первого элемента «ИЛИ, второй вход этого элемента через элемент задержки соединен с выходом пятого ключа,, а выход - с вычитающим входом первого реверсивного счетчика, разрядные выходы которого через второй логический элемент «ИЛИ соединены со вторыми входами первого и второго элементов «И, а через формиров.атель импульсов - со вто,р|Ым входом логического элемента «НЕ. Разрядные выходы второго счетчика через третий элемент «ИЛИ соедИНены со вторым входом, третьего элемента «И, выход которого подключен к управляющему входу патого ключа, а управляющие входы второго и шестого ключей соединены соответственно с выходами первого и второго элементов «И. На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - его характеристика (Ti); па. фиг. 3 - временная диаграмма, поясняющая, работу устройства. Подлежащий усилению входной сигнал (интервал времени TI) подается на входную шину устройства, соединенную со счетным входом триггера / и рабочим входом 2. (Способ задания TI не имеет принципиального значения и всегда мюжет быть приведен к принятому) . Ключ 2, как и все остальные ключи, схемы, является, нормально закрытым и пропускает на выход импульсы, поступающие на его рабочий вход, только, при поддерл а.нии на его управляющем входе в.ысокого потенциала. Выход ключа 2 соединен с первым входом логического элемента неравнозначности «НЕ 3, выход которого является выходом всего устройства. Нулевой выход триггера 1 соединен с управляющим входом ключа 2 и с первыми входами логических элементов «И 4 № 5, а единичный выход - с управляющими входами ключей 5 и 7. Выход генератора импульсов 8 соединен с рабочим входом ключа 6 и входом делителя частоты, Я выход которого соединен с рабочими входами ключей 7, 10, 11. Суммирующий ВХОД первого реверсивного счетчика 12 соединен с БЫХОДОМ ключа 6, а вычитающий - ,с выходом логического элемента «ИЛИ 13, первый вход которого соединен с выходом ключа //, а второй через элемент задержки импульсов 14 - с выходом ключа 10. Разрядовые в,ыходы счетчика 12 соединены со входами третьего логического элемента «ИЛИ 15, выход которого через формирователь им,пульсов 16 соединен со вторым входом логического элемента неравнозначнасти 3 и -непосредственно - со вторым входом логического элемента «И 4, выход которого соединен с упргавляющим входом ключа 11. Суммирующий вход второго реверсигзного счетчика 17 соединен с выходом ключа 7, а вычитающий - с выходом ключа 10, управляющий вход Которого соединен с выходом логического элемента «И 5. Разрядовые выходы реверсивно,го счетчика 17 соединены, со входа,ми четвертого л,огического элемента «ИЛИ 18, выход которого соединен со вторым входом логического элемента «И 5. Входная щина у1стройслва соединена также через ключ 19 со входами сброса (установки в нулевое исходное состояние) счетчиков 12 и 17. Управляющий вход ключа 19 соединен с выходом логического элемента «И 20, один вход которого соединен с выходом элемента 15, а второй - с нулевым выходом триггера /. Элементы 19 и 20 не участвуют в работе схемы на линейном участке характеристики T2 /(Ti) (CM. фиг. 2) и нужны только для установки схемы в исходное состояние перед началом каждого интервала та при работе усилителя ,времяимт1ульсных сигналов в режиме ограничения (насыщения). Схема работает следующим образом. В исходном состоянии реверсивные счетчики 12 и 17 и триггер / находятся в нулевом состоянии. При этом высокий потенциал поддерживается ,на нулевой (верхней) выходной щине триггера, так как ключ 2 открыт. Логические элементы «ИЛИ 15 и 18 построены та,ким образом, что высокий потенциал на их выходных шинах отсутствует только когда счетчики 12 и 17 находятся соответственно в нулевом состоянии. Следовательно, в исходном состоянии выходы логических элементов 4, 5 к 20 имеют низкий потенциал, благодаря чему ключи 10, 11 и 19 закрыты. Ключи о и 7 также закрыты (триггер / находится в нулевом состоянии). Таким образом, хотя на входы, ключа 6 с выхода генератора 8 непрерывно поступают импульсы высокой частоты /ь а на входы ключей 7, 10 и 11 - и-мпульсы частоты h С 1выхода делителя частоты 9, счетчики 12 и 17 от них отключены и остаются в нулевом состоянии. Пусть теперь на входную шину устройства поступает короткий импульс, фиксирующий начало временного интервала ть подлежащего усилению. Этот импульс через открытый ключ 2 и логический элемент нер,авнозначности 3 поступит на выходную шину устройства, фиксируя тем catMbiM на.чало отсчета усиленного сигнала Т2, и переведет триггер 1 в единичное состояние, т. е. высокий потенциал установится на его единичной (нижней) выходной шине, благодаря чему ключи 5 и 7 откроются. С этого момента на суммирующий вход счетчика 12 через ключ 6 начнут поступать импульсы частоты fj, а на суммирующий вход счетчика 17 через ключ 7 - импульсы частоты /2. Клю,чи 10, 11 и 19 по-прежнему закрыты, поскольку, хотя с момента поступления на счетчики 12 и 17 первых импульсов устанавливается высокий потенциал на выходах логических элементов «ИЛИ 15 и 18, еще до этого с первьгх входов логических элементов «И 4, 5 и 20 снимается, высокий потенциал (так как триггер 1 переходит в единичное состояние), т. е. высокий потенциал на их выходах по-прежйему отсутствует. Нетрудно видеть, что за время TI на счетчике 12 будет зафиксировано число импульAl /i n(1) Второй импульс, поступающий на входную шину уетр-ойсгва и свидетельст-вующий об окончании времени TI, не проходит через открытые КЛЮЧИ 2 и 19, возвращая лишь триггер 1 в нулевое исходное состояние. Благодаря этому, высокий потенциал оказывается пода«ным та-кже и на вторые входы логических элементов «И 4, 5 и 20, т. е. откроются ключи 10, 11 и 19. На вычитаюший вход счетчика 12 при этом начинают .поступать импульсы, с выхода делителя 9 (с. частотой /2) - через ключ // и логический элемент «ИЛИ 13, а также эти же имлульсы, задержанные на некоторое время v - через ключ 10, элемент задержки 14 и элемент 13. Именно элемент задерл ки 14 и обусловливает сдвиг во времени .на величину v импульсов на разных входах элемента 13. Одновременно импульсы с выхода делителя частоты 9 начинают поступать через ключ 10 на вычитающий вход счетчика 17. При /С 2 (а. случай /С 2 не представляет практического интереса) первым достигнет исходного нулевого состояния счетчик 17. Это можно видеть, хотя бы из того, что для возврата в нуль счетчика 12 необходи.мо подать .на его вычитающий вход NI импульсов. Через ключ 11 за время тд Т2 - TI (здесь тг : /(TI) поступит число импульсо.в ТдЫЛ:, откуда с учето.м (1) и (2) получа.ем NZ Л/з, если /С 2. Как только счетчиК 17 воавратится в исходное состояние, высокий потенциал с выхода логического элемента 18 будет снят, и, следовательно, за-кроется Ключ 10, прекращая поступле.ние импульсов на счетчик 17, остающийся в нулевом состоянии, и на второй вход логического элемента «ИЛИ 13. На вычитающий вход счетчика 12 продолжают поступать импульсы через ключ // до тех пор, пока счетчик 12 та1кже не возвратится в исходное нулевое состояние. Тогда высокий потенциал с выхода элемента 15 снимается, благодаря чему исчезает вьисокий потенциал на выходах логических элементов «И 4 и 20, т. е. ключи 6 и 19 за.Крываются. В м.омент скачкообразного перехода на низкий уровень потенциала выхода элемента 15 элемент 16 фор1мирует короткий импульс, проходящий через элемент нера.в.нозначности 3 на выходную шину устройства. Интервал времени между импульсами на выходе элемента 3 составит Т2 TI + (fif J - 1/2) - /Ст,, причем схема вновь будет находиться в исходно.м состоянии. Если интервал тг оказывается больше времени такта Т времяимпульсного представления сигнала TI (т. е. несмотря на условие получа.ем при большом коэффиципульсных сигналов -входит в режим ограничения (см. фиг. 2 и фиг. 3),: В этом случае схема работает идентично предыдуш,ему, но к моменту окончания очередного периода Т по крайней мере счетчик 12 не успевает возвратиться в исходное состояние. Чтобы установить устройство в исходное состояние (это необходимо делать до начала очередного интервала TI, та,к как в этом периоде Т может оказаться уже ciK.i,T и схема усилителя должна в этом же такте выдавать правильный результат), используется входной импульс, обозначающий начало отсчета, очередного интервала ть Этот импульс в случае, если триггер / находится в нулевом состоянии, а счетчик 12 - не в нулев.ом, т. е. если схема нуждается в принудительной утта новке в исходное состояние ввиду то.го, что Ti/C Т, проходит через открытый сигналом с выхода логического элемента «И 20 ключ 19 на входы сброса счетчиков 12 и 17, так что к м.оменту открывания ключей 5 и 7 счетчики оказываются в нулевом состоянии (триггер / должен иметь меньшее бы.стродействие, чем триггеры счетчиков, иначе потребуется введение дополнительных элементов задержки импульсов). Импульсы на выходе логического элемента неравнозначности 3 не появляются, начиная с имнульса, после которого усилитель входит в режим ограничения, поскольку в этом режиме импульсы проходят на оба его входа пра:ктически одновременно и «гасят друг друга (см. фиг. 3). Содержимое счетчиков 12 и 17 в момент окончания TI представляет в цифровой форме (в масштабах, отличающихся в К раз) входной 1времяимпульсный сигнал и может быть пспользова.но для ввода в цифровую часть системы, использующей предлагаемое устройство (например, для запоминания, для периодической регистрации сигнала в десятичной системе счисления и т. д.). В качестве делителя частоты может быть использован, например триггерный. При этом коэффициент деления легко регулировать, меняя коэффициент деления частоты. Если взять, например, fi 10 мгц, то порог чувствительностц устлнтеля оказывается равным 0,1 мксек, а дискретность выходного сигнала мксек. что .недостижимо при усилении (принято /С 100) другими мето-. дами. Следует также отметить высокую помехоустойчивость схемы, отсутствие опасности возбуждения, независимость работы от внешних факторов, простоту ее изготовления и обслуживания. Предмет изобретения Усилитель времяимпульсных сигналов, содержащий генератор импульсов и делитель частоты, подключенные через ключи к реверсивному счетчику, логические элементы «И, «ИЛИ, «НЕ, элемент задержки и формирошения точности, быстродействия, помехоустойчивости работы, он дополнительно содержит реверсивный счетчик и триггер, счетный вход Которого через первый и второй ключи соответственно подключен к TiepBOMy входу элемента «НЕ и входам сброса первого и второго реверсивного Счетчика, нулевой выход - к управляюндему входу первого ключа и к первым входам первого, второго и третьего элементов «И, а единичный выход - к управляющим входам третьего и четвертого ключей, пр.ичем выход генератора импульсов через третий ключ соединен с суммирующим входом первого реверсивного счетчика и непосредственно - со входом делителя частоты-, выход которого через четвертый, и нятый ключи подключен соответственно к суммирующему и вычитающему входам второго реверсивного счетчика, а через щестой ключ - к первому входу первого элемента «ИЛИ, второй вход которого через элемент задержки соединен с выходом пятого Ключа, а выход- с вычитающим входом первого реверсивного счетчика, разрядные выходы которого через второй логический элемент «ИЛИ соединены со вторыми входами первого и второго элементов «И, а через формирователь импульсов - со вторым входом логического элемента «НЕ, при этом разрядные выходы второго реверсивного счетчика через третиЙ элемент «ИЛИ соединены со вторым входом третьего элемента «И, выход которого подключен к управляющему входу пятого -ключа, а управляющие входы второго и щестого ключей соединены соответственно с выходами первого и второго элементов «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Расширитель временных интервалов | 1975 |

|

SU532079A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Измеритель мощности | 1983 |

|

SU1093925A1 |

| ЦИФРОВОЙ ИНФРАНИЗКОЧАСТОТКЫЙ ФАЗОМЕТР- ЧАСТОТОМЕР | 1966 |

|

SU189485A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Устройство для формирования времязадающих интервалов | 1986 |

|

SU1439733A1 |

| Устройство для управления электродвигателем постоянного тока | 1987 |

|

SU1608776A1 |

| Преобразователь частоты в двоичный код | 1981 |

|

SU995319A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Устройство для расширения временных интервалов | 1980 |

|

SU928295A1 |

Г,

Даты

1971-01-01—Публикация