Изобретение относится к области электрических измерений и может быть использовано при построении высокоточных измерительных приборов.

Целью изобретения является повышение точности измерения.

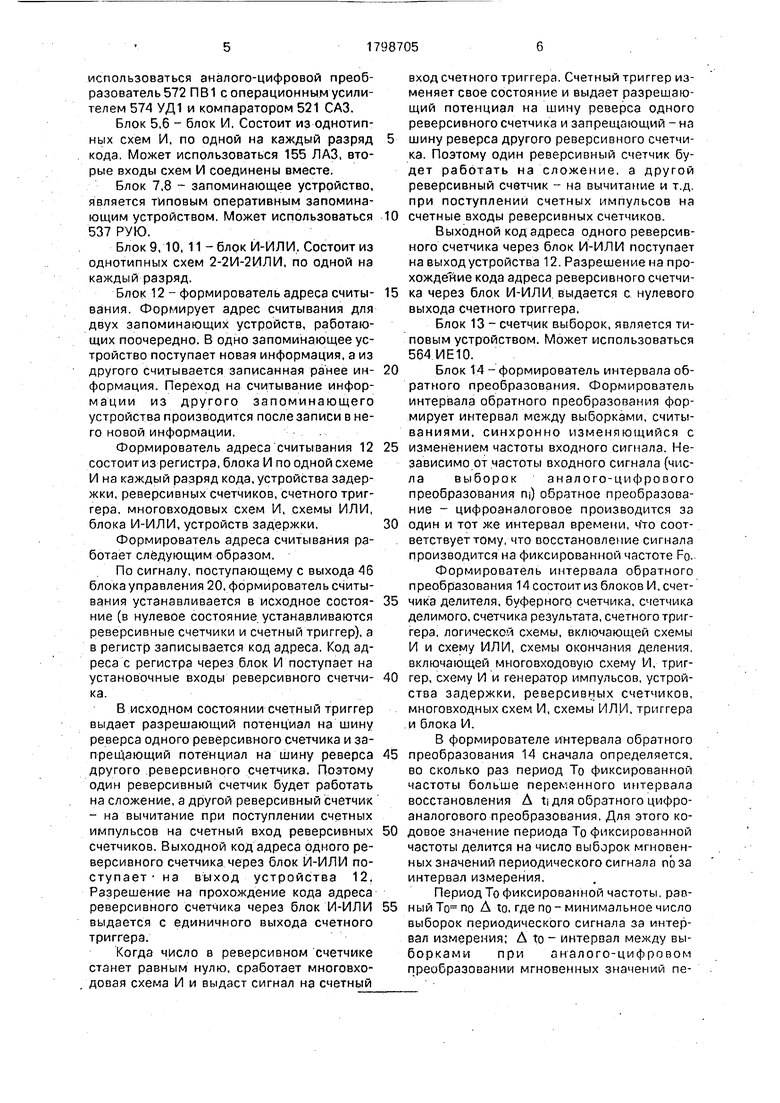

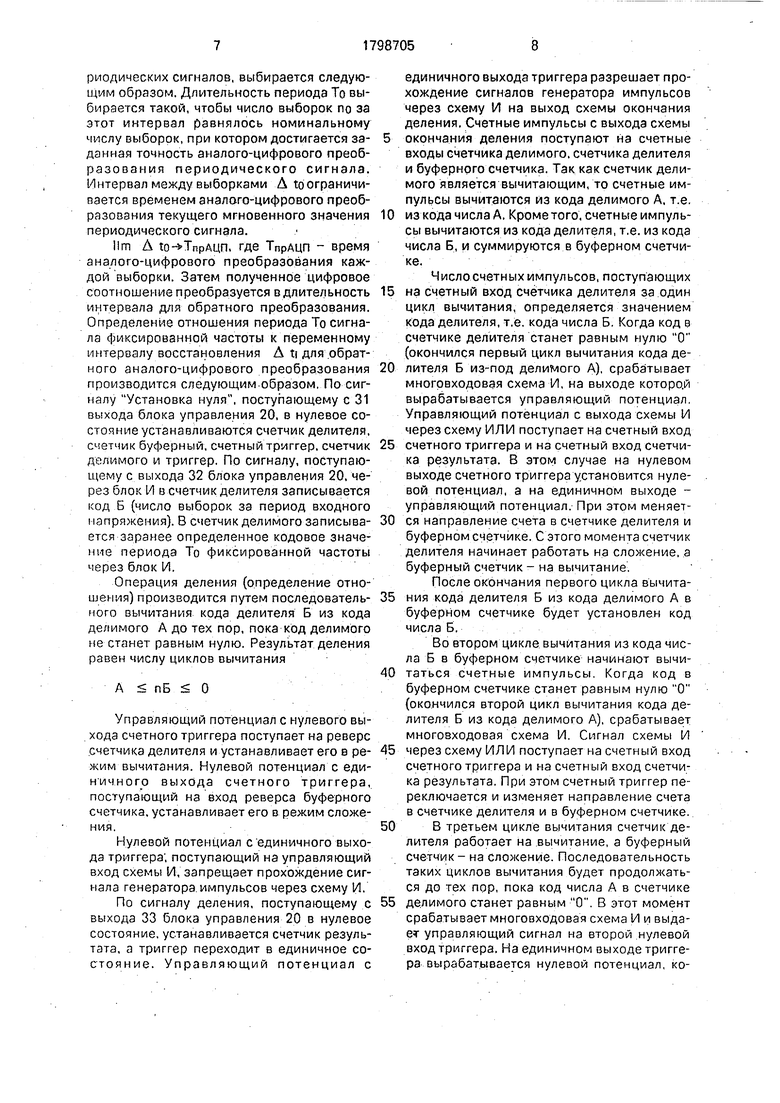

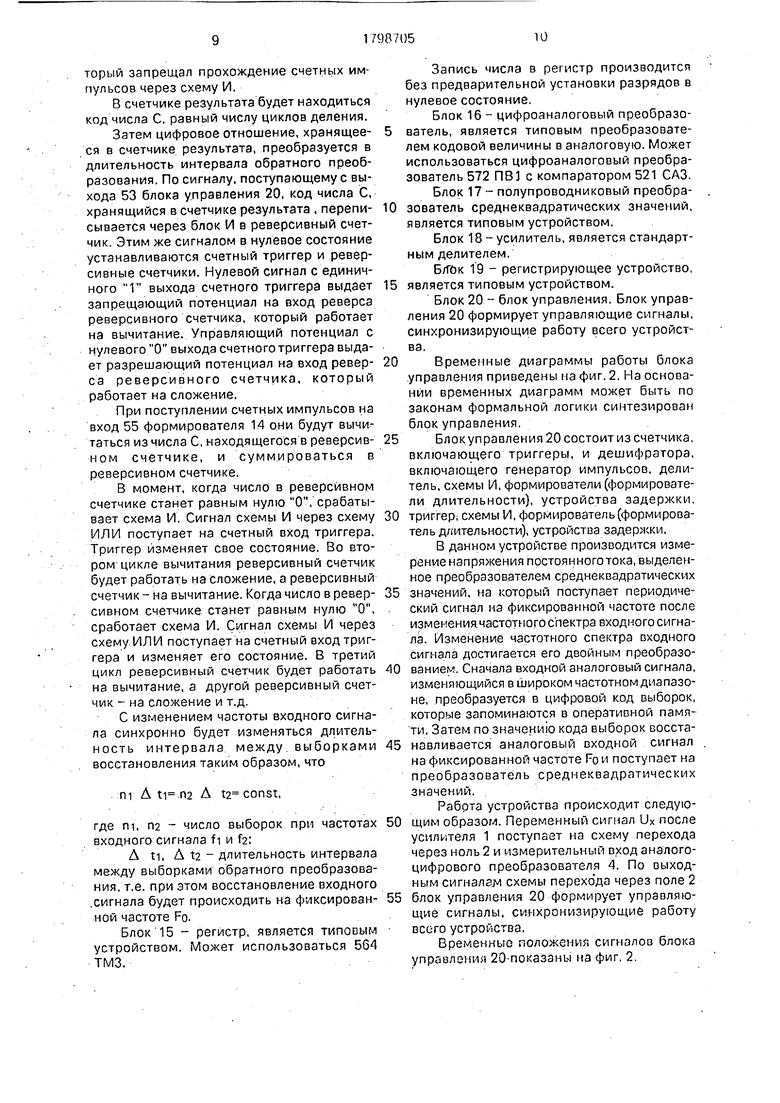

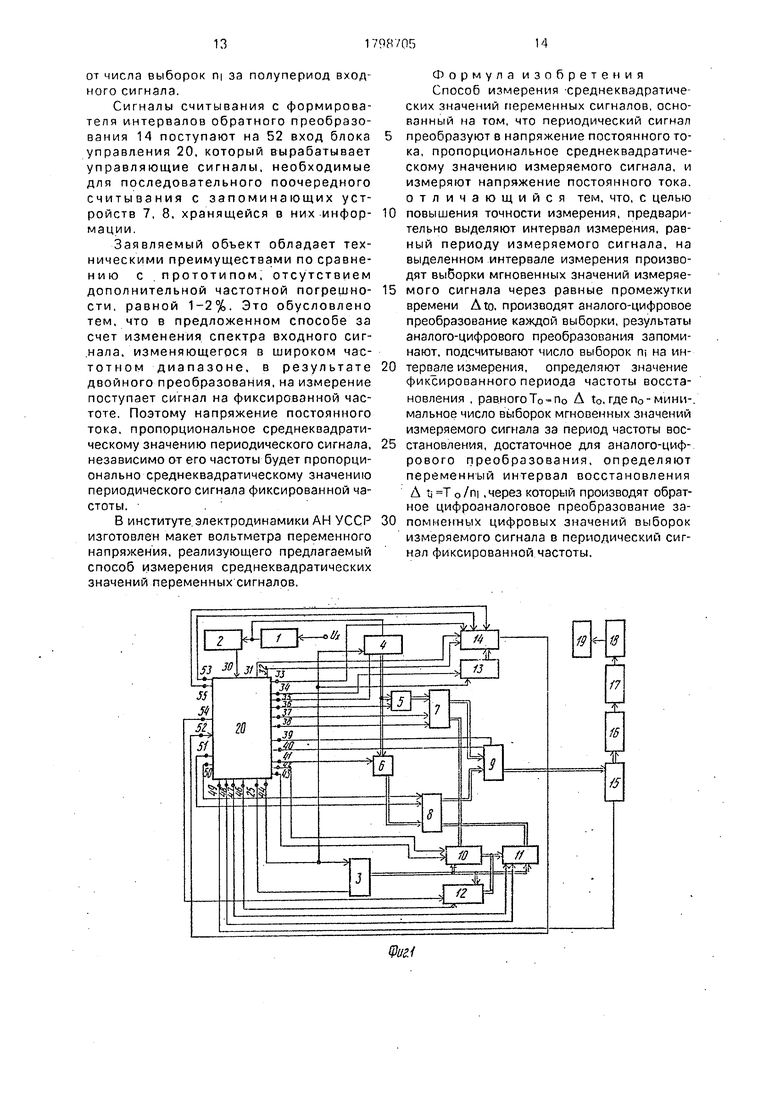

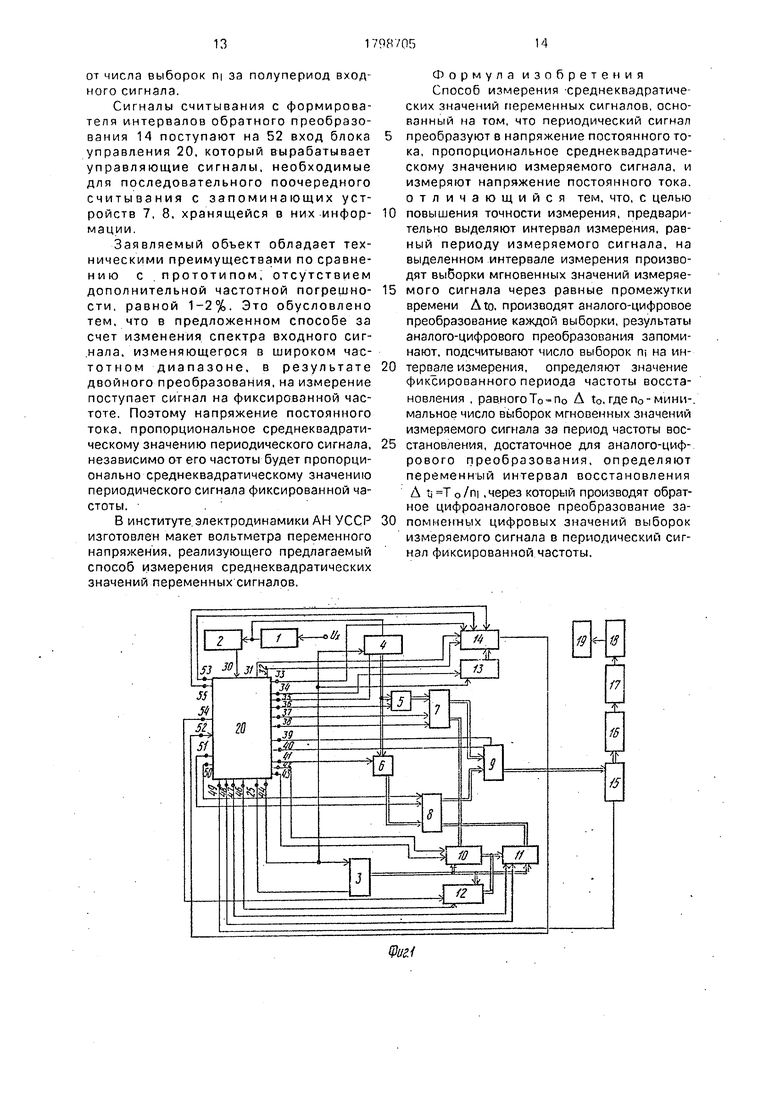

На фиг. 1 представлена блок-схема устройства, реализующая предлагаемый способ измерения среднеквадратических значений переменных сигналов; на фиг. 2 - временные диаграммы работы блока управления устройства, реализующего предлагаемыйспособ измерения среднеквадратических значений переменных сигналов.

В предлагаемом способе реализованы следующие операции в такой последовательности: выделение интербала измерения. проведение на выделенном интервале измерения через равные интервалы времени выборок мгновенных значений периодического измеряемого сигнала; проведение

(/

с

прямого зналого-цифрового преобразования каждой выборам мгновенного значения периодического сигнала; запоминание цифровых значений выборок; подсчет числа выборок щ за выделенный интервал измерения; определение и запоминание значений периода фиксированной частоты То, равного То no A to, где по - минимальное число выборок мгновенных значений периодического сигнала за период фиксированной частоты, достаточное для аналого- цифрового преобразования периодического сигнала; A to - интервал между выборками аналого-цифрового преобразования; определение переменного интервала восстановле- ния ДЬ для обратного циф роаналогового

преобразования по формуле

д - Ј -

XI

О

со

xi О СП

проведение обратного цифроаналогового преобразования запомненных цифровых значений выборок измеряемого сигнала в периодический сигнал фиксированной частоты FO; преобразование периодического сигнала в напряжение постоянного тока, пропорциональное среднеквадратичному значению периодического сигнала, измерение напряжения постоянного тока, пропорциональное среднеквадратическому значению периодического сигнала.

Устройство, реализующее предлагаемый способ измерений среднеквадратиче- ских значений переменных сигналов (фиг. 1), состоит из усилителя 1, схемы перехода через О 2, счетчика-адреса 3, аналого-цифрового преобразователя 4, блоков И 5, 6, запоминающих устройств 7, 8, блоков И-ИЛИ 9-11, формирователя адреса считывания 12, счетчика выборок 13, формирователя интервала обратного преобразования 14. регистра 15, цифроэналогового преобразователя 16, преобразователя среднеквадратических значений 17, усилителя 18, регистрирующего устройства 19 и блока управления 20.

Вход прибора Ux соединен с входом усилителя 1. Выход усилителя 1 соединен с входом схемы перехода через О 2 и сигнальным входом аналого-цифрового преобразователя 4. Выход схемы перехода через О 2 соединен с входом 30 блока управления 20.

Нулевой вход счетчика адреса 3 соединен с выходом 45 блока управления 20, выход 44 которого соединен с счетным входом счетчика адреса 3, запускающим входом аналого- цифрового преобразователя 4 и счетным входом счетчика выборок 13. Выход счетчика адреса 3 (параллельный код) соединен с первыми входами блоков И-ИЛИ 10, 11 и формирователя адреса считывания 12.

Первый вход блока И 5 соединен с выходом 36 блока управления 20, второй вход (параллельный код) схемы И 5 соединен с выходом аналого-цифрового преобразователя 4 и первым входом блока И6, второй вход которого соединен с выходом 41 блока управления 20, выход 35 которого соединен с тактирующим входом аналого-цифрового преобразователя 4. Выход блока И 5 (параллельный код) соединен с информационным входом запоминающего устройства 7. Вход записи запоминающего устройства 7 соединен с выходом 37 блока управления 20, выход 38 которого соединен с входом считывания запоминающего устройства 7. Адресный вход (параллельный код) запоминающего устройства 7 соединен с выходом блока И-ИЛИ 10, информационный выход запоминающего устройства 7 (параллельный код) соединен с первым входом блока И- ИЛИ 9.

Вход записи запоминающего устройства 8 соединен с выходом 50 блока управления 20, выход 51 которого соединен с

входом считывания запоминающего устройства 8. Адресный выход (параллельный код) запоминающего устройства 8 соединен с выходом блока И-ИЛИ 11, информационный

выход запоминающего устройства 8 (параллельный код) соединен со вторым входом блока И-ИЛИ 9, третий и четвертый входы которого соединены соответственно с 39 и 40 выходами блока управления 20. Выход блока

0 И-ИЛИ 9 (параллельный код) соединен с информационным входом регистра 15.

Второй вход блока И-ИЛИ 10 (параллельный код) соединен с вторым входом блока И-ИЛИ 11 и выходом формирователя адреса

5 считывания 12. Третий и четвертый входы блока И-ИЛИ 10 соответствен но соединены с. 42 и 43 выходами блока управления 20, выходы 47,48 которого соответственно соединены с третьим и четвертым входами блока И-ИЛИ

0 ц. .

Нулевой вход формирователя адреса считывания 12 соединен с 46 выходом блока управления 20. Тактирующий вход формирователя адреса считывания 12 сое5 динен с 54 выходом блока управления 20.

Нулевой вход регистра 15 соединен с выходом 49 блока управления 20. Выход р.е- гистра 15 (параллельный код) соединен с входом цифроаналогового преобразователя

0 16, выход которого через преобразователь среднеквадратических значений 17 и усилитель 8 соединен с регистрирующим устройством 19.

Нулевой вход счетчика выборок 13 сое5 динен с выходом 34 блока управления 20. Выход счетчика выборок 13 (параллельный код) соединен с первым входом формирователя интервала обратного преобразования 14. второй, третий, четвертый и пятый входы

0 которого соответственно соединены с выходами 31, 32, 33, 53, 55 блока управления 20. Выход формирователя интервала обратного преобразования 14 соединен со вторым входом 52 блока управления 20.

5Блок 1 - усилитель, является обычным усилителем.

Блок 2 - схема перехода через ноль, является обычным пороговым устройством, формирующим из входного переменного

0 напряжения сигналы его перехода через ноль. Устройство может быть выполнено на компараторе 521 САЗ, выделяющем моменты перехода через ноль переменного напряжения.

5 Блок 3 - счетчик адреса, является типовым элементом. Может использоваться 564 НЕ 10.

Блок 4 - аналого-цифровой преобразователь, является преобразователем аналоговой величины в цифровую. Может

использоваться аналого-цифровой преобразователь 572 ПВ1 с операционным усилителем 574 УД1 и компаратором 521 САЗ.

Блок 5,6 - блок И. Состоит из однотипных схем И, по одной на каждый разряд кода. Может использоваться 155 ЛАЗ, вторые входы схем И соединены вместе.

Блок 7,8 - запоминающее устройство, является типовым оперативным запоминающим устройством. Может использоваться 537 РУЮ.

Блок 9,10, 11 - блок Й-ИЛИ. Состоит из однотипных схем 2-2И-2ИЛИ, по одной на каждый разряд.

Блок 12 - формирователь адреса считывания. Формирует адрес считывания для двух запоминающих устройств, работающих поочередно. В одно запоминающее устройство поступает новая информация, а из другого считывается записанная ранее информация. Переход на считывание информации из другого запоминающего устройства производится после записи в него новой информации..

Формирователь адреса считывания 12 состоит из регистра, блока И по одной схеме И на каждый разряд кода, устройства задержки, реверсивных счетчиков, счетного триггера, многовходовых схем И, схемы ИЛИ, блока И-ИЛИ, устройств задержки.

Формирователь адреса считывания работает следующим образом.

По сигналу, поступающему с выхода 46 блока управления 20, формирователь считывания устанавливается в исходное состояние (в нулевое состояние устанавливаются реверсивные счетчики и счетный триггер), а в регистр записывается код адреса, Код адреса с регистра через блок И поступает на установочные входы реверсивного счетчика.

В исходном состоянии счетный триггер выдает разрешающий потенциал на шину реверса одного реверсивного счетчика и запрещающий потенциал на шину реверса другого реверсивного счетчика. Поэтому один реверсивный счетчик будет работать на сложение, а другой реверсивный счетчик - на вычитание при поступлении счетных импульсов на счетный вход реверсивных счетчиков. Выходной код адреса одного реверсивного счетчика через блок Й-ИЛИ поступает на выход устройства 12. Разрешение на прохождение кода адреса реверсивного счетчика через блок И-ИЛИ выдается с единичного выхода счетного триггера.

Когда число в реверсивном счетчике станет равным нулю, сработает многовхо- довая схема И и выдаст сигнал на счетный

вход счетного триггера. Счетный триггер изменяет свое состояние и выдает разрешающий потенциал на шину реверса одного реверсивного счетчика и запрещающий - на

шину реверса другого реверсивного счетчика. Поэтому один реверсивный счетчик будет работать на сложение, а другой реверсивный счетчик - на вычитание и т.д. при поступлении счетных импульсов на

счетные входы реверсивных счетчиков.

Выходной код адреса одного реверсивного счетчика через блок И-ИЛИ поступает на выход устройства 12. Разрешение на прохождение кода адреса реверсивного счетчика через блок И-ЙЛИ. выдается с нулевого выхода счетного триггера,

Блок 13 - счетчик выборок, является типовым устройством. Может использоваться 564ИЕ10.

Блок 14 - формирователь интервала обратного преобразования. Формирователь интервала обратного преобразования формирует интервал между выборками, считываниями, синхронно изменяющийся с

изменением частоты входного сигнала. Независимо от частоты входного сигнала (числа выборок аналого-цифрового преобразования т) обратное преобразование - цифроаналоговое производится за

один и тот же интервал времени, ч то соответствует тому, что восстановление сигнала производится на фиксированной частоте FQ. Формирователь интервала обратного преобразования 14 состоит из блоков И, счетчика делителя, буферного счетчика, счетчика делимого, счетчика результата, счетного триггера, логической схемы, включающей схемы И и схему ИЛИ, схемы окончания деления, включающей многовходовую схему И, триггер, схему И и генератор импульсов, устройства задержки, реверсивных счетчиков, многовходных схем И, схемы ИЛИ, триггера .и блока И.

В формирователе интервала обратного

преобразования 14 сначала определяется, во сколько раз период То фиксированной частоты больше переменного интервала восстановления A ti для обратного цифро- аналогового преобразования. Для этого кодовое значение периода Тр фиксированной частоты делится на число выборок мгновенных значений периодического сигнала по за интервал измерения.

Период То фиксированной частоты, рапныйТо по A to, где по-минимальное число выборок периодического сигнала за интервал измерения; A to - интервал между выборками при зналого-цифровом преобразовании мгновенных значений периодических сигналов, выбирается следующим образом. Длительность периода То выбирается такой, чтобы число выборок по за этот интервал равнялось номинальному числу выборок, при котором достигается за- данная точность аналого-цифрового преобразования периодического сигнала. Интервал между выборками A to ограничивается временем аналого-цифрового преобразования текущего мгновенного значения периодического сигнала.

Urn А ю- ТпрАЦП. где Тпрдцп - время аналого-цифрового преобразования каждой выборки. Затем полученное цифровое соотношение преобразуется в длительность интервала для обратного преобразования. Определение отношения периода То сигнала фиксированной частоты к переменному интервалу восстановления A ti для обратного аналого-цифрового преобразования производится следующим образом. По сигналу Установка нуля, поступающему с 31 выхода блока управления 20, в нулевое состояние устанавливаются счетчик делителя, счетчик буферный, счетный триггер, счетчик делимого и триггер. По сигналу, поступающему с выхода 32 блока управления 20, через блок И в счетчик делителя записывается код Б (число выборок за период входного напряжения). В счетчик делимого записыва- ется заранее определенное кодовое значение периода То фиксированной частоты через блок И.

Операция деления (определение отношения) производится путем последователь- ного вычитания кода делителя Б из кода делимого А до тех пор, пока код делимого не станет равным нулю. Результат деления равен числу циклов вычитания

А пБ О

Управляющий потенциал с нулевого выхода счетного триггера поступает на реверс .счетчика делителя и устанавливает его в ре- жим вычитания. Нулевой потенциал с единичного выхода счетного триггера, поступающий на вход реверса буферного счетчика, устанавливает его в режим сложения.

Нулевой потенциал с единичного выхода триггера; поступающий на управляющий вход схемы И, запрещает прохождение сигнала генератора, импульсов через схему И,

По сигналу деления, поступающему с выхода 33 блока управлениями в нулевое состояние, устанавливается счетчик результата, а триггер переходит в единичное состояние. Управляющий потенциал с

единичного выхода триггера разрешает прохождение сигналов генератора импульсов через схему И на выход схемы окончания деления. Счетные импульсы с выхода схемы окончания деления поступают на счетные входы счетчика делимого, счетчика делителя и буферного счетчика. Так как счетчик делимого является вычитающим, то счетные импульсы вычитаются из кода делимого А. т.е. из кода числа А. Кроме того, счетные импульсы вычитаются из кода делителя, т.е. из кода числа Б, и суммируются в буферном счетчике.

Числосчетныхимпульсов, поступающих на счетный вход счётчика делителя за один цикл вычитания, определяется значением кода делителя, т.е. кода числа Б, Когда код в счетчике делителя станет равным нулю О (окончился первый цикл вычитания кода делителя Б из-под делимого А), срабатывает многрвходовая схема И, на выходе которой вырабатывается управляющий потенциал. Управляющий потенциал с выхода схемы И через схему ИЛИ поступает на счетный вход счетного триггера и на счетный вход счетчика результата. В этом случае на нулевом выходе счетного триггера установится нулевой потенциал, а на единичном выходе - управляющий потенциал. При этом меняется направление счета в счетчике делителя и буферном счетчике. С этого момента счетчик делителя начинает работать на сложение, а буферный счетчик - на вычитание- После окончания первого цикла вычитания кода делителя Б из кода делимого А в буферном счетчике будет установлен код числа Б.

Во втором цикле вычитания из кода числа Б в буферном счетчике начинают вычитаться счетные импульсы. Когда код в буферном счетчике станет равным нулю О (окончился второй цикл вычитания кода делителя Б из кода делимого А), срабатывает многовходовая схема И. Сигнал схемы И через схему ИЛИ поступает на счетный вход счетного триггера и на счетный вход счетчика результата. При этом счетный триггер переключается и изменяет направление счета в счетчике делителя и в буферном счетчике. В третьем цикле вычитания счетчик делителя работает на вычитание, а буферный счетчик - на сложение. Последовательность таких циклов вычитания будет продолжаться до тех пор, пока код числа А в счетчике делимого станет равным О. В этот момент срабатывает многовходовая схема И и выдает управляющий сигнал на второй нулевой вход триггера. На единичном выходе триггера вырабатывается нулевой потенциал, который запрещал прохождение счетных импульсов через схему И.

В счетчике результата будет находиться код числа С, равный числу циклов деления.

Затем цифровое отношение, хранящееся в счетчике результата, преобразуется в длительность интервала обратного преобразования. По сигналу, поступающему с выхода 53 блока управления 20, код числа С, хранящийся в счетчике результата , переписывается через блок И в реверсивный счетчик. Этим же сигналом в нулевое состояние устанавливаются счетный триггер и реверсивные счетчики. Нулевой сигнал с единичного 1 выхода счетного триггера выдает запрещающий потенциал на вход реверса реверсивного счетчика, который работает на вычитание. Управляющий потенциал с нулевого О выхода счетного триггера выдает разрешающий потенциал на вход реверса реверсивного счетчика, который работает на сложение.

При поступлении счетных импульсов на вход 55 формирователя 14 они будут вычитаться из числа С, находящегося в реверсив- ном счетчике, и суммироваться в реверсивном счетчике.

В момент, когда число в реверсивном счетчике станет равным нулю О, срабатывает схема И. Сигнал схемы И через схему ИЛИ поступает на счетный вход триггера. Триггер изменяет свое состояние. Во втором цикле вычитания реверсивный счетчик будет работать на сложение, а реверсивный счетчик - на вычитание. Когда число в реверсивном счетчике станет равным нулю О, сработает схема И. Сигнал схемы И через схему ИЛИ поступает на счетный вход триггера и изменяет его состояние. В третий цикл реверсивный счетчик будет работать на вычитание, а другой реверсивный счетчик - на сложение и т.д.

С изменением частоты входного сигнала синхронно будет изменяться длительность интервала между.выборками восстановления таким образом, что

m A ti.n2 A ta const,

где гн, - число выборок при частотах входного сигнала f 1 и Ь;

A ti, A 12 - длительность интервала между выборками обратного преобразования, т.е. при этом восстановление входного .сигнала будет происходить на фиксированной частоте FO.

Блок 15 - регистр, является типовым устройством. Может использоваться 564

тмз.

Запись числа в регистр производится без предварительной установки разрядов в нулевое состояние.

Блок 16 - цифроаналоговый преобрэзователь, является типовым преобразователем кодовой величины в аналоговую. Может использоваться цифроаналоговый преобразователь 572 ПВ с компаратором 521 САЗ. Блок 17 - полупроводниковый преобразователь среднеквадратических значений, является типовым устройством.

Блок 18 - усилитель, является стандартным делителем.

Б/Ток 19 - регистрирующее устройство,

является типовым устройством.

Блок 20 - блок управления. Блок управления 20 формирует управляющие сигналы, синхронизирующие работу всего устройства.

Временные диаграммы работы блока управления приведены на фиг. 2, На основании временных диаграмм может быть по законам формальной логики синтезирован блок управления.

Блокуправленил 20 состоит из счетчика, включающего триггеры, и дешифратора, включающего генератор импульсов, делитель, схемы И, формирователи (формирователи длительности), устройства задержки,

триггер схемы И, формирователь (формирователь длительности), устройства задержки.

В данном устройстве производится измерение напряжения постоянного тока, выделенное преобразователем среднеквадратических

значений, на который поступает периодический сигнал на фиксированной частоте после изменениячастотного спектра входного сигнала. Изменение частотного спектра входного сигнала достигается его двойным преобразованием. Сначала входной аналоговый сигнала, изменяющийся в широком частотном диапазоне, преобразуется в цифровой код выборок, которые запоминаются в оперативной памяти. Затем по значению кода выборок восстанавливается аналоговый входной сигнал на фиксированной частоте РОИ поступает на преобразователь среднеквадратических значений.

Работа устройства происходит следующим образом. Переменный сигнал Ux после усилителя 1 поступает на схему перехода через ноль 2 и измерительный вход аналого- цифрового преобразователя 4. По выходным сигналам схемы перехо да через поле 2

блок управления 20 формирует управляющие сигналы, синхронизирующие работу всего устройства.

Временные положения сигналов блока управления 20-показзны на фиг. 2.

Блок управления 20 вырабатывает сигналы запуска аналого-цифрового преобразователя А, которые с выхода 44 блока управления 20 поступают из запуск аналого-цифрового преобразователя 4 зз один полупериод входного сигнала U.

Информация, преобразованная анало- ro-цифровым преобразователем 4 (цифровые значения выборок), поступает поочередно на запоминающие устройства 7, 8. Разделение этой информации производится блоком управления 20.

Управляющий сигнал с выхода 36 блока управления 20 разрешает/прохождение кодовой информации с выхода аналого-цифрового преобразователя 4 через блок И 5 на информационный вход запоминающего ус-, тройства 7. На запоминающее устройство 8 кодовая информация с выхода АЦП 4 не поступает, поскольку на блок И 6 поступает запрещающий потенциал с выхода 41 блока управления 20.

На адресный вход первого запоминаю- щего устройства 7 в это время поступает код адреса со счетчика 3, который формирует адрес записи, подсчитывая .сигналы запуска аналого-цифрового преобразователя 4. Код адреса записи, сформированный счетчиком 3, через блок И-ИЛИ 10 поступает на адресный вход запоминающего устройства 7. За- пись информации в запоминающее устройство 7 производится по сигналу, поступающему с 37 выхода блока управления 20,

В это же время с запоминающего устройства 8 считывается информация, поступившая в него в предыдущем такте. Формирователь адреса считывания 12 из адреса записи, сформированного счетчиком адреса 3, вырабатывает адрес для непрерывного считывания информации с запоминающего устройства 8, необходимого для восстановления переменного входного сигнала. Адрес считывания, сформированный формирователем здреса считывания 12, через блок И-ИЛИ. 11 поступает на адресный вход запоминающего устройства 8. По сигналу считывания, поступающему с 51 выхода блока управления 20, информация с запоминающего устройства 8 через блох И- 9 поступает на информационный вход регистра 15. Запись информации в регистр 15 производится управляющим сигналом, поступающим с 49 выхода блока управления 20. После восстановления переменного сходного сигнала цифроаналоговым преобразователем 16 производится преобразова- .. ние этого сигнала в напряжение постоянного тока преобразователем сред- неквадратичоских значений 17, усиление

усилителем 18 и индикация результата измерения регистрирующим устройством 19. Во втором цикле измерения полупериода входного сигнала информация запоминается в устройстве 8, а считывание информации производится с запоминающего устройства 7. В этом случае кодовая информация с выхода аналого-цифрового преобразователя 4 через блок И 6 поступает

на информационный вход запоминающего устройства 8, поскольку на второй вход бло ка 46 поступает сигнал с выхода 41 блока управления 20. Код адреса, сформированный счетчиком адреса 3, через блок И-ИЛИ

11 поступает на адресный вход запоминающего устройства -8. Запись информации в запоминающее устройство 8 производится по сигналу, поступающему с выхода 50 блока управления 20.

В это же время с запоминающего устройства 7 считывается информация, поступившая в него в предыдущий такт. Адрес считывания, сформированный формирователем адреса считывания 12 через блок ИИЛИ 10, поступает на адресный вход запоминающего устройства 7. По сигналу считывания, поступающему с 38 выхода блока управления 20, информация с запоминающего устройства 7 через блок И-ИЛИ 9

поступает на информационный вход регистра 15.

Формирование сигналов считывания производится при помощи счетчика выборок 13 и формирователя интервала обратного преобразователя 14. Счетчик выборок 13 после установления его в нулевое состояние сигналом, поступающим с выхода 34 блока управления 20, подсчитывает число импульсов запуска аналого-цифрового преобразователя 4 за период входного сигнала. Формирователь интервала обратного преобразования 14 вырабатывает сигналы с переменным интервалом между ними, чтобы . восстановление входного сигнала пррисходило на фиксированной частоте, т.е. чтобы выдерживалось равенство щ At2 const, где m, па - число выборок записи за один период входного сигнала; Д ti, A 12 - интервал между сигналами считывания.

Для этого формирователем интервала обратного преобразования 14 производится определение отношения кодового значения периода То фиксированной частоты к числу выборки за один полупериод входного сигнала, подсчитанного счетчиком выборок 13, и преобразование полученного результата в последовательность сигналов, длительность интервалов между которыми зависит

от числа выборок DI за полупериод входного сигнала.

Сигналы считывания с формирователя интервалов обратного преобразования 14 поступают на 52 вход блока управления 20, который вырабатывает управляющие сигналы, необходимые для последовательного поочередного считывания с запоминающих устройств 7, 8, хранящейся в них информации.

Заявляемый объект обладает техническими преимуществами по сравнению с .прототипом; отсутствием дополнительной частотной погрешности, равной 1-2%. Это обусловлено тем, что в предложенном способе за счет изменения спектра входного сиг- .нала. изменяющегося в широком частотном диапазоне, в результате двойного преобразования, на измерение поступает сигнал на фиксированной частоте. Поэтому напряжение постоянного тока, пропорциональное среднеквадрати- ческому значению периодического сигнала, независимо от его частоты будет пропорционально среднеквадратическому значению периодического сигнала фиксированной частоты. .

В институте, электродинамики АН УССР изготовлен макет вольтметра переменного напряжения, реализующего предлагаемый способ измерения среднеквадратических значений переменных сигналов.

0

Формула изобретения Способ измерения -среднеквэдратиче- ских значений переменных сигналов, основанный на том, что периодический сигнал преобразуют в напряжение постоянного тока, пропорциональное среднеквадратическому значению измеряемого сигнала, и измеряют напряжение постоянного тока, отличающийся тем, что, с целью повышения точности измерения, предварительно выделяют интервал измерения, равный периоду измеряемого сигнала, на выделенном интервале измерения производят выборки мгновенных значений измеряе5 мого сигнала через равные промежутки времени A to. производят аналого-цифровое преобразование каждой выборки, результаты аналого-цифрового преобразования запоминают, подсчитывают число выборок ги на шн0 тервале измерения, определяют значение фиксированного периода частоты восстановления , равного То-no A to, где п0-мини-, мальное число выборок мгновенных значений измеряемого сигнала за период частоты вое5 становления, достаточное для аналого-цифрового преобразования, определяют переменный интервал восстановления A ti T o/ni, через который производят обратное цифроаналоговое преобразование запомненных цифровых значений выборок измеряемого сигнала в периодический сигнал фиксированной частоты.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| Измеритель глубины модуляции | 1989 |

|

SU1737370A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Способ интегрального преобразования релаксационных сигналов и устройство для его осуществления | 1986 |

|

SU1695324A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР КАЧЕСТВА ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1993 |

|

RU2096788C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Использование: изобретение относится к электрическим измерениям и может быть использовано при построении высокоточных измерительных приборов. Сущность изобретения: способ измерения средне- квадратических значений переменных сигналов, основанный на изменении спектра входного сигнала, в результате чего преобразование сигнала в напряжение постоянного тока,пропорциональное среднеквадратическому значению периодического сигнала, производится на фиксированной частоте, что позволяет повысить точность измерения за счет устранения частотной составляющей погрешности. 2 ил.

| Шрамков Е.Г | |||

| Электрические измерения | |||

| М.: Высшая школа, 1972, с | |||

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Там же, с | |||

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

Авторы

Даты

1993-02-28—Публикация

1990-11-16—Подача